PCI Express总线架构和总线层次结构浅析

描述

作者:romme

1、PCI Express总线架构

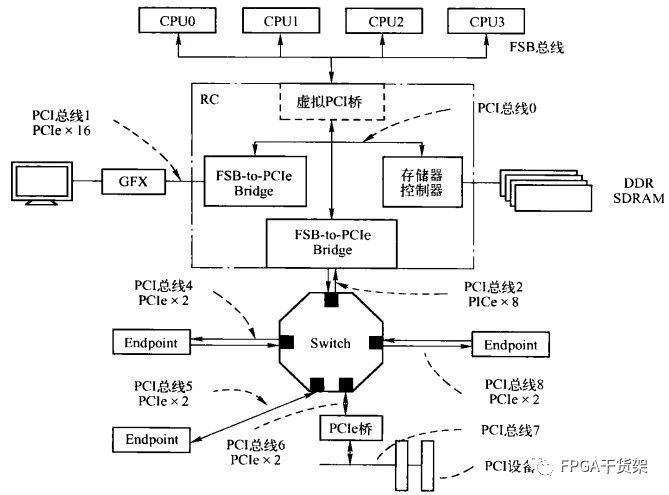

如果将计算机比作人的话,CPU就是人的大脑,而PCIe就是人的神经中枢,负责内部数据信息的传输。下图是PCIe总线结构。

处理器系统首先使用一个虚拟的PCI桥分离处理器系统的存储器域与PCI总线域。FSB总线下的所有外部设备都属于PCI总线域。

RC由两个FSB-to-PCIe桥和存储器控制器组成。这两个FSB-to-PCIe桥分别推出一个x16和x8的PCIe链路,其中x16的PCIe链路连接显卡控制器(GFX),x8的PCIe链路连接一个Switch进行PCIe链路扩展,而存储器控制器连接DDR插槽或颗粒。

PCIe总线使用端到端的连接方式,因此只有Switch才能对PCIe链路进行扩展,而每扩展一条PCIe链路将产生一个新的PCI总线号。

Switch可以将1个x8的PCIe端口扩展为4个x2的PCIe端口,其中每个PCIe端口都可以挂接EP。除此之外,PCIe总线还可以使用PCIe桥,将PCIe总线转换为PCI总线或PCI-X总线,之后挂接PCI或PCI-X设备。

2、PCI Express总线层次结构

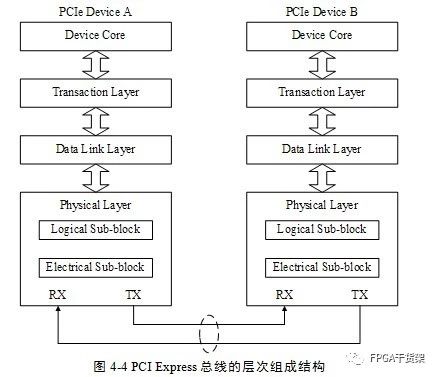

PCIE总线采用串行连接方式,并使用数据包(Packet)进行数据传输,且需要通过多个层次,包括事务层、数据链路层和物理层。PCIe总线的层次结构如下图所示。

(1)事务层

事务层定义了PCIE总线使用总线事务,其中多数总线事务与PCI总线兼容。这些总线事务可以通过Switch等设备传送到其他PCIE设备或者RC。RC也可以使用这些总线事务访问PCIE设备。事务层接收来自PCIE设备核心层的数据,并将其封装为TLP(Transaction Layer Packet)后,发向数据链路层。此外事务层还可以从数据链路层中接收数据报文,然后转发至PCIE设备的核心层。

(2)数据链路层

数据链路层保证来自发送端事务层的报文可以可靠、完整地发送到接收端的数据链路层。来自事务层的报文在通过数据链路层时,将被添加Sequence Number前缀和CRC后缀。数据链路层使用ACK/NAK协议保证报文的可靠传递。

(3)物理层

物理层是PCIE总线最底层,将PCIE设备连接在一起。PCIE总线的物理层为PCIE设备间的数据通信提供传送介质,并管理链路状态。

编辑:hfy

-

PCIE总线2016-03-02 0

-

基于FPGA的PCI Express总线接口应用2019-05-21 0

-

如何去设计一种PCI Express接口?2021-05-21 0

-

基于PCI Express总线高速数据采集卡的设计与实现2010-09-22 685

-

pci express总线概念2006-12-25 1646

-

仪器控制总线比较(GPIB、USB、PCI、PCI Expr2009-02-26 8760

-

PCI Express插槽,什么是PCI Express插槽2009-04-26 4943

-

PCI Express总线技术白皮书2009-10-04 1042

-

基于Virtex5的PCI-Express总线接口设计2009-10-05 918

-

PCI Express总线2010-01-22 631

-

FPGA在PCI Express总线接口中的应用2011-10-17 1042

-

PCI与PCI-Express总线v1.22017-04-19 1058

-

PCI-Express总线介绍 接口设计和实现2018-04-11 6974

-

一文看懂PCI总线与PXI总线有什么区别2018-05-24 14111

-

PCI-Express总线接口的布线规则2023-11-29 660

全部0条评论

快来发表一下你的评论吧 !