PCB设计中介电损耗角正切高速设计作用

描述

当今的高速PCB设计具有两个因素:移动大量数据和信号带宽,频率范围高达非常高的频率。结果,有几件事会影响这两个因素。在“如果您做得不好,您将死在水里”列表顶部的那些元素中,损失很小。在设计过程中有很多事情会影响损耗,但是要做出的基本决定是所选层压板的介电损耗正切值。简而言之,介电损耗正切将限制PCB上传输线的有效长度,因为它会导致信号电平在传播过程中降低。

本文将介绍介电损耗角正切,它在高速设计中的作用,它如何取决于玻璃与树脂的比率和频率,如何测量它以及对当今产品的影响。对于以32 Gbps速度运行的电路板,我们将研究为什么构建测试板对于合格损耗正切的必要性。

介电损耗角正切有时称为耗散因数,其符号为Df。在传输线的设计和RF设计中,电介质损耗角正切与黄褐色(定义δ ),这是在其中由电磁场(RF)通过电介质行进携带的能量由电介质吸收的速率的量度。当一种材料被称为“高速”时,它就是Df值。需要牢记的一些要点包括:

在PCB和微波组件使用的频率下,电介质吸收的能量通常随频率增加,直到进入高GHz范围。

损耗随频率增大,这是因为不断变化的电磁场导致电介质中的分子振动。它们振动得越快,损失就越大(下文对此进行了更多介绍)。

材料的损耗角正切值越低,功率损耗就越低。

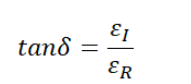

就材料的介电常数而言,任何材料的介电损耗角正切都有一个简单的方程:

如果知道介电常数的虚部和实部,则可以计算损耗角正切。如果查看PCB层压板数据表,通常会看到介电损耗正切值和Dk值。只需将它们相乘即可得到介电常数的虚部。

都是分子的

PCB中使用的频率下电介质的损耗是由于分子由相反的电荷形成而形成,该电荷可以相互吸引和排斥。如果分子中的原子由于电场而移离平衡状态,则它可以开始振荡。所有材料都将具有一定的损耗角正切,即使在大多数PCB使用的频率下损耗很小。

例如,考虑具有极性和非对称结构的水。有一个氧原子和两个氢原子形成V形,其中氧原子为负端,氢原子为正端。当水分子经受变化的电场时,它会振动。请注意,分子动能与温度直接相关,因此,传播场引起的分子振动会导致基板中的温度升高。这就是为什么微波炉可以工作的原因。食物中的水由于电场的振动而达到高温。由于在极性分子的不同区域中更大的电荷分离,所以分子与非极性分子相比可以具有更高的介电损耗角正切。

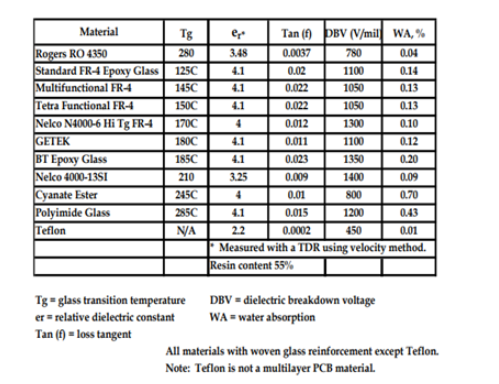

表1中的信息表明,用于制造多层PCB的大多数材料具有相对较高的损耗。(要归类为低损耗,损耗角正切应低于.004。)

表1.某些常见层压系统的特性

PCB设计人员面临的挑战是确定一种材料何时损耗太大,必须用损耗更低的替代品来代替。由于损耗是频率和传输线长度的函数,因此没有简单的规则可用来确定何时必须进行切换。

介电损耗角正切,频率和玻璃与树脂的比率

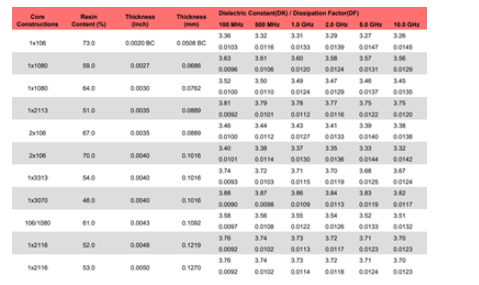

给定的PCB层压板由树脂体系和玻璃纤维增强布制成,每一种都有不同的损耗角正切值。因此,由于使用不同比例的玻璃和树脂来制作具有各种厚度的PCB层压板,因此总损耗角正切值将有所变化。当信号完整性工程师仅获得一组层压板的单个损耗角正切值时(例如Panasonic及其Megtron 6材料系统),这就会给信号完整性工程师带来问题。表2显示损耗角正切如何随频率和玻璃与树脂的比率变化。这是Isola Corporation的FR408HR核心材料的数据。

该表包含一个特性良好的PCB层压板系统的示例。可以看出,介电损耗角正切随频率增加的幅度大于其随玻璃与树脂之比变化的幅度。这是因为,在该体系中,树脂体系和玻璃的损耗角正切非常接近。在其他树脂体系中,这可能有所不同。

测量数字层压板的介电损耗正切

本文末尾的参考文献2显示,IPC记录了23种不同的方法来测量层压板中的介电损耗角正切。这些方法中的每一种都是针对特定应用开发的。由于首先需要低损耗层压板的应用是微波和RF,因此大多数测试方法已针对特定类型的电路(如相控阵雷达)进行了优化。与超高速数字电路的需求相比,这些应用可被视为“窄带”。

这些方法中只有一种方法以可用于数字多层PCB设计的方式表征层压板。已证明与带状线传输线构造的PCB上进行的实际测试具有最佳关联。所有其他方法都使用谐振腔或其他类型的测量单元,这些单元在狭窄的频率范围内表征层压板,并且它们都有一些误差。

介电损耗正切数据不完整时该怎么办?

典型的层压板数据表没有包含足够的有关介电损耗的信息,因此无法对高速数字数据路径中的潜在损耗进行正确的建模和分析。那么,如何才能确保设计在最终构建时能够按规格工作?工程师在开发使用最新高速数据链路的产品时,都会出现这个问题。由于需要精确地考虑铜走线的损耗,这可能会更加复杂,铜走线的损耗受走线的总表面积以及铜表面粗糙度的影响。

即使准确知道损耗角正切,也没有可靠的方法可以对所有这些效应进行建模。因此,产品开发人员别无选择,只能用实际的传输线构造测试PCB。将其用于最终产品并进行测试以确定所考虑的层压板的损耗与频率的关系,并查看是否可以达到目标。这是为高性能系统构建设计规则集的唯一安全方法。图1是两套实际测试PCB的照片,几年前我们使用它们来验证超级计算机中的路径为5.2 Gb / S和TB路由器中的路径为4.8 Gb / S。这些测试PCB的设计使其在插入在一起时将创建子板/背板接口,以及从背板和子板到外界的接口。

图2. 5.2 Gb / S和4.8 Gb / S数据路径的测试PCB集

那么,如何为当今的32 Gb / S和56 Gb / S数据路径进行设计呢?

当您设计具有32 Gb / S或56 Gb / S数据路径的产品时,您必须构建测试板以确保产品能够按设计工作,这可能不足为奇。Speeding Edge的创始人兼总裁Lee Ritchey指出:“一旦进入这些数据路径,损耗正切就变得更加令人担忧。您可以构建类似于上述内容的测试板。您只需测量更远的频率即可。这些数据速率支配着产品的性能,它们决定了板上的路径长度。等式非常简单,路径越长,损失就越大。”

32 Gb / S和56 Gb / S的速度下,您将超越极限。” 相比之下,光纤通道的损耗要少两个或三个数量级。当大型机器(例如用于扫描半导体的机器)之间存在盒对盒连接或截面到截面空间时,在很多地方都必须使用光纤。这是痛苦的昂贵,因为在路径的每一端都必须有一个收发器,每个收发器的价格为50美元。因此,激励措施是留在铜中。在10 Gb / S服务器场中,我们对收发器进行了改进,以使我们可以通过100英尺长的6类电缆进行10 Gb / S的传输。但是,从10 Gb / S提升到56 Gb / S是一个巨大的飞跃。真正好的收发器只能处理大约30英寸。”

编辑:hfy

-

深度分析电容器损耗角2011-11-17 0

-

高速pcb设计指南。2012-07-13 0

-

高速PCB设计之一 何为高速PCB设计2014-10-21 0

-

高速PCB设计指南2008-08-04 912

-

高速PCB设计的叠层问题2009-05-16 610

-

电容在高速PCB设计中的应用2009-08-16 524

-

Cadence高速PCB设计2011-11-21 1565

-

高速PCB设计误区与对策2011-11-23 563

-

高速PCB设计指南之一2016-05-09 537

-

高速PCB设计指南二2016-05-09 695

-

高速PCB设计电容的应用2017-01-28 932

-

介质损耗角正切值的测量方法2021-09-26 6820

-

高速PCB设计指南之七.zip2022-12-30 168

-

高速PCB设计指南之六.zip2022-12-30 194

-

高速PCB设计的叠层问题.zip2022-12-30 284

全部0条评论

快来发表一下你的评论吧 !