基于ZCU106单板的功耗优化

电子说

1.2w人已加入

描述

作者:付汉杰,hankf@xilinx.com,文章转载自:博客园

不同使用场景,对芯片的性能和功耗要求不一样。为了测试Xilinx MPSoC PS侧的最低功耗,基于ZCU106单板做了功耗优化。为了方便,使用最简单的软硬件环境。软件使用死循环做串口打印,硬件保留了如下模块。

A. A53 0

B. QSPI flash Dual Parallel

C. I2C 0/1

D. PMU

E. UART 0

F. GPIO MIO

G. SWDT 0/1

H. TTC 0/1/2/3

I. DDR 16-bit

J. DPLL/RPLL

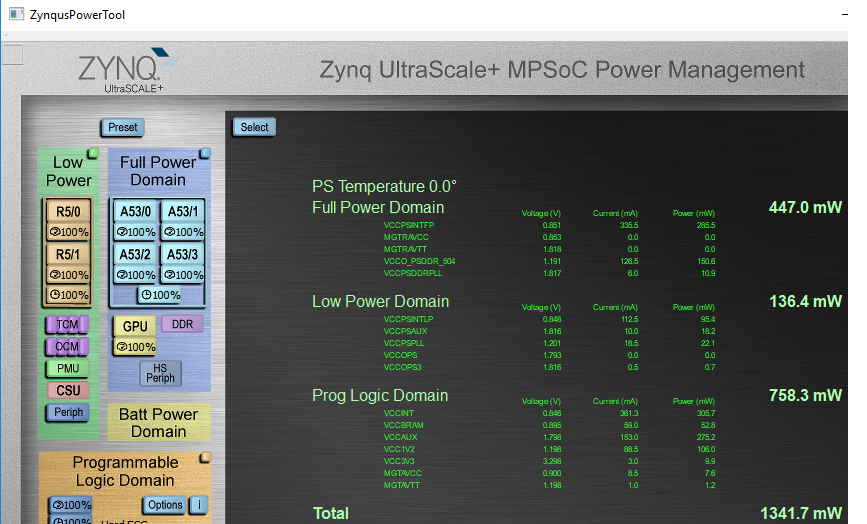

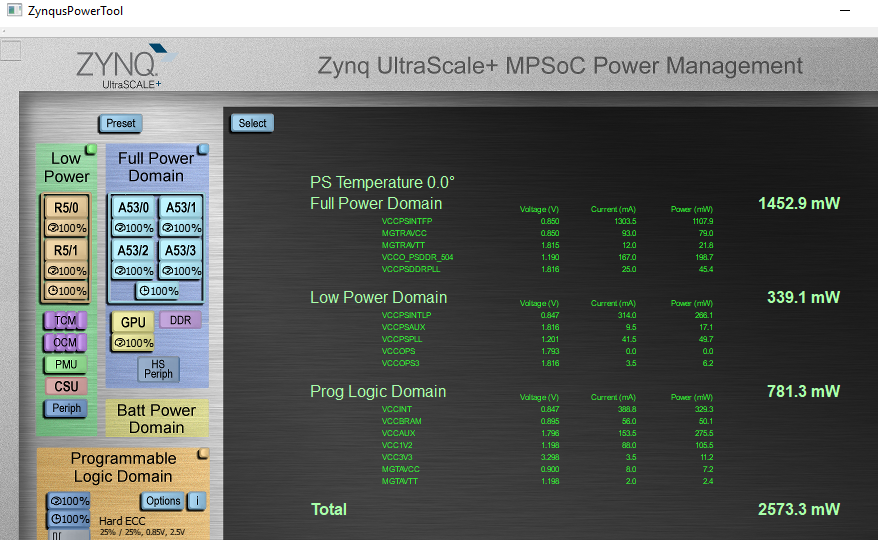

在关闭其他外设,尽可能降低各个模块的频率后,FPD功耗是447mw,LPD是136mw。作为对比,Vivado使用ZCU106单板建立工程,使用默认设置,FPD功耗是1452mw,LPD是339mw。可以看到,新设计节省了相当大的功耗。当然,具体的产品使用场景,可能有性能和功能要求。能达到什么效果,还需要根据产品要求再做评估。

优化后的功耗

优化前的功耗

责任编辑:xj

原文标题:【资深工程师分享】ZCU106 MPSoC 功耗优化

文章出处:【微信公众号:FPGA开发圈】欢迎添加关注!文章转载请注明出处。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

ZCU102,ZCU104和ZCU106有什么区别?2019-10-22 0

-

ZCU106 评估套件产品描述2019-07-31 5634

-

ZCU106开发板的用户指南免费下载2020-09-18 1586

-

Xilinx提供在ZCU106单板上可以验证的超低延时编解码方案2021-04-30 2687

-

在ZCU106单板上验证Xilinx超低延时编解码方案2021-05-07 6293

-

如何在zcu106之间运行1588?2021-05-13 3359

-

在MPSoC ZCU106单板的HDMI-Tx上基于eglfs_kms的运行QT应用程序2022-08-02 2516

-

ZCU106在PLDDR实现超低延时编码2022-08-02 565

-

ZCU106的超低延时gstreamer编解码命令2022-08-02 996

-

在ZCU106开发板上的仅限TX的设计内实现UHD-SDITX子系统2023-07-10 659

全部0条评论

快来发表一下你的评论吧 !