USB端口加ESD元件时的设计细节

电子说

1.2w人已加入

描述

USB端口加ESD元件时的设计细节

今天的线路如下图。

该USB口可以支持Device/Host模式,

1)当为device时 U50(SY6281)不使能;U50(SY6281)关断,VCC_5V_USB2电压为0V

2)当为host时U50(SY6281)不使能;U50(SY6281)关断,VCC_5V_USB2电压为5V

到这里,这个设计是完美的。

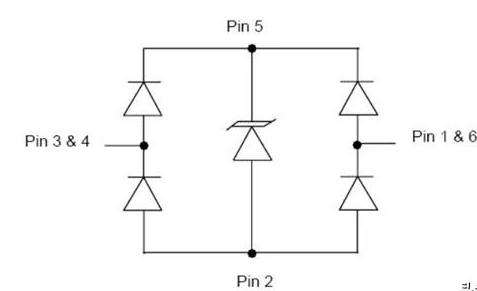

然而,问题在于TVS (D8)元件的使用,我们先看下TVS内部是什么样子的。

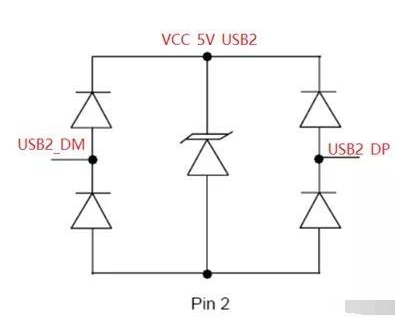

然后结合原理图你会发现连接关系如下图所示。

当VCC_5V_USB2一直为高电平时,TVS上的Diode是不会导通的。没有任何问题,然而,当VCC_5V_USB2变为0V时,因为此时TVS上的Diode导通,从而导致USB的D+上的高电平(当USB为high speed 模式或者是full speed模式时,D+会有上拉,一般为3.3V)被钳位到0.6V左右的低电平。这样就有可能会导致SOC对USB口识别错误。

责任编辑人:CC

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

USB接口的ESD保护器件要求2008-07-22 0

-

保护元件免受ESD的方法2013-01-04 0

-

USB2.0数据接口ESD保护2013-12-27 0

-

USB Type-C™:您的 ESD 解决方案是否保护端口?2017-01-04 0

-

USB端口ESD和EOS防护介绍及方案2018-11-21 0

-

针对USB端口的ESD保护2019-08-02 0

-

ESD保护元件介绍2020-03-19 0

-

USB端口ESD器件SRV05-42020-10-14 0

-

USB 3.0端口的ESD保护方案2010-03-04 1439

-

USB 2.0高速端口的ESD保护设计方案2010-04-12 12681

-

USB Type-C™:您的ESD解决方案是否保护端口2021-11-10 862

-

USB Type-C™:您的ESD解决方案是否保护端口?2022-11-02 259

-

ESD静电二极管能否应用于USB端口?2023-07-18 771

全部0条评论

快来发表一下你的评论吧 !