PFC控制器的架构、功能特点及应用分析

模拟技术

描述

作者:Vinit Jayar,Victor Khasiev

PFC控制器的架构

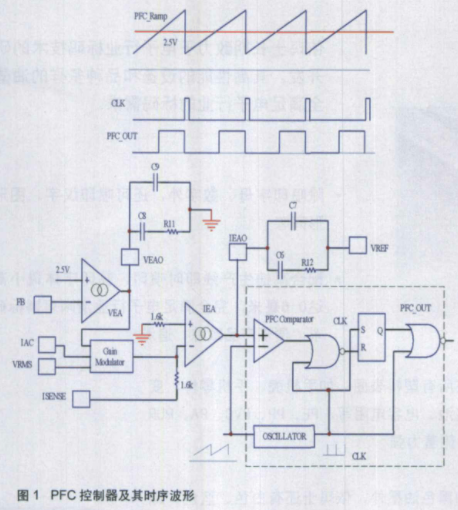

尽管有许多公司在生产不同类型的PFC (Power Factor Correction,PFC)控制器,这些芯片的架构和结构却极为类似。大多数PFC控制器都采用增益调制器、电流误差放大器 (IEA)、PFC比较器、电压误差放大器 (VEA) 和PFC脉冲输出驱动器。图1是PFC控制器的模块示意图。

内环是电流控制回路,包含了增益调制器、IEA和PFC比较器。外环控制回路是电压控制回路,利用VEA作为误差放大器。VEA输出 (VEAO) 也是增益调制器的输入之一。内环电流控制回路修整来自交流线路的线电流,并与交流线电压成正比。外环电压回路调节PFC直流总线电压,使之保持在大约385V左右。需注意的是,与电压控制回路相比,电流控制回路的带宽要大得多。

PFC控制器的PFC比较器 驱动器部分在图1中以虚线标注,其设计围绕PFC比较器。振荡器产生锯齿波形及与该锯齿波形下降边缘同步的时钟 (CLK) 信号。图1所见的锯齿波形被称为“PFC_RAMP”信号,也即RAMP1。

如图1所示,在周期开始处,CLK信号为高时,PFC_OUT为低。一旦PFC_RAMP超过电流误差放大器的输出 (IEAO) 值,PFC_OUT就变高,最终接通外部PFC开关管。PFC_OUT一直保持高电平直到周期结束,CLK会将它设为低电平。因此,PFC能实现尖端的调节功能。

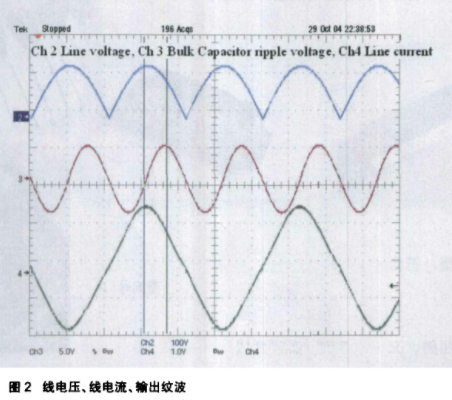

通常,PFC芯片能确保PFC的负载周期D和PFC_OUT脉冲不会达到100%。防止了升压电感器达致饱和。最大的负载周期会在AC线电压的过零点处出现 (如图2所示的Ch2)。

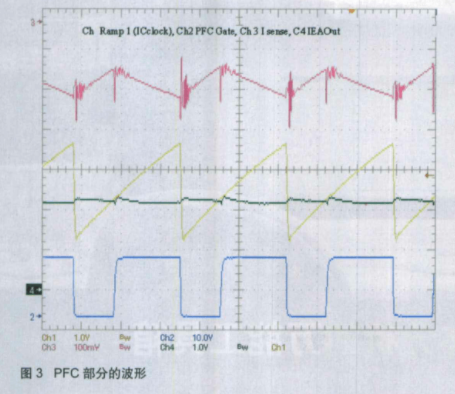

因此,当Vin为零时,控制器芯片限制负载周期为98%。例如,图3所示是飞兆半导体的PFC控制器FAN4810的实际波形。这里Ch4是电流误差放大器的输出。

对设计人员而言,设置正确的电流误差放大器输出值是非常重要的。例如,FAN4810规格定义RAMP1谷对峰电压为2.5V。这意味着通过调节,IEAO电压的动态范围应该在RAMP1信号摆幅内,如图3所示的线迹Ch1和Ch4。

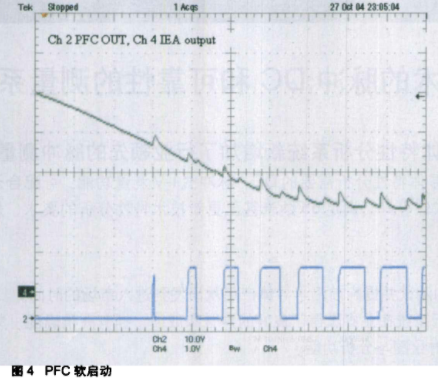

在许多IC中,IEA是跨导放大器 (transconductance amplifier)。图1所示为围绕该放大器的2类补偿电路。该补偿电路与参考电压引脚VREF连接,建立了PFC的软启动功能。当启动时,IEAO上升到参考电压水平;随着回路进行调节,IEAO从VREF水平下降到工作水平。这保证了PFC的负载周期从0% 逐渐增加到回路所需要的数值,从而提供了软启动功能,如图4所示。

增益调制器的功能

PFC控制器的中部心分是增益调制器和电压误差放大器,如图1所示。该增益调制器会生成控制信号给电流控制回路,让后者对这个输入电流进行修整。FAN4810 PFC控制器的电流控制回路确保电流传感器的负反馈电压被内部Rcp电阻上的正电压所平衡。这一正电压由流经Rcp的增益调制器输出电流所生成。因此,所产生的线电流 (I_line) 和 ISENSE 引脚上的电压被迫重复增益调制器输出波形的形状。换言之,这个情况:

I_line R_{s}=I_{GM} R_{cp} (1)

会常常出现。这里,Rs代表线电感电阻 (line current sense resistor),而IGM是增益调制器的输出电流。

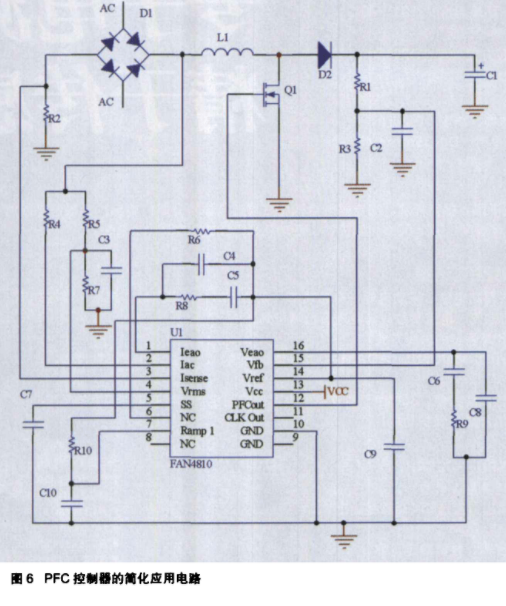

为了修整产生的线电流,增益调制器采用三个输入:IAC、VRMS 和VEA输出。引脚IAC通过1M 电阻与AC线整流桥的输出相连接 (见图6中的R4)。IAC为两倍线频率全波整流正弦波,与瞬态AC线电压成正比。IAC实际上修整了增益调制器输出电流,该电流由下式的正弦曲线描述:

I_{GM}=\frac{I_{VC} V_{RAO}}{V_{RMS}^{2}} (2)

在VRMS引脚的电压是与AC线电压RMS值成正比的DC电压,如图6所示。IGM 的设计与VRMS平方成反比。

为什么增益调制器的输出电流必须与AC线电压RMS 值的平方成反比呢?假设VEAO恒定不变,如果输入线电压加倍,为提供相同的功率,那么输入电流及IGM就应相应减小一半。由式 (2) 可知,若线电压加倍,IAC也会加倍。因此要抵消IAC 的增大,VRMS信号便应增加4倍。

VEA带宽和THD

增益调制器的第三个输入是VEA输出,会决定增益调制器输出电流的幅值。VEA的输入与监测PFC输出电压的分压器相连接 (图6)。在FAN4810的例子中,FB引脚在额定总线电压 (nominal bus voltage) 时被设置为2.5V。VEA是带类2补偿电路的跨导放大器,如图1所示。要关闭VEA的反馈回路,有两个相互矛盾的要求:1) 回路应具有足够低的带宽来缓减DC总线上的120Hz 纹波电压,从而减小输入线电流的总谐波失真 (Total Harmonic Distortion,THD);2) 回路必须足够快的负载瞬态响应。

THD是设计人员考虑的重要因素。由于输出电容的移相特性,大容量电容的电压纹波相位与线电压相比时 (见图3中的Ch 3) 位移了90度。因此与位移的电压纹波成正比的信号直接输入到VEA,放大器的增益和带宽应该受到限制。通常,电压控制回路分频频率设置在10 ~30Hz之间。

增益调制器有两个有趣的特性很少被提及。首先,转移特性提供了自然的电压过低保护 (brown out protection)。增益调制器的最大增益被设计在最小线电压处。若输入电压恰巧低于规定的最小值 (电力减弱情况),那么增益和PFC负载周期都会急剧下降,因而降低总线电压。第二个有趣的特性是内置过电流保护功能。增益调制器的最大输出电压会被限制,在FAN4810中为0.8V。如果因为任何原因,例如由于过载,ISENSE 引脚上的电压下降到低于 0.8V,IEA的反相输入对地负值将会更大。因此,IEAO水平将增加,这会降低PFC负载周期和总线电压,从而限制输出功率 (见图1)。

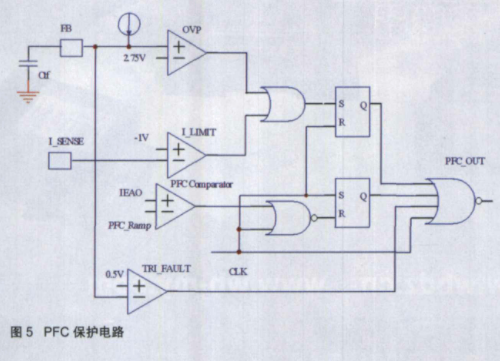

PFC保护电路

如同其他控制器一样,FAN4810包括了大量与PFC工作相关的保护电路。其中有过电压保护 (Over-Voltage Protection,OVP) 和过电流保护 (Over-Current Protection,OCP) (见图5)。利用由PFC OVP或电流限值设置的SR触发来终止PFC输出脉冲。所以,OVP和OCP故障会在每一个周期中被监测及闩锁。

飞兆半导体器件具有“三重故障 (Tri-Fault)”保护功能。这种保护可覆盖以下故障:(a) FB引脚对地短路,(b) 从PFC DC总线分压器到芯片的VFB引脚的连线 (引线或PCB走线) 断裂,(c) 分压器的顶端或底部电阻开路 (图6中的电阻R1、R2)。如果FB对地短路 (情况(a)),PFC_FB引脚上的电压将低于0.5V,Tri-Fault 比较器输出将停顿PFC OUT脉冲。在引线断裂(情况(b)) ,内部电流源开始对电容Ctf充电。于是,一旦FB引脚上的电压超过2.75V,OVP比较器将终止PFC输出。电容Ctf (图6中的C2) 是可选的选项,定义时间t_F 来触发保护电路。

t_F=\frac{Ctf 2.75V}{200nA}

对于 (c) 的故障情况,OVP或TRI_FAULT将终止PFC_OUT脉冲。如果因任何原因DC总线电压超过额定水平的10%,OVP保护开始起作用。例如,若额定总线电压为385VDC (FB引脚为2.5V),只要总线电压超过423VDC (FB引脚为2.75V),OVP就会被触发。

小结

PFC控制器集成了诸如过电压保护 (OVP)、过电流保护 (OCP) 及FAN4810示例中的三重故障 (TriFault) 保护等功能,在AC/DC设计中起着重要的作用。带有有源PFC及接近统一功率因子的转换器能满足ICE61000-3-2 规范的要求,减少了电源设计者的一个主要顾虑。

责任编辑:gt

-

数字PFC控制:实现电机控制系统监控的增值2018-10-16 0

-

搭载PFC控制器的AC/DC转换器IC2018-11-21 0

-

FAN4800A PFC和PWM组合控制器应用2019-06-13 0

-

FAN4800C PFC和PWM组合控制器应用2019-06-21 0

-

什么是闪存控制器架构?2019-09-27 0

-

一款高压PFC控制器简介2020-07-24 0

-

基于FAN7930B的PFC控制器应用2020-07-31 0

-

网关控制器的功能和特点2020-12-21 0

-

新型功率因数校正PFC控制器NCP1601资料推荐2021-03-29 0

-

PFC和PWM控制器CM6806相关资料下载2021-03-31 0

-

PFC和PWM组合控制器CM6805AB资料推荐2021-04-15 0

-

PFC控制器IRll50的主要特点及引脚功能有哪些?2021-04-20 0

-

控制器MP2200产品特点及功能介绍2021-09-02 0

-

PFC能否用UCC28056单相临界模式PFC控制器呢?2023-07-31 0

-

ML4835的PFC控制器电路2009-07-17 1751

全部0条评论

快来发表一下你的评论吧 !