资料下载

FPGA的演变过程和内部结构的资源使用说明

历史上,可编程逻辑器件经历了从PROM ( Programmable Read Only Memory )、PLA(Programmable Logic Array) 、PAL(Programmable Array Logic) 、可重复编程的GAL(Generic Array Logic ) ,到采用大规模集成电路技术的EPLD ,直至CPLD 和FPGA 的发展过程。

可编程逻辑器件大致的演变过程如下:

(1)20 世纪70 年代,熔丝编程的PROM 和PLA 器件是最早的可编程逻辑器件。

(2) 20 世纪70 年代末,对PLA 进行了改进, AMD 公司推出PAL 器件。

(3) 20 世纪80 年代初, Lattice 公司发明电可擦写的、比PAL 使用更灵活的GAL 器件。

(4) 20 世纪80 年代中期, Xilinx 公司提出现场可编程概念, 同时生产出了世界上第一片FPGA 器件。同一时期, Altera 公司推出EPLD 器件,较GAL 器件有更高的集成度,可以用紫外线或电擦除。

(5) 20 世纪80 年代末, Lattice 公司又提出在系统可编程技术,并且推出了一系列具备在系统可编程能力的CPLD 器件,将可编程逻辑器件的性能和应用技术推向了一个全新的高度。

(6) 进入20 世纪90 年代后,可编程逻辑集成电路技术进入飞速发展时期。器件的可用逻辑门数超过了百万门,并出现了内嵌复杂功能模块(如加法器、乘法器、RAM 、CPU 核、DSP 核、PLL 等)的SOPC(System On a Programmable Chip ) 。

一、CPLD 的结构与工作原理

基于乘积项的PLD 结构(PRODUCT-TERM )。在流行的CPLD 中,Altera 的MAX7000S系列器件具有一定典型性,在这里以此为例介绍CPLD 的结构和工作原理。

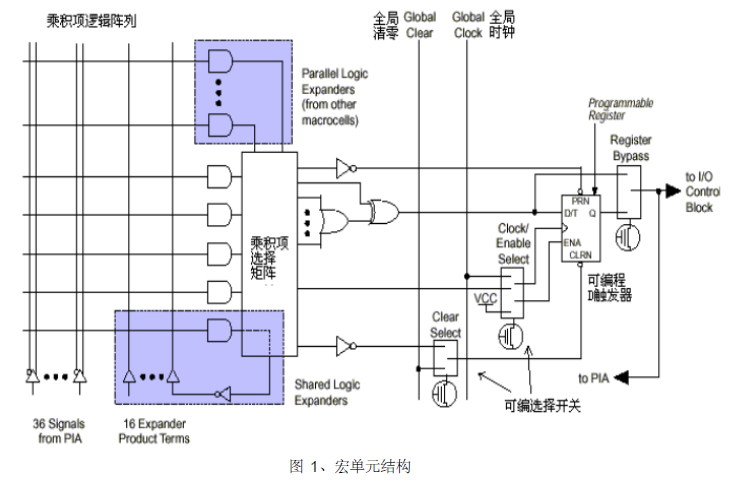

MAX7000 系列器件包含32~256 个宏单元,其单个宏单元结构如图1。每16 个宏单元组成一个逻辑阵列块( LAB )。每个宏单元含有一个可编程地“与”阵列和固定地“或”阵列,以及一个可配置寄存器, 每个宏单元共享扩展乘积项和高速并联扩展乘积项, 它们可向每个宏单元提供多达32 个乘积项,以构成复杂地逻辑函数。

如图,宏单元左侧是乘积项阵列,实际就是一个与或阵列,每一个交叉点都是一个可编程熔丝,如果导通就是实现“与”逻辑。后面的乘积项选择矩阵是一个“或”阵列。两者一起完成组合逻辑。图右侧是一个可编程D 触发器,它的时钟,清零输入都可以编程选择,可以使用专用的全局清零和全局时钟,也可以使用内部逻辑(乘积项阵列)产生的时钟和清零。如果不需要触发器,也可以将此触发器旁路,信号直接输给PIA 或输出到I/O 脚。MAX7000 结构中包含5 个主要部分,即逻辑阵列块、宏单元、扩展乘积项(共享和并联)、可编程连线阵列和I/O 控制块。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章