DDR5内存即将到来!

电子说

描述

近几个月来,有关下一代DDR内存的讨论一直沸沸扬扬,因为制造商们一直在展示各种各样的测试模块,为推出完整的产品做准备。计划使用DDR5的平台也在迅速兴起,在消费者中广泛使用之前,预计将在企业端首次亮相。同样,开发也是分阶段进行的:内存控制器、接口、电气等效测试IP和模块。SK Hynix已经进行到了最后一个阶段,或者至少是这些模块中的芯片。

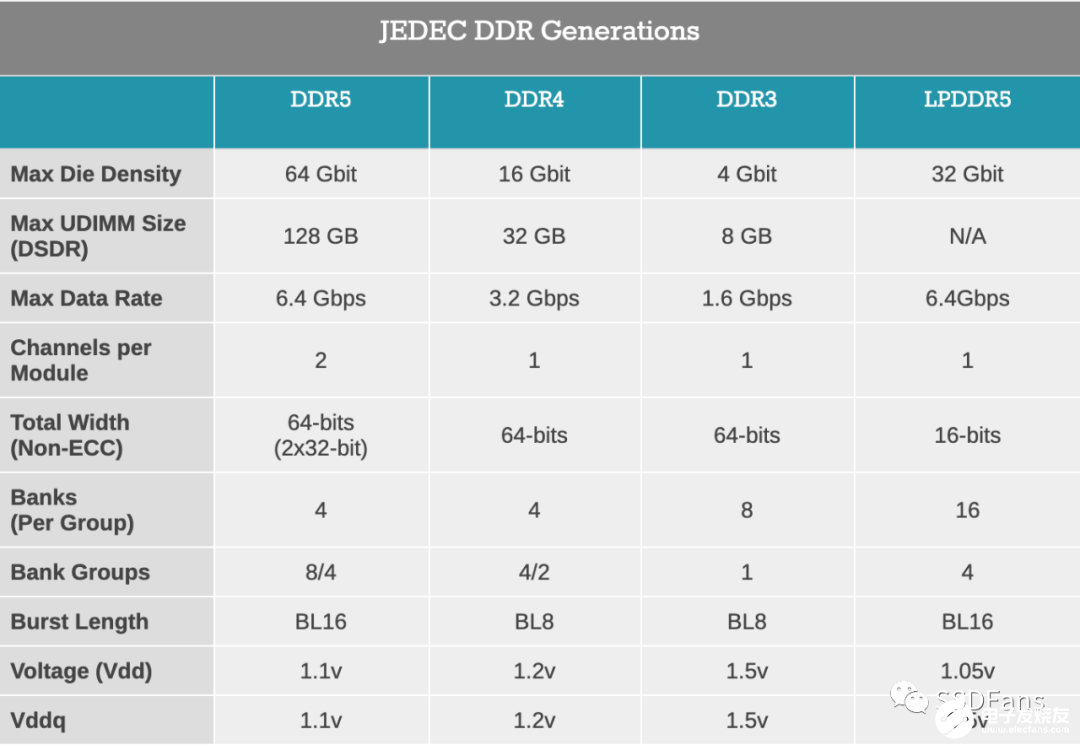

DDR5是下一代用于大多数主要计算平台的平台内存。该规范(于2020年7月发布)将主电压从1.2 V降至1.1 V,将最大硅芯片密度提高了4倍,最大数据速率翻倍,存储数量翻倍。简而言之,JEDEC DDR规范允许在DDR5-6400上运行128 GB无缓冲模块。在电源允许的情况下,RDIMM和LRDIMM应该能够更高。

DDR领域中的每个方面都需要从四个角度进行迭代。容量是最明显的一个,但内存带宽在我们看到的大型核计数服务器中常见的多核工作负载的性能扩展中也发挥着关键作用。另外两个是功耗和延迟,是体现性能的一个关键指标。

使用DDR5,实现这一功能的主要更改之一是系统查看内存的方式。DDR5不是每个模块一个64位的数据通道,而是每个模块两个32位的数据通道(在ECC中是40位)。脉冲长度增加了一倍,这意味着每个32位通道仍然会为每个操作提供64字节,但是可以以一种更加交错的方式来实现。这意味着标准的“双64位通道DDR4”系统将转变为“四位32位通道DDR5”结构,这样每个记忆模块就以一种更加可控的方式提供了64位。这也使得双倍的数据速率(增加峰值带宽的一个关键因素)变得更容易,并且具有更细粒度的存储体刷新功能,该功能允许在使用内存时进行异步操作,从而减少了延迟。

电压调节也从主板移到了内存模块,允许模块根据自己的需要调节。DDR4采用了每个芯片的Vdroop控制,但这将整个想法推进到更严格的电源控制和管理阶段。它还将电源管理交给了模块供应商而不是主板制造商,允许模块制造商确定更快内存所需的容量,看看不同的固件如何应对肯定会超出规范的非JEDEC标准游戏内存也是一件趣事。

SK-Hynix宣布,他们已经准备好向模块制造商提供DDR5-ECC内存,特别是16个基于其1Ynm流程构建的千兆芯片,支持1.1伏的DDR5-4800到DDR5-5600。SK-Hynix表示,如果采用正确的封装技术(如3D-TSV),合作伙伴可以制造256gb的lrdimm。为了提供比JEDEC更快的速度,额外的芯片装箱必须由模块制造商自己完成。SK Hynix似乎也有自己的模块,特别是DDR5-4800上的32GB和64GB RDIMM,并承诺提供高达DDR5-8400的内存。

SK Hynix没有提供这些模块的子定时信息。JEDEC规范为DDR5-4800定义了三种不同的模式:

DDR5-4800A: 34-34-34

DDR5-4800B: 40-40-40

DDR5-4800C: 42-42-42

尚不清楚SK Hynix使用的是哪一种。模块上写着“4800E”,但是这似乎只是模块命名的一部分,因为JEDEC规范没有超过DDR5-4800的CL值42。

对于带宽,其他内存制造商已经引用了DDR5-4800每个模块理论上38.4 GB/s的数据,他们已经看到有效数字在32 GB/s范围内。这比DDR4-3200上每个通道的20-25GB/s有效速率更高。其他内存制造商已经宣布,他们将从今年年初开始提供给客户试用DDR5。

公告中提到,英特尔是这些模块的主要合作伙伴之一。英特尔已承诺在其Sapphire Rapids Xeon处理器平台上启用DDR5,预计将于2021或2022年末首次发布。声明中没有提到AMD,也没有任何Arm合作伙伴。

SK Hynix表示,预计在2022年DDR5将占全球市场的10%,2024年将增至43%。在这一点上,消费者平台的交叉点有些模糊,因为我们可能只完成了DDR4周期的一半(或不到一半)。通常,当新旧技术的市场份额相等时,它们之间可能会出现成本拦截,但是DDR5要求的额外电压调节成本很可能会推高模块成本,从JEDEC模块的标准电源供应扩展到超频模块的更强大的解决方案。然而,在这方面,它应该使主板更便宜。

责任编辑:haq

-

物理网时代即将到来了2014-07-23 0

-

DDR3/4都还没玩够,DDR5已经来啦2021-08-12 0

-

国产内存即将到来_可业内却判DDR死刑2018-04-05 4718

-

美光宣布出样DDR5内存 它的特性有哪些2020-01-12 3366

-

内存条ddr4和显卡ddr52020-07-30 2517

-

龙耀D50 Xtreme DDR4系列内存超过即将到来的DDR52020-12-24 2131

-

DDR5升级背后的技术玄机2021-01-13 4584

-

DDR3内存突然涨价50% DDR5内存将要上市2021-02-02 3311

-

DDR5内存和数据中心正迎来发展新契机2021-05-01 2089

-

新一代DDR5内存模组密集发布,支持DDR5 CPU随后就到!2021-04-27 13544

-

DDR5进入放量元年,内存性能提升50%以上!2021-10-25 4071

-

金士顿DDR5内存通过英特尔内存解决方案_瑞虎8西伯利亚版上市发布2022-03-16 1158

-

DDR5内存普及率不高,是PMIC的锅?2022-07-12 8879

-

ddr5的主板可以用ddr4内存吗 几代CPU才能上DDR52023-08-09 14276

-

DDR6和DDR5内存的区别有多大?怎么选择更好?2024-01-12 4334

全部0条评论

快来发表一下你的评论吧 !