贴片晶振的PCB layout需要注意哪些?

电子说

描述

看了这篇文章,你还不知道晶体和晶振的区别,你来打我

晶振有两个比较重要的参数,频偏和温偏,单位都是PPM,通俗说,晶振的标称频率不是一直稳定的,某些环境下晶振频率会有误差,误差越大,电路稳定性越差,甚至电路无法正常工作。

所以在PCB设计时,晶振的layout显得尤其的重要,有如下几点需要注意。

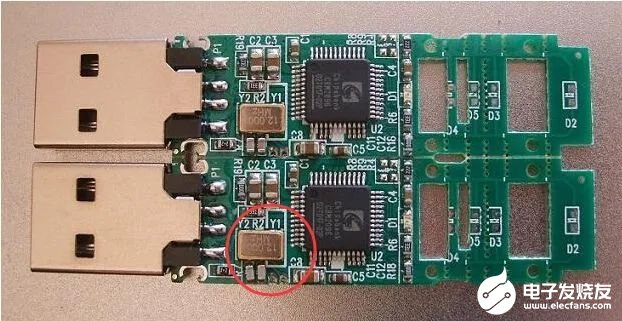

两个匹配电容尽量靠近晶振摆放。

晶振由石英晶体构成,容易受外力撞击或跌落的影响,所以在布局时,最好不要放在PCB边缘,尽量靠近芯片摆放。

晶振的走线需要用GND保护好,并且远离敏感信号如RF、CLK信号以及高速信号。

在一些晶振的PCB设计中,相邻层挖空(净空)或者同一层和相邻层均净空处理,第三层需要有完整的地平面,这么做的原因是维持负载电容的恒定。

晶振负载电容的计算公式是:

CL=C1*C2/(C1+C2)+Cic+Cp

Cic为集成电路内部电容,Cp为PCB板的寄生电容,寄生电容过大,将会导致负载电容偏大,从而引起晶振频偏,这个时候减小匹配电容C1和C2可能会有所改善,但这也是治标不治本的措施。

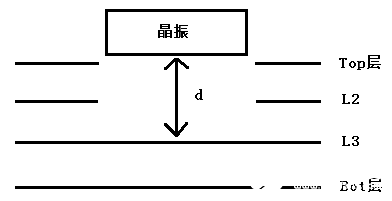

晶振相邻层挖空是如何控制寄生电容Cp的呢?

电容的物理公式是:C=εS/4πKd,即晶振焊盘与邻近地平面之间的面积S和距离d均会影响寄生电容大小,因为面积S是不变的,所以影响寄生电容的因素只剩下距离d,通过挖空晶振同一层的地和相邻层的地,可以增大晶振焊盘与地平面之间的距离,来达到减小寄生电容的效果。

电容容值和物理量之间的关系

简单画了一个图示,如下一个4层板,晶振放在Top层,将Top层和相邻层净空之后,晶振相对于地平面(L3),相比较没有净空之前,这个距离d是增大的,即寄生电容会减小。

晶振的L1和L2层均净空处理

晶振的摆放需要远离热源,因为高温也会影响晶振频偏。

我们知道晶振附近相邻地挖空处理,一方面是为了维持负载电容恒定,另一方面很大原因是隔绝热传导,避免周围的PMIC或者其他发热体的热透过铜皮传导到晶振,导致频偏,故意净空不铺铜,以隔绝热的传递。

为什么温度会影响晶振频率呢?

当晶振加热或者降低到某个温度后再降到常温,与最初在常温下测试通常情况下会有一定的变化,这是因为晶体的热滞后现象,带温度补偿的TCXO相对来说精度会好不少,可以有效解决晶体温漂,但一般TCXO都是M以上级别较多,KHz的很少,受限于生产工艺。

责任编辑:haq

-

列举能手工焊接的贴片晶振2012-11-16 0

-

常用贴片晶振2013-07-16 0

-

贴片晶振与插件晶振的运用2013-11-04 0

-

贴片晶振:以要求来选用贴片晶振2014-04-02 0

-

PCB layout软件该如何学习和PCB设计需要注意的问题2014-09-16 0

-

贴片晶振用途有哪些?2015-09-07 0

-

采购晶振需要注意什么2017-06-08 0

-

如何拆卸贴片晶振2017-06-28 0

-

贴片晶振的焊接方法和注意事项2019-07-27 0

-

贴片晶振替换插件晶振前需要考虑什么2020-04-29 0

-

MSP430单片机外围贴片晶振选型和设计标准2020-07-03 0

-

高价回收晶振,专业收购贴片晶振2021-09-16 0

-

贴片晶振的PCB layout需要注意哪些2022-02-10 2940

-

10年老司机倾囊相授,贴片晶振的PCB layout需要注意哪些?2021-01-29 1024

全部0条评论

快来发表一下你的评论吧 !