浅谈PCB设计产生EMI的问题

描述

众所周知合理的层叠结构和连续的参考平面能够很有效的抑制EMI问题,但有时候设计就涉及到模拟数字信号隔离的问题。

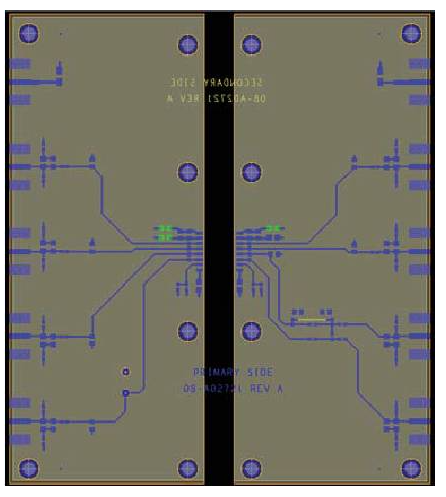

图1

图1是一个电源转换芯片,一边为数字信号,一边为模拟信号,数字信号模拟信号隔开有助减小数字信号和模拟信号之间的相互干扰。但中间分隔区域导致了参考平面的不连续,从而产生EMI的问题。

有经验的设计人员遇到这种情况可能在模拟低和数字地之间加入缝补电容(Stitching Capacitance)或者磁珠,通常这些情况下都使用陶瓷电容。然而加电容会带来一些不利的因素:

1.电容为分立器件,电容会额外的增加pad和via,pad和via都会增加寄生电感。

2.安装陶瓷电容由于容值较小,其有效的作用空间较小。电容需要安装到适当的位置。

3.安装电容起作用的频率范围一般低于200MHz。

PCB设计尽量让电源平面和地平面紧耦合,让邻近的两个面之间形成耦合平面电容。我们能不能有一个办法即让模拟地和数字地分开又让分开平面上噪声更好的耦合到地平面上去呢?方法如下图所示:

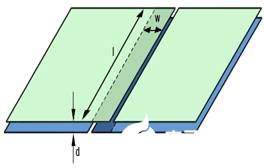

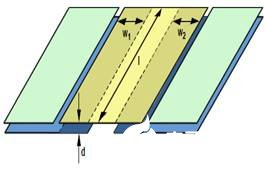

图2 图3

图2图3为两种平面耦合方式

将上下两个平面在分割区域形成一个重叠的区域,重叠区域会形成一个耦合平板电容,这样既可以把模拟和数字区域分开,又可让模拟地和数字地通过耦合平板电容链接到一起。

通过上述平面形成电容有以下特点:

1.寄生电感小,另外电容均匀分散在平面重叠区域。

2.平面耦合电容起作用的频率范围更广。

3.埋容平面与平面是电源平面还是地平面无关。

4.埋容结构最好位于板子的内层。表层或者底层会减小平板耦合电容的效果。

图2和图3两种方式各有优点和缺点,图2单位平面形成的电容较大,但如果整版都这样分割,PCB板子的容易折断,此方法适用于很小的区域分割;图3的单位面积形成的电容较小,但形成的PCB比较牢固。使用于板子空间较大。

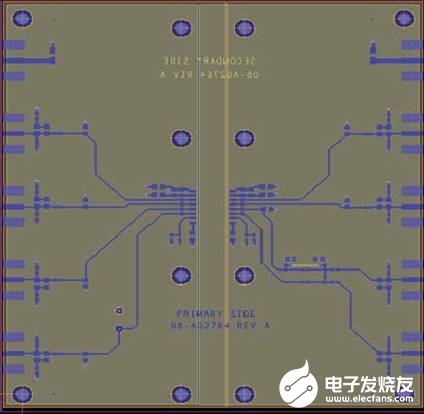

图4 分割区域形成平面耦合电容

Remark:平面耦合电容的计算,以图4为例:

图4可以看做是左右两个深黄色下的耦合电容串联的结果。

C=(c1*c2)/(c1+c2),其中c1 c2 分别为左右两个耦合电容,假设左右耦合电容相等则有C1=c2=(ε*s)/d,其中ε=ε_0*ε_r,ε_0为真空介电常数8.854*1e-12F/m, ε_r为相对介电常数,比如FR4为4.5;S为相互重叠的面积,比如图4中深黄色区域,d为相互重叠区域距离。

Edadoc公司有款设计用到此方案,设计中重叠区域的长4300mil,宽250mil,带入公式中:

C=(4.5*(8.854*e-12)*4300*0.0254*(10e-3)*250*0.0254*(10e-3))/(5.12*0.0254*(10*e-3))=212pf

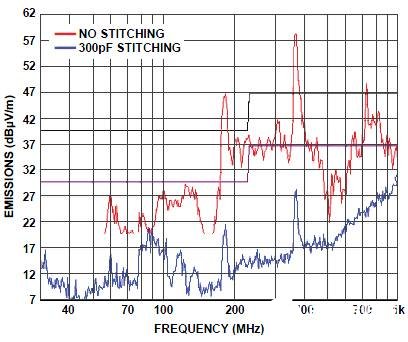

图5 形成330pf缝补电容和没有缝补电容实测对比图

编辑:hfy

-

如何解决高速PCB设计中的EMI问题2020-03-25 1430

-

PCB设计:在真实世界里的EMI控制2021-06-23 727

-

PCB设计中EMI控制原理与实战技巧2011-05-19 0

-

浅谈PCB设计2011-06-15 0

-

表面安装pcb设计工艺浅谈2012-08-20 0

-

高速PCB设计解决EMI问题的九大规则2016-01-19 0

-

解决高速PCB设计EMI(电磁干扰)的九大规则2017-11-02 0

-

浅谈射频PCB设计2019-03-20 0

-

浅谈PCB设计七大流程2010-04-16 2481

-

高速PCB设计的EMI抑制探讨2012-03-31 1618

-

如何快速解决PCB设计EMI问题2017-01-14 817

-

高速PCB设计EMI有什么规则2019-08-21 831

-

低EMI DC/DC变换器的PCB设计2020-02-04 3893

-

PCB设计如何降低EMI2021-01-28 2162

-

PCB设计之五个EMI设计指南2020-10-09 3194

全部0条评论

快来发表一下你的评论吧 !