仿真反射详解:接收端信号与测试点信号的区别

描述

场的反射

来到了场的领域,我们要做的第一件事就是把我们的波形拆开,让我们先来看看之前说过的测试点的问题。为了将问题简化,我们假定一个这样的条件:

1.在拓扑上,源端完全匹配,末端全反射,理想的100Ω差分传输线。

2.传输的为我们之前模拟的DDR3信号,由三次谐波构成。

3.测试点位置离接收端距离为500mil。

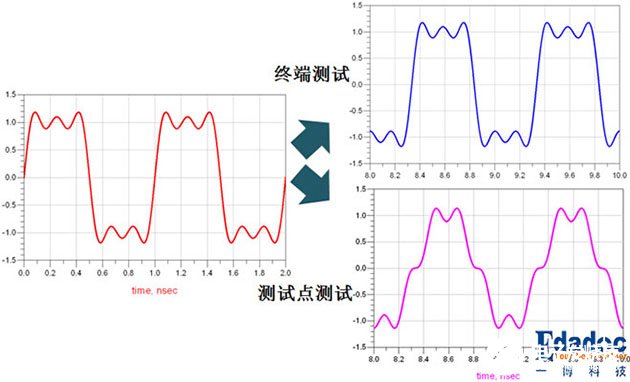

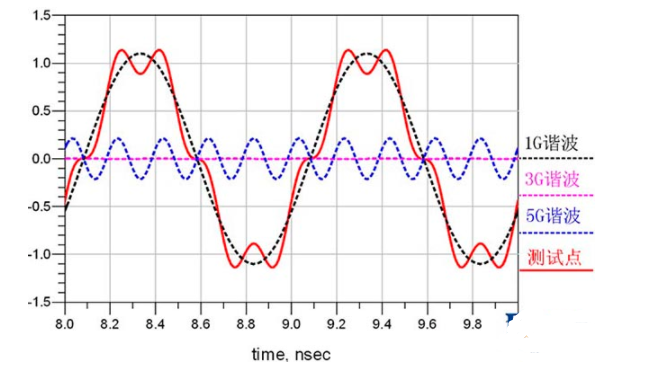

好的,现在开始让我们分析,首先,如同大家在之前文章中看到的,我们接收端信号与测试点信号的区别是这样的:

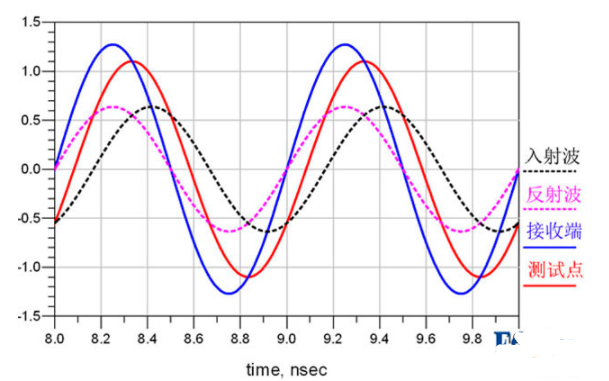

让我们看看1GHz谐波发生了什么:

测试点测到的是两个信号叠加的波形,一个是入射信号,一个反射波。反射波与入射波幅值相等(末端全反射);走过的路程比入射波多1000mil(一来一回),也就是六分之一波长;两个信号的相位差也就是60°。

这样,我们就看到了1GHz的谐波在接收端时蓝色的波形,在测试点处为红色的波形,幅值衰减,相位超前。

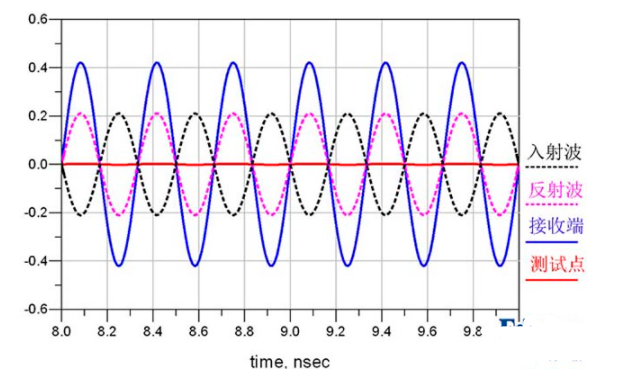

再看看3GHz的谐波:

同样的1000mil,对于3GHz来说就是半波长,相位差180°,这样我们就发现在测试点处3GHz的频率分量基本上就衰减完了。

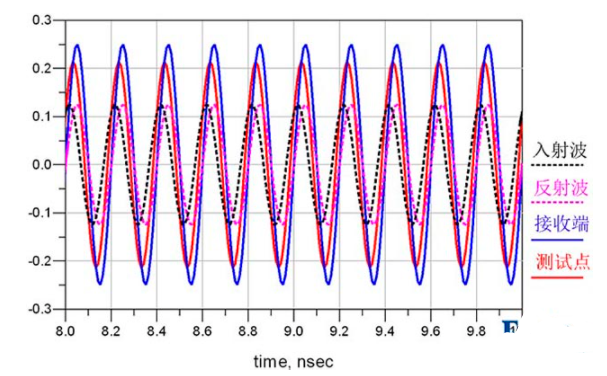

再来看看5GHz的谐波:

相位差300°,于是看到测试点的波形衰减,相位滞后。

将在测试点的三个频率分量的叠加再叠加起来之后:

不知道大家对于这样的分析方法是感觉如何,是觉得把东西变复杂了还是变简单了呢?怎么想没有关系,下一篇中高速先生会将这样的方法再拓展,相信你会爱上这个方法的。

反射疑云

在前文中有不少公式与计算,但其实个人觉得应用工程师要做的是知道趋势,知道影响范围,并不需要精确计算,那是软件干的事情。

最近听到一个理论,说大数据时代,人们只需要知其然,不需要知其所以然。想象一下,当我们要做一个项目时,我们可以轻而易举的知道一些其他类似项目哪些结构成功了哪些结构失败了,我们还需要理论分析干嘛呢?

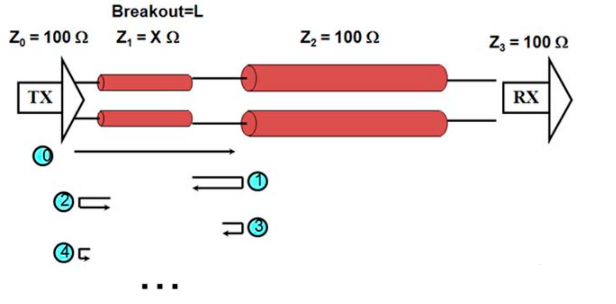

这句话到底有没有道理大家仁者见仁智者见智,下面我们继续来解决我们的反射问题:Breakout区域有一次阻抗不连续,但走出该区域之后,走线从细变宽,会增加一次反射,那是不是全程按照breakout区域走线会比较好?

首先将问题进行简化,由于本身反射系数不大,第四次反射很小,假设传到RX的信号是最初的信号加上第二次反射的信号。

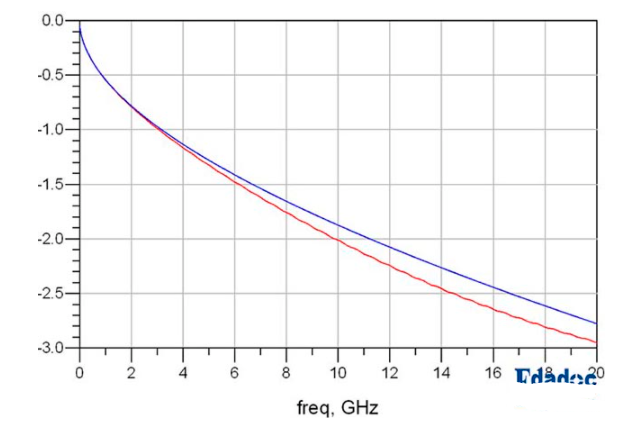

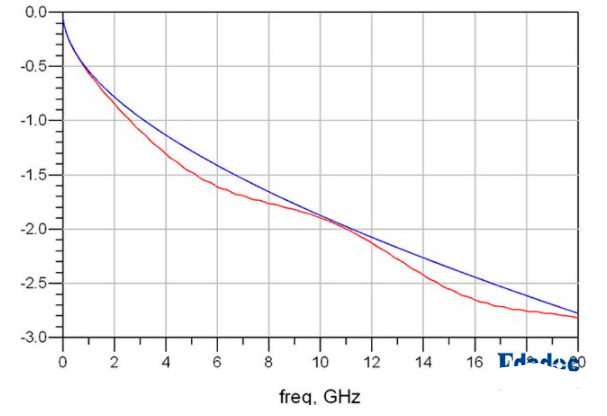

一段长为X的阻抗不连续,对哪个频率的影响最大呢?当相位差为(2n+1)π/2时,也就是相差二分之一波长的时候(反射一来一回,对应的X为四分之一波长)。

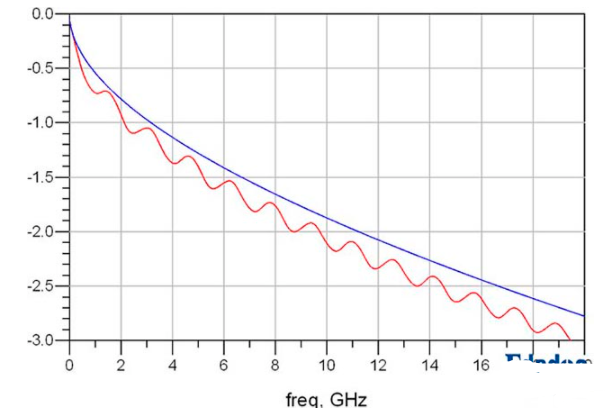

也就是说,当X为100mil时,第一次最大衰减的频点为15GHz,我们从S参数中可以很明显的看出:

当X为300mil时,第一次谐振频率为5GHz:

假设总线长为2000mil,而全部按照breakout区域走线的阻抗去走的话,第一次谐振频率则变成了750MHz,谐振周期为1.5GHz:

回头呼应反射系列文章的第一节,从那几张图中可以知道:

四分之一波长差的损耗为二分之一波长差损耗的30%,二分之一波长差时完全没有了,四分之一波长差时还有70%。全反射(反射系数为1)时,在谐振频率损耗为100%,谐振频率的损耗跟反射强度有关。

看到这里估计各位看官也明白了,阻抗不连续越长,影响的频率越低。的的确确是因为阻抗不连续较短,反射淹没在上升沿当中了。

根据这套理论,我们很容易去判断设计中的一些细节对整个系统的影响到底有多大,举个例子:

信号速率越来越高是一种趋势,于是各种优化方案也被人们提了出来,这两个可能是近年来开始被大家熟悉的优化方案,加粗反焊盘上的走线或者填补走线附近的参考层,以防止反焊盘上扇出的走线阻抗偏高。可是这到底有多大的影响或者优化呢?

排除一些特殊情况(连接器,板厚较厚需要使用较大过孔等等),这一段在antipad上的走线长度大约为20mil(亲,不要把过孔pad算上哦)。

20mil的第一次谐振频率大约是多少呢?75GHz(四分之一波长)。如果我们按照二十分之一波长(影响不到1%)来算的话,对应的频率也是15GHz。您的信号需要做这样的优化吗?

看完这些之后,相信能帮助大家在工(he)程(ge)师(wan)精(sui)神和工(qiang)匠(po)精(zheng)神中间找到一个平衡点了。

编辑:hfy

-

CX3是如何从接收到的MIPI传感器信号中重建测试点信号(H8、G6、H5)的?2024-02-23 0

-

添加测试点会不会影响高速信号的质量?2009-09-06 0

-

什么是PCB的测试点?2017-02-06 0

-

各测试点对系统杂散测试的意义2017-11-15 0

-

EDA教程:在PADS中添加表面型测试点2019-06-10 0

-

添加测试点对高速信号的质量影响概述!2019-08-30 0

-

信号反射的几个基本问题分析2019-10-16 0

-

时钟信号回沟与测试点位置有关吗2020-11-25 0

-

请问时钟信号回沟与测试点位置有关吗?2020-12-15 0

-

在电路板上设置测试点?测试点是什么?2021-09-17 0

-

在PAD中添加表面型测试点2010-07-08 5001

-

如何找准PCB设计中的测试点位置2021-01-14 6127

-

测试点对高速信号质量的影响2022-09-16 1733

-

为什么要在PCB中使用测试点?2023-05-11 2268

-

信号完整性的反射因素详解2023-09-25 720

全部0条评论

快来发表一下你的评论吧 !