FOWLP技术如何使摩尔定律保持有效?

描述

摩尔定律在制程技术中处于最后一刻,因此高级包装占据了接力棒。扇出晶圆级封装(FOWLP)等先进技术可提高组件密度并提高性能,并帮助解决芯片I / O限制。然而,成功使用这种技术的关键是从一开始就将封装包括在芯片设计中。

数十年来,半导体加工技术一直将特征尺寸从数十微米稳步降低到单位纳米,在此过程中每18个月有效地使部件密度翻了一番。但是,与此同时,设计和制造成本上升了,阈值余量变窄了,许多其他挑战似乎阻碍了进一步的发展。此外,单个芯片中晶体管密度的增加在将芯片连接在一起时产生了问题,例如,限制了IO引脚数和芯片到芯片互连的速度。

事实证明,这些限制在需要大量高带宽内存的应用程序(如人工智能(AI)边缘和云系统)中尤其成问题。为了解决这些问题并继续提高组件密度,该行业开发了几种先进的封装技术,这些技术允许多个芯片以紧凑,高性能的封装互连,该封装在板上可以作为单个组件工作。

一种这样的技术FOWLP已经用于移动设备的批量生产中。FOWLP封装过程涉及将单个芯片安装在称为重分布层(RDL)的中介层基板上,该中介层可提供芯片之间以及与IO焊盘的互连,所有这些封装都封装在一个包覆成型中。

正面朝上和正面朝下的方法

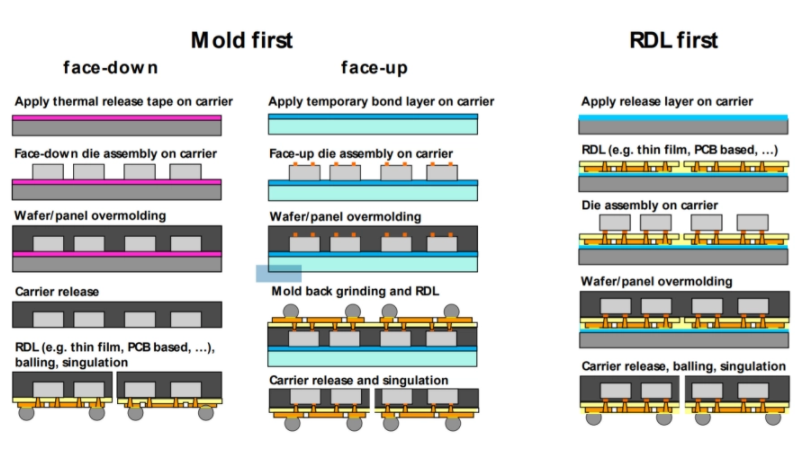

FOWLP有多种变体,每种变体使用的制造步骤略有不同,可从多家供应商处获得(图1)。FOWLP组件可以使用模制优先的工艺来创建,芯片朝下或面朝上安装,或者使用RDL优先的组件。

图1 FOWLP技术的变化形式包括模制优先和RDL优先的装配选项。资料来源:微型机器

在“先铸模”方法中,芯片管芯使用临时粘合或热释放层附着到载体上,然后将其模制成封装。如果裸片正面朝下安装,则下一步是释放临时层,附上RDL,并形成完成封装的焊球。如果裸片面朝上安装,则需要一些其他步骤。

首先,必须在包覆成型之前通过在其上添加铜柱来扩展各个管芯的I / O连接。模制之后,在连接RDL和形成焊球之前,必须将模制的背面接地,以露出柱子。

在以RDL为先的方法中,RDL使用临时释放层附着到载体,而管芯附着到RDL。然后,该组件被包覆成型,释放载体,并形成焊球。两种方法的最后一步是将组件分开,这些组件被整体形成为单独的设备。

这些不同的方法提供了不同的成本和性能折衷。在成本方面,模具优先,面朝下的方法避免了制造铜柱和进行背面研磨的需要,因此具有较低的制造成本。它最适合于低I / O数量的应用;然而,存在管芯移位,晶片翘曲等问题,从而限制了其在复杂的多芯片封装中的使用。

正面朝上的方法减少了这些问题,并且由于芯片的背面完全暴露在热量管理方面具有优势,因此有利于散热。以RTL为先的方法的优势在于,它允许在其制造过程中使用已知的良好管芯(KGD),从而提高了成品率。

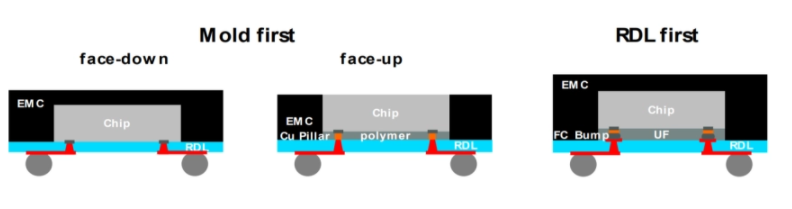

在性能方面,面朝下方法的连接路径比其他两种方法短(图2)。这两种方法都具有铜柱,该铜柱将连接扩展到RDL,并且在芯片下方具有一层材料,在连接之间增加了寄生电容,从而影响了它们的高频性能。

图2 FOWLP方法的选择会影响走线长度并产生寄生效应,需要在芯片设计中加以考虑。源微机

先进包装的新工具

随着逻辑速度的提高,由于封装的制造而产生的这种细微的寄生效应变得越来越重要,并且可以极大地改变信号时序和特性。因此,寻求使用这种高级封装技术的开发人员将需要确保他们的仿真和设计验证工作包括封装以及芯片设计,以确保成功。

芯片供应商开始开发自己的内部工具,以将封装和芯片设计集成到为其客户的单个处理流程中。但是,内部工具可能会限制设计人员对使用供应商流程制作的芯片的选择。那些想要混合来自不同工艺的芯片的人可能需要依靠外包组装和测试(OSAT)设备提供的工具来验证完整封装的芯片设计。EDA公司还加紧开发可支持这些高级包装要求的设计和验证工具。

无论哪种方式,随着行业不断推动保持摩尔定律的有效期,高级包装的作用将继续增长。对更小,更快,功能更强大的芯片和系统的需求将继续存在,而封装现在似乎已成为开发人员需要探索的新领域。

Rich Quinnell是一位退休的工程师和作家,并且是EDN的前总编辑。

编辑:hfy

-

摩尔定律,摩尔定律是什么意思2010-02-26 1509

-

晶圆和摩尔定律有什么关系?2011-12-01 0

-

介绍28 nm创新技术,超越摩尔定律2012-08-13 0

-

摩尔定律也适用于EPON芯片商用之路?2011-09-27 0

-

半导体行业的里程碑“摩尔定律”竟是这样来的2016-07-14 0

-

摩尔定律推动了整个半导体行业的变革2019-07-01 0

-

摩尔定律还能走多远看了就知道2021-02-01 0

-

摩尔定律在测试领域有哪些应用?2021-04-13 0

-

请问摩尔定律死不死?2021-06-17 0

-

IC芯片的密度和计算机的速度能够一直按照摩尔定律前行吗?2021-07-22 0

-

摩尔定律_摩尔定律是什么2012-05-21 2751

-

摩尔定律死去,半导体怎么办?2016-05-23 1434

-

摩尔定律的历程2017-10-24 1904

-

摩尔定律是什么_摩尔定律提出者及含义2018-03-09 28393

-

功能密度定律是否能替代摩尔定律?摩尔定律和功能密度定律比较2024-02-21 209

全部0条评论

快来发表一下你的评论吧 !