PCB设计:走线包地要打孔有什么建议?

描述

线宽要按50或者100欧姆设计,差分线要做等长,电源走线要粗一点,电源地平面最好紧耦合等等这些PCB设计的常规操作相信没人质疑。那么对于走线包地要打孔,估计你们也不会有什么意见吧……

有些PCB设计的操作,工程师们已经在脑海中形成了定势的思维,甚至都已经写进了各种skill或者约束规则里面。无可否认,大部分这些设计都是经过了多次的验证,说白了就是换谁来做都不会有问题的那种。前面也说了,对于走线包地要打孔这一点,其实看起来也是一个常规的操作,但是却并不是每个人做都能做得很好的哦。我们最近就收到这样的一个case,本来想炫一把包地打孔的高手风范,结果还比不上包地不打孔这种我们认为错误的做法。

这个板子也是一个比较特殊的板子,首先它只是一块双面板,板厚是1mm,其次它居然要走高速线,板内的高速线达到了10Gbps。听起来是不是很恐怖?当然其实在我们看来,走表层也不是不能走10Gbps的信号,其实我们甚至还走过25Gbps的光模块信号。由于可以只在表层走完,而且我们知道1mm的板厚如果要控制100欧姆差分阻抗的话,也就只能通过表层共地的方式进行阻抗控制了,下面底层的地基本是影响不了阻抗的了。通过阻抗的精确计算后,我们确定了差分线的线宽,线距,以及信号线两边到包地的距离以便控制到阻抗。如下所示:

板子很简单,这些10Gbps的高速线就几对,因此工程师在我们高速先生还没反应过来的时候就已经把走线走出来了,几inch的走线,走线走在表层,底层铺下地,然后中间打一些地过孔,距离大概500mil左右的地孔,部分PCB走线如下所示:

然后这个那么“简单”的设计项目,也没有说要做仿真,后面准备投板了,才象征性的发给我们检查一下。我们初步看了下就觉得有点问题(这里先卖个关子哈),认为这个设计比较特别,建议做一下仿真。PCB工程师和客户都觉得会不会夸张了一点,看着我们高速先生坚定的眼神之后,还是同意去看一下。

果然,仿真证实了我们的怀疑,从插损和回损来看,在较低的频段就会有比较尖峰的谐振点。基本上肯定会影响到10Gbps的信号了,下文会有眼图的情况哈。

正好这类10Gbps的走线不止一对,另外有一对由于底层需要铺其他的电源和走线,因此不能像上面这对走线一样,很幸福的拥有一个下面完整的参考层,因此另外一对走线只能完全通过表层的包地来控制阻抗,因此也就没必要在沿途打地过孔了。如下所示:

PCB工程师还战战兢兢的过来和我们高速先生说,这对走线底层没办法铺地,所以就没法打地过孔,会不会更差啊。

干脆我们怀着期待的心情又做了一次仿真,结果奇迹……并没有出现!!!

从插损曲线来看,谐振点变得更靠近而且很密了,间隔不到1个GHz就有一个谐振,看起来也是一个比较差的结果。

但是呢,俗话说得好,没有对比就没有伤害。有的东西看起来更差,但是我们一定要有信心,因为不知道什么时候,别人就会比你更差。我们把两种情况摆在一起看下,就会发现,其实不打孔这种看起来不对的做法,其实反而是两者较优的一方。

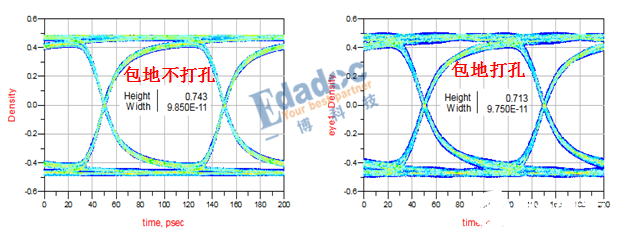

如果看不懂上图的无源参数也没关系,我们把眼图对比一下,你们就清楚了。

同样在10Gbps情况下,两者的眼图结果是这样的:你会发现眼高和眼宽都会有差异,其中眼高居然差了近30mV,抖动也有一定的差距。

当你千方百计想遵循规则或者一些常规操作去走的时候,可能出来的结果反而还不如一个“懒”的方法。我们经常会认为打地过孔进行包地肯定是只有好处没有坏处,但是高速设计本身却并没有人们想象得那么简单,很多细微的东西忽略了可能会出现这种反常的结果。

编辑:hfy

- 相关推荐

- 阻抗

-

#PCB设计 #Allegro速成教程 差分对走线电子技术那些事儿 2022-09-12

-

#PCB设计 #Allegro速成教程 蛇形走线演示电子技术那些事儿 2022-09-12

-

PCB.走线为什么不能走锐角和直角?# #pcb设计 #硬声新人计划学习电子知识 2022-09-23

-

如何修复PCB走线损坏问题#pcb设计jf_24750660 2022-11-01

-

PCB设计技巧Tips11:蛇形走线有什么作用?2014-11-19 0

-

PCB设计:差分对走线+其他建议和原则2015-01-08 0

-

开关电源的PCB设计(布局、排版、走线)规范2015-05-21 0

-

PCB设计走线的几点专家建议2018-12-05 0

-

PCB设计包地打孔的含义2019-05-30 0

-

有相关cc2541 antenna的pcb走线资料吗?2020-03-24 0

-

电源布局/网口电路/音频走线的PCB设计2021-03-04 0

-

PCB设计走线的规则是什么2021-03-17 0

-

PCB设计走线的宽度与哪些因素有关2021-10-11 0

-

PCB走线的设计细节详解2023-04-13 0

全部0条评论

快来发表一下你的评论吧 !