FPGA:状态机简述

描述

本文目录

前言

状态机简介

状态机分类

Mealy 型状态机

Moore 型状态机

状态机描述

一段式状态机

二段式状态机

三段式状态机

状态机优缺点

总结

扩展-四段式状态机

01. 前言

状态机是FPGA设计中一种非常重要、非常根基的设计思想,堪称FPGA的灵魂,贯穿FPGA设计的始终。

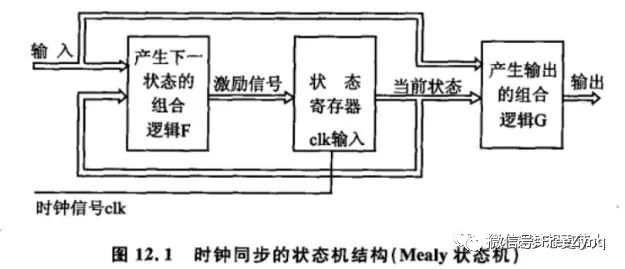

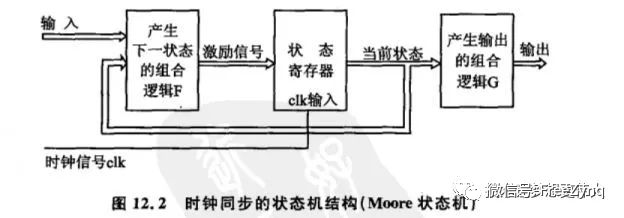

02. 状态机简介

什么是状态机:状态机通过不同的状态迁移来完成特定的逻辑操作(时序操作)状态机是许多数字系统的核心部件, 是一类重要的时序逻辑电路。通常包括三个部分:

下一个状态的逻辑电路

存储状态机当前状态的时序逻辑电路

输出组合逻辑电路

03. 状态机分类

通常, 状态机的状态数量有限, 称为有限状态机(FSM) 。由于状态机所有触发器的时钟由同一脉冲边沿触发, 故也称之为同步状态机。

根据状态机的输出信号是否与电路的输入有关分为 Mealy 型状态机和 Moore 型状态机

3.1,Mealy 型状态机

电路的输出信号不仅与电路当前状态有关, 还与电路的输入有关

3.2,Moore 型状态机

电路的输出仅仅与各触发器的状态, 不受电路输入信号影响或无输入

状态机的状态转移图, 通常也可根据输入和内部条件画出。一般来说, 状态机的设计包含下列设计步骤:

根据需求和设计原则, 确定是 Moore 型还是 Mealy 型状态机;

分析状态机的所有状态, 对每一状态选择合适的编码方式, 进行编码;

根据状态转移关系和输出绘出状态转移图;

构建合适的状态机结构, 对状态机进行硬件描述。

04. 状态机描述

状态机的描述通常有三种方法, 称为一段式状态机, 二段式状态机和三段式状态机。

状态机的描述通常包含以下四部分:

利用参数定义语句 parameter 描述状态机各个状态名称, 即状态编码。状态编码通常有很多方法包含自然二进制编码, One-hot 编码,格雷编码码等;

用时序的 always 块描述状态触发器实现状态存储;

使用敏感表和 case 语句(也采用 if-else 等价语句) 描述状态转换逻辑;

描述状态机的输出逻辑。

下面根据状态机的三种方法来具体说明

4.1,一段式状态机

1module detect_1( 2input clk_i, 3input rst_n_i, 4output out_o 5); 6reg out_r; 7//状态声明和状态编码 8reg [1:0] state; 9parameter [1:0] S0=2'b00; 10parameter [1:0] S1=2'b01; 11parameter [1:0] S2=2'b10; 12parameter [1:0] S3=2'b11; 13always@(posedge clk_i) 14begin 15 if(!rst_n_i)begin 16 state<=0; 17 out_r<=1'b0; 18 end 19 else 20 case(state) 21 S0 : 22 begin 23 out_r<=1'b0; 24 state<= S1; 25 end 26 S1 : 27 begin 28 out_r<=1'b1; 29 state<= S2; 30 end 31 S2 : 32 begin 33 out_r<=1'b0; 34 state<= S3; 35 end 36 S3 : 37 begin 38 out_r<=1'b1; 39 end 40 endcase 41end 42assign out_o=out_r; 43endmodul 44

一段式状态机是应该避免使用的, 该写法仅仅适用于非常简单的状态机设计。

4.2,两段式状态机

1module detect_2( 2 input clk_i, 3 input rst_n_i, 4 output out_o 5 ); 6 reg out_r; 7 //状态声明和状态编码 8 reg [1:0] Current_state; 9 reg [1:0] Next_state; 10 parameter [1:0] S0=2'b00; 11 parameter [1:0] S1=2'b01; 12 parameter [1:0] S2=2'b10; 13 parameter [1:0] S3=2'b11; 14 //时序逻辑: 描述状态转换 15 always@(posedge clk_i) 16 begin 17 if(!rst_n_i) 18 Current_state<=0; 19 else 20 Current_state<=Next_state; 21 end 22 //组合逻辑:描述下一状态和输出 23 always@(*) 24 begin 25 out_r=1'b0; 26 case(Current_state) 27 S0 : 28 begin 29 out_r=1'b0; 30 Next_state= S1; 31 end 32 S1 : 33 begin 34 out_r=1'b1; 35 Next_state= S2; 36 end 37 S2 : 38 begin 39 out_r=1'b0; 40 Next_state= S3; 41 end 42 S3 : 43 begin 44 out_r=1'b1; 45 Next_state=Next_state; 46 end 47 endcase 48 end 49 assign out_o = out_r; 50endmodule 51

两段式状态机采用两个 always 模块实现状态机的功能, 其中一个 always 采用同步时序逻辑描述状态转移, 另一个 always 采用组合逻辑来判断状态条件转移。

4.3,三段式状态机

1module detect_3( 2 input clk_i, 3 input rst_n_i, 4 output out_o 5 ); 6 reg out_r; 7 //状态声明和状态编码 8 reg [1:0] Current_state; 9 reg [1:0] Next_state; 10 parameter [1:0] S0=2'b00; 11 parameter [1:0] S1=2'b01; 12 parameter [1:0] S2=2'b10; 13 parameter [1:0] S3=2'b11; 14 //时序逻辑: 描述状态转换 15 always@(posedge clk_i) 16 begin 17 if(!rst_n_i) 18 Current_state<=0; 19 else 20 Current_state<=Next_state; 21 end 22 //组合逻辑: 描述下一状态 23 always@(*) 24 begin 25 case(Current_state) 26 S0: 27 Next_state = S1; 28 S1: 29 Next_state = S2; 30 S2: 31 Next_state = S3; 32 S3: 33 begin 34 Next_state = Next_state; 35 end 36 default : 37 Next_state = S0; 38 endcase 39 end 40 //输出逻辑: 让输出 out, 经过寄存器 out_r 锁存后输出, 消除毛刺 41 always@(posedge clk_i) 42 begin 43 if(!rst_n_i) 44 out_r<=1'b0; 45 else 46 begin 47 case(Current_state) 48 S0,S2: 49 out_r<=1'b0; 50 S1,S3: 51 out_r<=1'b1; 52 default : 53 out_r<=out_r; 54 endcase 55 end 56 end 57 58 assign out_o=out_r; 59endmodule 60

三段式状态机在第一个 always 模块采用同步时序逻辑方式描述状态转移, 第二个always 模块采用组合逻辑方式描述状态转移规律, 第三个 always 描述电路的输出。通常让输出信号经过寄存器缓存之后再输出, 消除电路毛刺。

05. 状态机优缺点

1、一段式状态机

只涉及时序电路,没有竞争与冒险,同时消耗逻辑比较少。

但是如果状态非常多,一段式状态机显得比较臃肿,不利于维护。

2、两段式状态机

当一个模块采用时序(状态转移),一个模块采用组合时候(状态机输出),组合逻辑电路容易造成竞争与冒险;当两个模块都采用时序,可以避免竞争与冒险的存在,但是整个状态机的时序上会延时一个周期。

两段式状态机是推荐的状态机设计方法。

3、三段式状态机

三段式状态机在状态转移时采用组合逻辑电路+格雷码,避免了组合逻辑的竞争与冒险;状态机输出采用了同步寄存器输出,也可以避免组合逻辑电路的竞争与冒险;采用这两种方法极大的降低了竞争冒险。并且在状态机的采用这种组合逻辑电路+次态寄存器输出,避免了两段式状态机的延时一个周期(三段式状态机在上一状态中根据输入条件判断当前状态的输出,从而在不插入额外时钟节拍的前提下,实现寄存器的输出)。

三段式状态机也是比较推崇的,主要是由于维护方便, 组合逻辑与时序逻辑完全独立。

06. 总结

灵活选择状态机,不一定要拘泥理论,怎样方便怎样来

07.扩展

四段式不是指三个always代码,而是四段程序。使用四段式的写法,可参照明德扬GVIM特色指令Ztj产生的状态机模板。

明·德·扬四段式状态机符合一次只考虑一个因素的设计理念。

第一段代码,照抄格式,完全不用想其他的。

第二段代码,只考虑状态之间的跳转,也就是说各个状态机之间跳转关系。

第三段代码,只考虑跳转条件。

第四段,每个信号逐个设计。

有兴趣的话可以自己去学习一下,或者http://www.mdyedu.com/product/299.html自行看视频。

责任编辑:xj

原文标题:FPGA 高手养成记-浅谈状态机

文章出处:【微信公众号:FPGA开源工作室】欢迎添加关注!文章转载请注明出处。

-

FPGA/CPLD状态机稳定性研究2012-01-12 0

-

状态机是什么意思2013-04-25 0

-

FPGA有限状态机2013-09-08 0

-

FPGA状态机2014-09-14 0

-

FPGA状态机为什么会跑飞2021-07-29 0

-

什么是状态机? 状态机是如何编程的?2021-10-20 0

-

FPGA状态机跑飞的原因是什么2021-11-01 0

-

FPGA状态机一段式简介2022-02-23 0

-

FPGA工程师:如何在FPGA中实现状态机?2013-03-29 12411

-

华清远见FPGA代码-状态机2016-10-27 484

-

简述使用QII状态机向导如何创建一个状态机2018-06-20 3969

-

FPGA之状态机的功能简述与学习建议2019-10-09 3219

-

FPGA之状态机的功能简述2019-10-09 3418

-

如何在FPGA中实现状态机2023-07-18 553

-

基于FPGA的状态机设计2023-07-28 488

全部0条评论

快来发表一下你的评论吧 !