i2c通信的详细讲解

通信网络

描述

什么是I2C通信

(1)I2C属于串行通信,所有的数据以位为单位在SDA上串行传输

(2)同步通信就是通信双方工作在同一个时钟下面,一般是通信的A方通过一根CLK线传输A自己的时钟给B,B工作在A传输的时钟下。所以通信的显著特征就是:通信中有CLK

(3)非差分:因为I2C的通信速率不高,所以使用电平信号通信,而且通信双方距离很近,所以使用电平信号通信

(4)低速率:I2C一般是用在同一个板子上的两个IC之间的通信,而且用来传输的数据量也不大,所以本身通信速率很低(一般几百KHz,不同的I2C芯片的通信速率可能不同,具体编程的时候要看自己所使用的设备所允许I2C的最高通信速率,不能超过这个速率)

突出特征1:主设备+从设备

(1)I2C通信的时候,通信双方地位是不对等的,而是分为主设备和从设备。通信由主设备发起,由主设备主导,从设备只是按照I2C协议被动的接收主设备的通信,并及时响应。

(2)谁是主设备,谁是从设备是由我们通信双方来定的,I2C协议并没有规定,一般来说一个芯片可以只做主设备,也可以只做从设备,也可以既当主设备,也当从设备。

突出设备2:可以多个设备同时挂在一条总线上(从设备地址)

(1)I2C通信可以一对一(一个主设备对应一个从设备),也可以一对多(一个主设备对应多个从设备)

(2)主设备来负责调度总线,决定某一时间和哪个设备从设备通信,注意:同一时间内,I2C总线只能传输一对设备的通用信息。所以同一时间内,只能有一个从设备和主设备通信,而其他从设备处于“”“冬眠”状态,不能出来捣乱,否则通信就会乱套。

(3)每一个I2C从设备在通信中都会有一个I2C设备地址,这个设备地址是从设备本身固有的属性,然后通信时,主设备需要知道自己将要通信的那个设备的地址,然后在通信中通过地址来甄别是不是自己要找的那个从设备。(这个地址是一个电路板上唯一的,不是全球唯一的)

主要用途:SoC和周边设外设之间的通信(典型的如EEPROM、电容式触摸屏、各种sensor)

由I2C学通信时序

什么是时序?

时序:字面意思,时序就是时间顺序,实际上通信中的时序就是通信线上按照时间顺序发生的电平变化,以及这些变化对通信的意义就叫做时序。

I2C的总线空闲状态、起始位、结束位?

(1)I2C总线上有一个主设备,n(n》=1)个从设备。I2C总线上有两种状态,空闲态(所有设备都未和主设备通信,此时总线空闲)和忙状态(其中一个从设备在和主设备通信,此时总线被这一对占用,其他从设备必须歇着

(2)整个通信周期分为一个周期一个周期的,两个相邻的通信周期是空闲态。每一个通信周期由起始位开始,一个结束位结束,中间是本周期的通信数据。

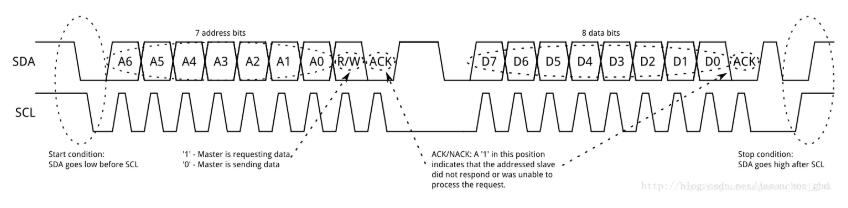

(3)起始位不是一个时间点,而是一个时间段。这段时间的总线状态的变化情况是:SCL线维持高电平,同时SDA线发生一个从高到低的下降沿。

(4)与起始位相似,结束位是一个时间段,在这段时间内总线的变化情况是:SCL线维持高电平,同时SDA线发生一个低到高的上升沿。

I2C数据传输格式(数据位&ACK):

(1)每一个通信周期的发起和结束都是由主设备来做,从设备只有被动的相应主设备,没法自己自发的去做任何事情。

(2)主设备在每个通信周期会先发8位的从设备地址(其实8位中只有7位是从设备地址,还有一位表示主设备下面是要写入还是读出)到总线(主设备是以广播的形式发送,总线上的所有的从设备都能收到这个广播),然后总线上的每个从设备都能收到这个地址,并且收到这个地址后,和自己的设备地址相比较看是否相等。如果相等说明主设备本次通信就是给我说话,如果不想等就说明本次通信与我无关,不用听不同管了。

(3)发送方在发送了一段数据后,接收方需要回应一个bit位,不能携带有效信息。只能表示2个意思(要么表示收到数据,即有效响应,要么表示未接到数据,即无效响应)

(4)在某一个通信时刻,主设备和从设备只能有一个在发(占用总线,向总线写),另一个一个在收(从总线读),如果主设备和从设备都试图向总线写,那就完蛋了,通信就乱套了。

数据在总线上的传输协议:

(1)I2C通信时的基本数据单位也是以字节为单位的,每次传输的有效数据都是一个字节(8位)。

(2)起始位及其后的8个clock中都是主设备在发送(这设备掌控总线),此时从设备只能读取总线,通过读取总线来得知主设备发给从设备的信息,然后到了第9个字节,按照协议规定,从设备需要发送ACK给主设备,所以这设备必须释放总线(这设备把总线置为高电平,不要动其实就类似于总线空闲状态),同时从设备试图拉低总线发出ACK。如果从设备拉低总线失败,或者从设备根本没有拉低总线,则主设备看到的现象就是总线在第9周期仍然一直保持高电平,这对于主设备来说,意味着我没收到ACK信号,主设备就会认为我刚刚发送的8字节不对(接收失败)。

S5PV210的I2C控制器:

通信双方本质上是通过时序工作,但是时序比较复杂,不利于SoC软件完成,因此,解决方案是SoC内部内置了硬件的控制器来产生通信时序,这样我们写软件时,只需要向控制器中写入配置值即可,控制器会产生适当的时序在通信线上和对方通信。

结构框图:

(1)时钟部分,时钟来源是PCLK_PSYS,经过内部分频最终得到I2C控制器的CLK,通信中这个CLK会通过SCL线传给从设备

(2)I2C总线控制逻辑(前台代表是I2CCON、I2CSTAT这两个寄存器),主要负责I2C通信时序。实际编程中要发送起始位、停止位。ACK等都是通过这两个寄存器(背后所代表电路模块)实现的。

(3)移位寄存器(shift regeist),将代码中要发送的字节数据,通过寄存器变成一个位一个位的丢给SDA线上去发送/接收。学过数字电路的同学应该对寄存器不陌生

(4)地址寄存器+比较器。本I2C控制器做从设备的时候用。

系统分析I2C的时钟:

I2C时钟源于PCL (PCLK_PSYS、等于65MHZ),经过了2级分频后得到的

第一级分频是I2CCON的bit,可以得到一个中间时钟I2CCLK(等同于PCL/16、PCLK/512)

第二级分频是得到I2C控制器工作的时钟,以I2CCLK这个中间时钟为源,分频系统位[1,16]

最终要得到时钟是2级分频后的时钟

主要寄存器I2CCON、I2CSTAT、I2CADD、I2CDS:

I2CCON+I2CSTAT:主要用来产生通信时序和I2C接口设置

I2CADD:用来写自己的slave address

I2CDS:发送/接收的数据都放在这里

I2C通信协议

1.I2C设备都有设备地址,可以多对多(多个主设备,多个从设备)

一对多:这种比较常见(我还没遇到过多对多,手动滑稽),也不会有太多问题

多对多:需要确保时钟(SCL)同步

2.SCL时钟速率不要高于从设备

数据传输步骤如下:

1.开始条件:SDA为高电平(1),SCL为高电平时(1),SDA由高向低跳变(下降沿)

2.发送数据:8个数据位,先传最高位(MSB),然后释放SDA线(1)(拉高电平)

SCL为低电平时(0),SDA可进行电平转换;

SCL为高电平时(1),SDA保持不变,接收设备(主设备或从设备)读取数据。

3.接收响应:ACK,在第九个周期(可以说是第九个数据位)

接收设备拉低SDA(0);

答复发送设备,接收完成;

4.结束条件:SDA为低电平(0),SCL为高电平时(1),SDA由低向高跳变(上升沿)

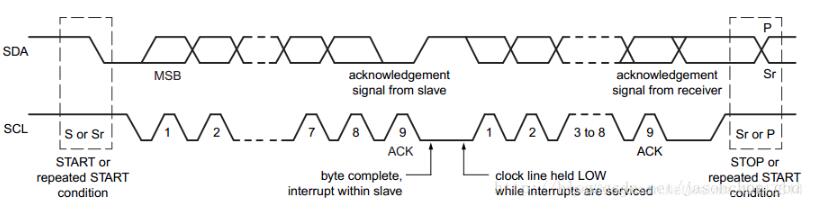

5.重复开始条件:master需要在一次通信中进行多次消息交换(例如与不同的slave传输消息,或切换读写操作)

开始和结束不一一对应,可以发送多次开始条件,然后只有一个结束条件

a. 主设备发送地址帧(地址+写),发送要读取的寄存器地址(如0xA0)

b. 主设备发送地址帧(地址+读),接收(0xA0)寄存器数据

6.时钟拉伸(clock stretching):

有时候,低速slave可能由于上一个请求还没处理完,尚无法继续接收master的后续请求,即master的数据传输速率超过了slave的处理能力。这种情况下,slave可以进行时钟拉伸来要求master暂停传输数据 —— 通常时钟都是由master提供的,slave只是在SDA上放数据或读数据。

而时钟拉伸则是slave在master释放SCL后,将SCL主动拉低并保持,此时要求master停止在SCL上产生脉冲以及在SDA上发送数据,直到slave释放SCL(SCL为高电平)。之后,master便可以继续正常的数据传输了。可见时钟拉伸实际上是利用了时钟同步的机制,只是时钟由slave产生。

如果系统中存在这种低速slave并且slave实现了clock stretching,则master必须实现为能够处理这种情况,实际上大部分slave设备中不包含SCL驱动器的,因此无法拉伸时钟。

所以更完整的I2C数据传输时序图为:

传输详细内容

1.地址帧(address frame):(用于master指明消息发往哪个slave)

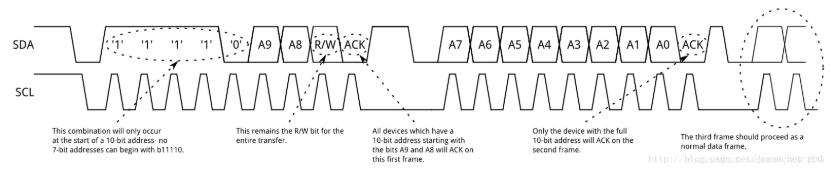

地址帧:7个地址位+1个读写位(0写1读),也支持10bit地址

地址位:确保芯片Datasheet给的是几位地址位,有的给的7位,有的给的8位(需要左移);直接给地址帧,带读/写

10bit地址帧:b1111 0XX(W/R)+bXXXX XXXX;

如下图所示

2.数据帧(data frames): 由master发往slave的数据(或由slave发往master),每一帧是8-bit的数据

3.根据 (1地址帧) 的读写位,确定发送/接收设备

写:和发送地址帧一样,主设备(发送),从设备(接收);

读:反过来,主设备(接收),从设备(发送);

后续的数据传输中,发送设备发送数据,接收设备需要发送ACK。

责任编辑:YYX

精彩阅读推荐:

-

I2C通信2016-04-22 0

-

3分钟理解通信协议之I2C总线 #通信协议硬声课堂 2021-10-18

-

I2C的通信问题2016-10-05 0

-

i2c通信协议2020-03-06 0

-

硬件I2C的说明2021-08-04 0

-

【龙芯1c库】封装硬件I2C接口和使用示例 精选资料分享2021-08-09 0

-

什么是软件I2C和硬件I2C2021-08-23 0

-

STM32硬件I2C重新编制I2C的通信流程2021-12-14 0

-

I2C通信协议的原理是什么2022-02-17 0

-

讲解一下STM32CubeMx的I2C配置2022-02-21 0

-

I2C通信详解2022-02-28 0

-

如何在PSOC和ST之间实现I2C通信?2023-01-17 0

-

AT32F423 I2C使用指南2023-10-26 0

-

I2C通信的详细讲解2021-06-25 132595

-

i2c总线是什么意思 i2c通信咋样 i2c通信的详细讲解2023-07-27 951

全部0条评论

快来发表一下你的评论吧 !