我们看看JTAG的最初用途,边界测试

描述

JTAG是1980年代开发的用于解决电子板制造问题的IEEE标准(1149.1)。如今,它可以用作编程,调试和探测端口。但是首先,让我们看看JTAG的最初用途,边界测试。

边界测试

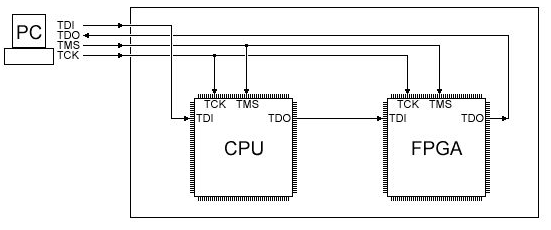

这是一个简单的电子板(也称为“印刷电路板”的“ PCB”),带有两个IC(“集成电路”),一个CPU和一个FPGA。典型的电路板可能具有更多的IC。

IC可以有很多引脚。因此,当然,IC通过大量连接(PCB traces)连接在一起。这里只显示四个。但是可以轻松地在PCB上放置几千个。

现在,如果您构建一千个板,每个板具有数千个连接,则不可避免地会有一些不良板。如何测试所有这些板?必须确保所有这些连接都正确。不能只手动测试所有这些连接。这样就创建了JTAG。

JTAG可以控制(or hijack)所有IC的引脚。在图片上,也许JTAG将使所有CPU引脚输出,以及所有FPGA引脚输入。然后,通过从CPU引脚发送一些数据,并从FPGA引脚读取值,JTAG可以确保电路板连接良好。

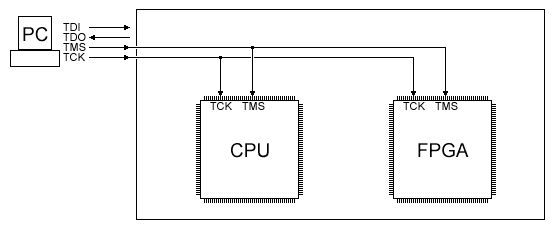

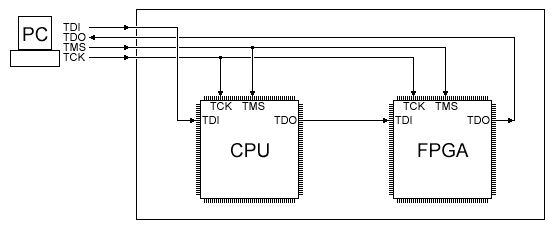

现在,JTAG实际上包含四个逻辑信号,分别为TDI,TDO,TMS和TCK。从PC的角度来看,这是三个输出和一个输入。

◇TCK:时钟信号,为TAP的操作提供了一个独立的、基本的时钟信号。

◇TMS:模式选择信号,用于控制TAP状态机的转换。

◇TDI:数据输入信号。

◇TDO:数据输出信号。

这四个信号需要以特定方式进行布线。首先,TMS和TCK与所有JTAG IC并联。

然后将TDI和TDO并连接起来,形成一条链。用JTAG术语,您经常会听到“ JTAG-chain”一词的来历。

如您所见,每个符合JTAG的IC都有四个用于JTAG的引脚(三个输入和一个输出)。名为TRST的第五个引脚是可选的(JTAG复位)。JTAG引脚通常是专用的(不共享用于其他目的)。

所有大型IC都使用通过JTAG进行的边界测试-边界测试是创建JTAG的最初原因。如今,JTAG的使用已得到扩展,以允许进行诸如配置FPGA之类的操作,然后在FPGA内核内部使用JTAG进行调试。

责任编辑:lq

-

边界扫描测试技术简介及原理2009-10-15 0

-

Cyclone IV器件的JTAG边界扫描测试2017-11-14 0

-

怎样才能使JTAG边界扫描与功能测试相结合2021-05-06 0

-

边界扫描测试技术介绍2022-02-17 0

-

JTAG边界扫描技术设计方案2010-03-04 439

-

基于JTAG边界扫描方式的重构控制器的设计2010-02-06 1185

-

边界扫描测试的原理及应用设计2016-02-16 509

-

Cyclone_IV器件的JTAG边界扫描测试2016-09-02 707

-

JTAG的先进经验和系统设计详析2018-05-22 608

-

ARM的JTAG调试结构2020-08-27 2895

-

一文详解JTAG2020-11-01 7256

-

看看JTAG的最初用途,边界测试2021-03-09 2286

-

JTAG(四) 边界扫描测试技术2021-12-20 641

-

什么是JTAG?用途是什么2022-10-17 8265

-

什么是边界扫描?JTAG边界扫描测试方案介绍2023-09-22 1756

全部0条评论

快来发表一下你的评论吧 !