资料下载

便携式IP核的WISHBONE片上系统SoC互连结构

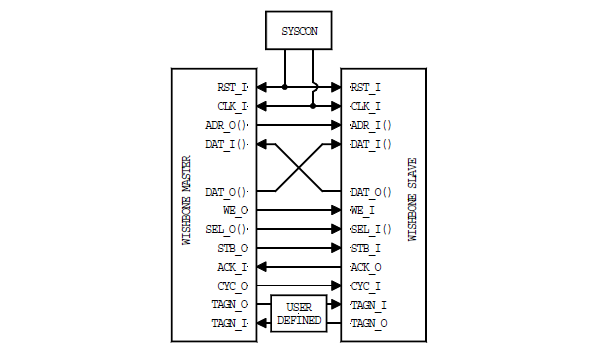

用于便携式IP核的WISHBONE1片上系统(SoC)互连结构是一种灵活的设计方法,可用于半导体IP核。其目的是通过缓解片上系统集成问题来促进设计重用。这是通过在IP核之间创建一个公共接口来实现的。这提高了系统的可移植性和可靠性,并缩短了最终用户的上市时间。

以前,IP核使用非标准的互连方案,这使得它们很难集成。

这需要创建自定义的粘合逻辑来将每个核心连接在一起。通过采用标准的互连方案,最终用户可以更快、更容易地集成核心。

本规范可用于软核、固核或硬核IP。由于硬核和硬核通常被认为是软核,所以本规范就是从这个角度编写的。

本规范不要求使用特定的开发工具或目标硬件。此外,它完全符合几乎所有的逻辑综合工具。然而,规范中给出的示例确实使用VHDL硬件描述语言。这些仅为方便读者而提供,其他硬件描述语言(如Verilog)的用户应易于理解。也可以使用基于原理图的工具。

叉形杆互连旨在作为通用接口。因此,它定义了IP核心模块之间的标准数据交换。它并不试图规范IP核心的特定于应用程序的功能。

WISHBONE建筑师受到三个因素的强烈影响。首先,需要一个好的、可靠的片上系统集成解决方案。第二,需要一个通用的接口规范来促进大型项目团队的结构化设计方法。

第三,他们对PCI总线和VMEbus等微机总线提供的传统系统集成解决方案印象深刻。

事实上,叉形杆结构类似于微型计算机总线,因为它们都:

(a) 提供灵活的集成解决方案,可以轻松地针对特定的应用程序进行定制;(b)提供各种总线周期和数据路径宽度,以解决各种系统问题;(c)允许各种供应商设计产品(从而降低价格,同时提高性能和质量)。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章