0101以太网简介以及SMI接口

电子说

描述

0101以太网简介

STM32F20X和STM32F21的以太网外设可接受和发送数据按照IEE802.3-2002标准。

以太网提供一个完整的、灵活的外设去满足不同应用和要求。它支持与外部相连(PHY)的两个标准的工业接口:默认情况使用在IEEE802.3规范中定义的独立介质接口(MII)和精简介质独立接口(RMII)。它可以被用于大量的需求,例如开关(交换机)、网络接口卡等等。

以太网满足下列标准:

● IEEE 802.3-2002,用于以太网MAC。

● IEEE 1588-2008 标准,用于规定联网时钟同步的精度。

● AMBA 2.0,用于AHB 主/从端口。

● RMII 联盟的 RMII规范。

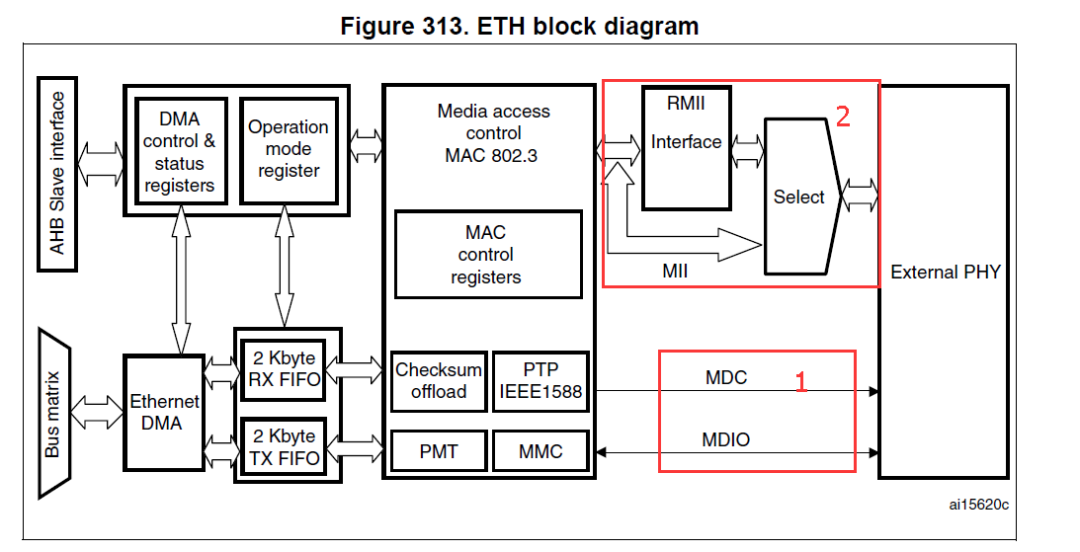

02 STM32F207的ETH介绍

STM32F207支持MII接口和RMII接口。STM32F207以太网外设包括一个MAC802.3(介质访问控制)和一个DMA控制器。它默认情况下支持MII和RMII接口,通过一个选择位进行切换(参考SYSCFG_PMC寄存器)。

DMA控制器通过AHB主从接口和内核与内存相连。AHB主接口控制数据传输,AHB从接口用于访问控制和状态寄存器(CSR)空间。

在MAC内核发送数据之前,数据经过DMA的方式发送到FIFO中缓存。同样的,接收FIFO存储通过线路收到的以太网数据帧,直到这些数据帧通过DMA被传输到系统内存。

以太网外设也包括一个SMI,用于和外部PHY通讯。通过一组寄存器的配置,用户可以选择MAC和DMA控制器的不同模式和功能。

当使用以太网时,AHB时钟必须至少25MHZ。

下面是ETH的框图

关于AHB的连接信息:

区域1:我们称为SMI接口,用于配置外部PHY芯片。

区域2:是数据交换接口,也就是上面我们说的MII接口和RMII接口。

03 SMI接口

3.1、站管理接口:SMI

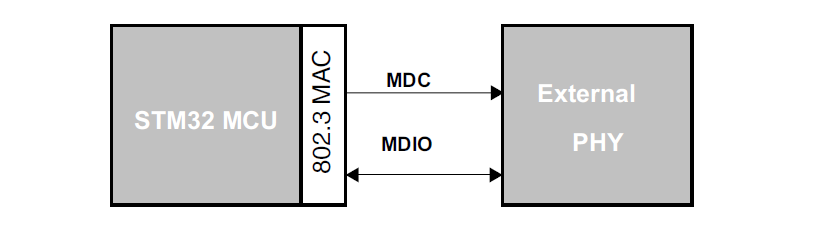

站管理接口允许任何PHY寄存器请求通过2线时钟和数据线。这个接口支持最多到32个PHY。

应用程序可以从 32个 PHY中选择一个PHY,然后从任意PHY 包含的32 个寄存器中选择一个寄存器,发送控制数据或接收状态信息。任意给定时间内只能对一个PHY 中的一个寄存器进行寻址。

MDC 时钟线和 MDIO数据线在微控制器中均用作复用功能I/O:

MDC:周期性时钟,提供以最大频率2.5 MHz 传输数据时的参考时序。MDC的最短高电平时间和最短低电平时间必须均为160 ns。MDC的最小周期必须为400 ns。在空闲状态下,SMI管理接口将 MDC时钟信号驱动为低电平。

MDIO:数据输入/输出比特流,用于通过MDC 时钟信号向/从PHY 设备同步传输状态信息。

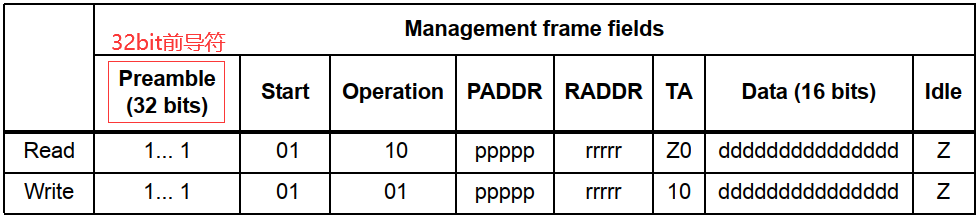

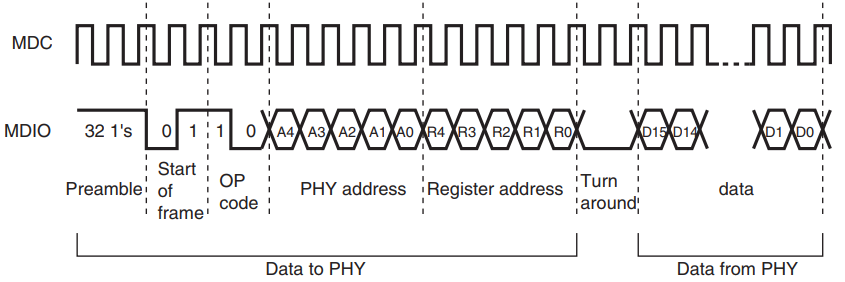

3.2、SMI帧结构

下图给出了读操作和写操作帧结构,位传输必须要求从左到右。

Preamble(32bit前导符):每个传输(读或者写)都必须以前导符开始,前导符是MDIO线上连续的32个逻辑’1’信号,和对应MDC线上的32个时钟信号。这部分信号用于和PHY设备建立同步。

Start(起始符):帧的起始符定义为’01’,也就是MDIO线从逻辑’1’降到’0’再回到’1’,以标记传输的。

开始。

Operation(操作符):用于定义操作的类型:读或者写。

PADDR:PHY的地址有5位,可以区分32个PHY。高位先被发送和接收。

RADDR:寄存器的地址有5位,可以寻址32个独立的寄存器。高位先被发送和接收。

TA:2位的转向符,插在RADDR和数据(DATA)之间,用于避免读操作时发生冲突。读操作时,在TA的这2位时间内,MAC控制器保持MDIO线的高阻状态,PHY设备则先保持1位的高阻状态,在第2位时输出’0’信号。写操作时,在TA的这2位时间内,MAC控制器驱动MDIO线输出’10’信号,而PHY设置则保持高阻状态。

DATA(数据):16位的数据域。最先发送和接收的是ETH_MIID寄存器的第15位。

空闲位:MDIO线保持在高阻状态。取消所有的三态驱动,由PHY的上拉电阻保证MDIO线处于逻辑’1’。

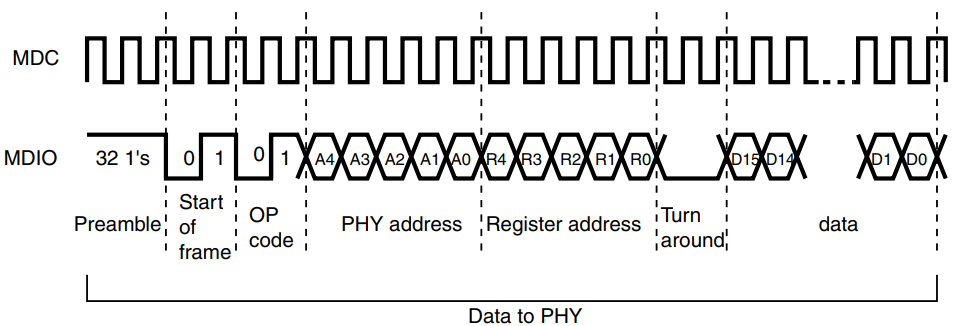

3.3、SMI写操作

当应用程序设置了MII写和忙位(以太网MACMII地址寄存器(ETH_MACMIIAR)),SMI接口会向PHY传 送 PHY地 址 和 PHY寄 存 器 地 址 ,然 后 传 输 数 据 (以 太 网 MAC MII 数据 寄 存器(ETH_MACMIIDR))。在SMI接口传输数据的过程中,不能修改MII地址寄存器和MII数据寄存器的内容;在此过程中(忙位为高),对MII地址寄存器或MII数据寄存器的写操作将被忽视,并且不影响整个传输的正确完成。当完成写操作时,SMI接口将清除忙位,告知应用程序。

下图描述了写操作时的帧格式。

3.4、SMI读操作

当程序把以太网MACMII地址寄存器(ETH_MACMIIAR)的MII忙位置为’1’,而保持MII写位为’0’,SMI接口则发送PHY地址和PHY寄存器地址,执行读PHY寄存器的操作。在整个传输过程中,应用程序不能修改MII地址寄存器和MII数据寄存器的内容。在传输过程中(忙位为高),对MII地址寄存器或者MII数据寄存器的写操作将被忽视,并且不影响整个传输的正确完成。在读操作完成后,SMI接口将清除忙位,并把从PHY读回的数据更新到MII数据寄存器中。

下图描述了读操作的帧格式

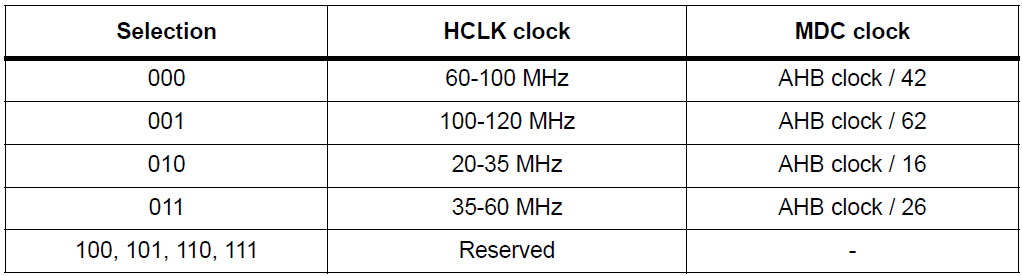

3.5、SMI时钟选择

MAC 启动管理写/读操作。SMI时钟是一个分频时钟,其时钟源为应用时钟(AHB时钟)。分频系数取决于MII地址寄存器中设置的时钟范围。这里既然说到了时钟,就再次提一下上文提到的内容:当使用以太网时,AHB时钟必须至少25MHZ。

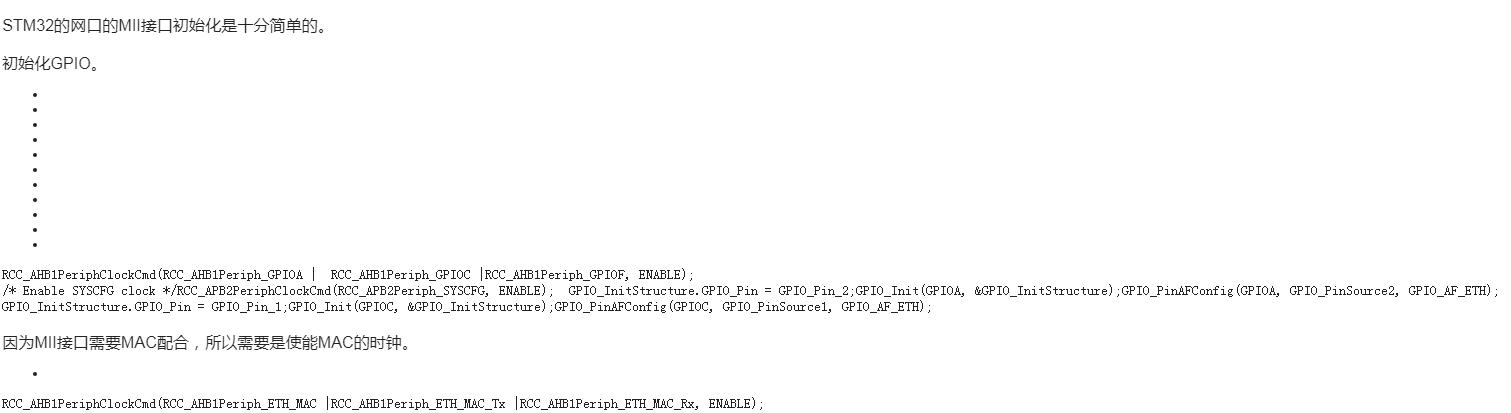

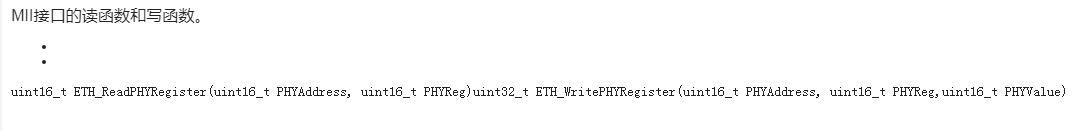

04 代码

责任编辑:xj

原文标题:STM32网络之SMI接口

文章出处:【微信公众号:嵌入式ARM】欢迎添加关注!文章转载请注明出处。

-

以太网是什么鬼?以太网基础知识详解电子学习 2023-02-07

-

69 67_以太网简介 - 第4节充八万 2023-08-19

-

车载以太网快速入门#车载以太网北汇信息POLELINK 2023-09-01

-

车载以太网的接口卡VN5650开箱视频来啦!#车载以太网北汇信息POLELINK 2023-09-04

-

Vector的车载以太网总线接口卡VN5000系列快速入门#车载以太网北汇信息POLELINK 2023-09-12

-

车载以太网基础培训——物理层简介#车载以太网北汇信息POLELINK 2023-09-18

-

车载以太网基础培训——车载以太网的链路层#车载以太网北汇信息POLELINK 2023-09-19

-

基于FPGA的万兆以太网接口的设计与实现2012-08-11 0

-

Verilog实现的以太网接口2012-08-15 0

-

以太网和工业以太网的不同2018-10-23 0

-

SMI接口是什么2021-07-29 0

-

stm32f103以太网通信2021-08-05 0

-

以太网简介2021-08-09 0

-

什么是以太网?2022-11-18 0

全部0条评论

快来发表一下你的评论吧 !