如何优化验证电子电路的设计流程

电子说

描述

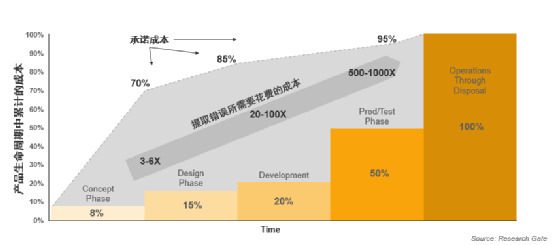

传统的流程将验证留给实验室样机测试,或发生在设计的最后阶段。然而在后期阶段才对设计进行整改将明显浪费成本和时间并且也没有办法对问题产生的原因进行根本性分析,或者寻找解决问题的方案。 这也让传统的仿真验证成为了电子电路设计项目开发过程中的一个难以突破的瓶颈。加速评审的唯一选择就是减少每个设计验证的覆盖率和次数。

重新设计造成的成本隐藏在产品的整个生命周期之中,据Lifecycle Insights的报告显示,平均每个项目会有2.9次的设计重制, 而平均每次设计重制,将会造成8.5天的项目延期,直接导致约44000美金的成本损失。除了这些确定的损失,产品生命周期中包含的潜在成本,例如后期的维护费用、品牌声誉、问题管理费用等等,都可能给整个项目开发的累积更高的成本。而导致重新设计的原因主要是:对设计仿真分析覆盖度不足,以及在人工评审时疏忽遗漏造成的。

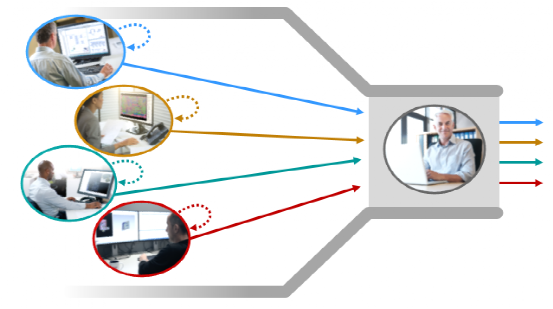

那么如何优化设计流程?设计工程师需要在将设计交付给分析专家之前进行多次的“内循环”,通过为分析专家“减负”来提高验证的吞吐量。在整个工程项目中,让仿真验证来驱动设计的更迭,而不是仅仅通过经验。

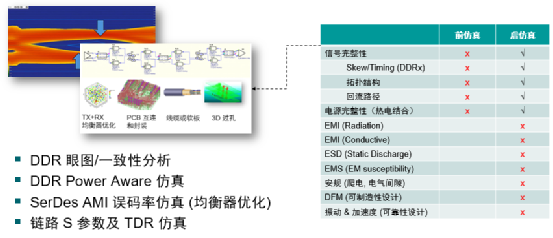

在传统的验证流程中,大多数公司仅对那些有明确目标的部分进行验证,比如 DDR 总线、部分 SerDes 差分线,重要芯片的PDN 阻抗等。但将仿真局限在这些范围中会让许多同样重要的问题被忽略,复杂设计中上千根的通用信号、电源网络爬电效应、PDN信号回路形成的天线效应等都是传统的仿真流程所不能覆盖的。

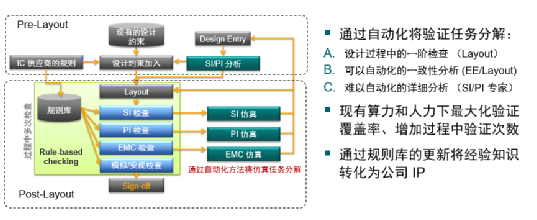

Siemens EDA 推荐使用混合验证流程解决仿真覆盖度和仿真效率的问题。通过自动化的手段将验证的工作拆分成多个部分,分别由团队中不同的工程师处理。通过自动化的平台,工程师将能够通过标准化的流程在设计过程中对项目进行高覆盖度、快速、多次迭代的仿真或验证,同时不会引入过多的学习成本。

如何从根本上优化仿真验证的流程,是系统设计者的一大挑战。

责任编辑:xj

原文标题:如何优化验证的设计流程,减少设计验证的覆盖率和次数?

文章出处:【微信公众号:电子发烧友网】欢迎添加关注!文章转载请注明出处。

-

模拟电子电路--视频版2009-09-25 0

-

模拟电子电路2010-05-06 0

-

【PDF】电子电路大全2011-03-02 0

-

实用电子电路2012-06-24 0

-

电子电路大全2013-04-07 0

-

重赏用晶闸管电子电路设计 求高人***2016-06-28 0

-

用可控硅电子电路设计 求高人***2016-06-28 0

-

如何对电子电路系统进行调测2021-08-06 0

-

电子电路集2006-03-15 1215

-

PSpice在电子电路优化设计中的应用2009-09-05 449

-

芯片验证分析及测试流程优化技术2011-06-29 1251

-

电力电子电路习题2016-01-08 719

-

电子电路设计原则_电子电路设计方法_电子电路设计步骤2019-09-26 18727

-

Testbench自动化验证方法介绍2023-09-04 507

-

电子电路仿真的意义和作用2024-04-21 438

全部0条评论

快来发表一下你的评论吧 !