先进工艺的提升能否延续摩尔定律?

电子说

描述

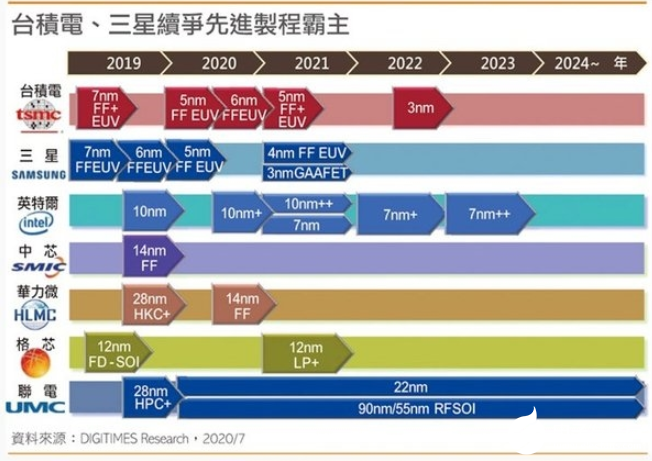

从苹果在2020年9月的iPad Pro上率先采用5nm工艺的A14 Bionic,随后华为、高通、三星也相继推出5nm工艺的旗舰级SoC。

WikiChips分析后估计,台积电5nm的栅极间距为48nm、金属间距30nm、鳍片间距25-26nm,单元高度约为180nm。

从而推算出台积电5nm的晶体管密度为1.713亿个每平方毫米,比初代7nm每平方毫米9120万个增加88%,台积电官方宣传的数字是84%。

第一款出货的5nm芯片,是苹果2020年10月份发布并上市的A14仿生芯片,这款SoC的晶体管数量达到118亿个,比A13多大约40%。

而且使6核CPU性能提升40%,4核图形GPU性能提升30%,功耗降低30%。

第二款华为麒麟9000则集成153亿个晶体管,8核CPU、24核GPU和NPU AI处理器,官方称CPU性能提升25%,GPU提升50%。

按照摩尔定律,芯片的晶体管数量每隔18-24个月翻一番,性能提升一倍。

但随着半导体技术逐渐接近物理瓶颈,晶体管尺寸的微缩越来越难。

从7nm推进到5nm的手机芯片的表现似乎并不尽人意,不仅在性能提升有限,功耗也面临“翻车”。特别是很多用户并不买5nm芯片的账,认为5nm手机芯片表现并没有达到预期。

外媒9to5Mac首先指出,部分iPhone 12用户在使用手机时遇到高耗电问题,待机一夜电量下降20%至40%,哪怕有没有开启更多的后台程序,结果不变。

工艺、IC设计与功耗的平衡

为什么5nm芯片翻车?主要原因是制造工艺不成熟。

在多数人眼中,芯片设计和制造工艺是互相独立的,但事实并非如此。制造工艺和IC设计不匹配时,便会造成一些问题,包括功耗、性能等。

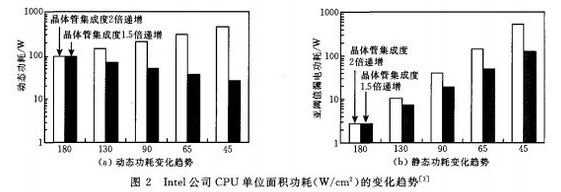

集成电路的功耗可以分为动态功耗和静态功耗。动态功耗通常指电路状态变化时产生的功耗,计算方法与普通电路的P=UI物理公式相同,动态功耗受到电压和电流的影响。

静态功耗即每个MOS管泄露电流产生的功耗,尽管每个MOS管产生的漏电流很小,但一颗集成上亿甚至上百亿晶体管的芯片,累计的芯片态功耗就会比较大。

在芯片工艺制程发展过程中,当工艺制程还不太先进时的动态功耗占比大,业界通过放弃最初的5V固定电压的设计模式,采用等比降压减慢功耗的增长速度。

减小电压意味着晶体管的开关会变慢,更加注重性能的厂商即便采用更先进的工艺,也依然保持5V供电电压,导致功耗增大。

由于对性能需求不同,也就产生了高性能和高能效两种产品。诸如桌面、服务器等高性能CPU、GPU,便采用5V供电电压,确保响应速度和性能。

也有厂商选择降低功耗,虽然会损失一部分性能,无需像高性能产品那般面对高功耗带来的一系列问题。

但对于普通用户来说,设备发热严重和高功耗会直接影响使用体验,芯片散热差严重时会导致芯片异常甚至失效。

所以半导体行业一直将低功耗设计视为芯片行业需要解决的问题之一,如何平衡先进节点下芯片的性能、功耗与面积(PPA)也是芯片设计与制造的挑战。

理论芯片制程越先进,使用更低的供电电压产生更低的动态功耗,但工艺尺寸进一步减小后,芯片的典雅来到0.13V以后便难以继续下降,也导致了近几年工艺尺寸减小时,动态功耗无法进一步下降。

静态功耗方面,场效应管的沟道寄生电阻随节点进步变小,在电流不变的情况下,单个场效应管的功率也变小。但另一方面,单位面积内晶体管数目倍速增长又提升静态功耗,因此最终单位面积内的静态功耗可能保持不变。

厂商为追求更低的成本,用更小面积的芯片承载更多的晶体管,看似是达成制程越先进、芯片性能越好、功耗越低。

但实际情况更复杂,有的厂商通过增加核心、也有通过设计更复杂的电路,无论是增加核心还是设计更复杂的电路,都需要面对功耗激增的问题,两者之间又需要寻找新方法进行平衡。

晶体管结构的升级

国际商业战略IBS公司主席兼CEO就曾表示,传统Bulk CMOS工艺技术将在20nm走到尽头,必须用创新的思路和方法寻找新的替代工艺。

胡正明教授在2020年提出全耗尽型绝缘体上硅(FD-SOI)工艺;目前行业广泛采用鳍式场效应晶体管(FinFET)则是1999年发明。

FinFET工艺很好的平衡了20nm至5nm之间的芯片性能与功耗,类似于鱼鳍式的架构控制电路的连接和断开,改善电路控制并减少漏电流,晶体管的沟道也随之大幅度缩短,静态功耗随之降低。

Moortec首席技术官曾接受外媒体采访时称:当制造工艺升级到16nm或14nm时,处理器速度的到很大的提高,而且漏电流也下降得比较快,以至于我们在使用处理器时能够用有限的电量做更多的事情。

但从7nm升级到5nm的过程中,漏电情况几乎与28nm水平相同,以至于厂商需要重新平衡功耗和性能之间的关系。

Cadence的数字和签准组高级产品管理总监Kam Kittrell也曾表示,很多人都没有弄清能够消耗如此多电能的东西,他们需要提前获取工作负载的信息才能优化动态功耗。

长期以来,我们一直专注于静态功耗,以至于一旦切换到FinFET节点时,动态功耗就成为大问题。另外多核心的出现也有可能使系统过载,因此必须有更智能的解决方案。”

IC设计公司、制造公司在5nm节点上面临相同的问题,也是这几款5nm芯片集体“翻车”的根本。

不成熟的IC设计或制造工艺,都会影响性能与功耗的最大化折中。虽然不排除IC设计公司为追求更好的性能,牺牲功耗。

在FinFET工艺之后,环绕式闸极电晶体(GAA)也开始提上议程,台积电原本计划在5nm节点上应用该技术,但考虑到综合性能和成本之后,选择继续使用FinFET工艺。

让GAA的应用推迟至3nm节点上(4nm节点为5nm改良版),外界对于功耗、性能的平衡并不了解。

高昂的晶圆设计和制造成本

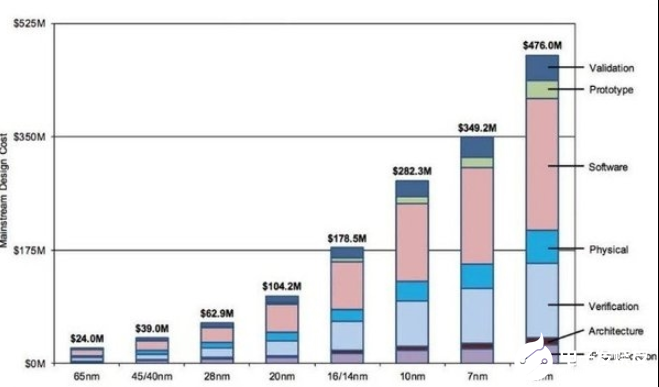

除了功耗和性能之间的平衡外,越先进工艺的晶圆设计费用和制造成本更高。

根据市场研究机构给出的数据显示,65nm工艺的设计成本需要2400万美元,28nm工艺则需要6290万美元,7nm和5nm分别达到3.49亿与4.76亿美元。

此外,三星也曾对外称其3nm GAA的成本可能会超过5亿美元,预期在2022年大规模,讲采用比FinFET更先进的GAAFET 3nm制程芯片。

编辑点评:随着5nm工艺“翻车”,外界对先进制程的怀疑态度又增一分,首先是先进工艺的性能提升已经难以满足“摩尔定律”的延续。

高昂的设计成本和制造费用,同样制约着先进制程的未来,目前采用5nm工艺的都是顶级IC设计公司。

对于半导体越来越接近物理极限,摩尔定律还能持续多久?

责编AJX

-

小芯片能否“续写”摩尔定律?电子学习 2023-02-08

-

摩尔定律也适用于EPON芯片商用之路?2011-09-27 0

-

半导体行业的里程碑“摩尔定律”竟是这样来的2016-07-14 0

-

摩尔定律在测试领域有哪些应用?2021-04-13 0

-

请问摩尔定律死不死?2021-06-17 0

-

摩尔定律,摩尔定律是什么意思2010-02-26 1509

-

摩尔定律_摩尔定律是什么2012-05-21 2751

-

延续摩尔定律,英特尔强推新制程2016-05-16 1745

-

摩尔定律的历程2017-10-24 1906

-

台积电谈如何延续摩尔定律!2020-01-28 3420

-

扇出型晶圆级封装能否延续摩尔定律2020-11-12 776

-

2nm芯片符合摩尔定律吗 摩尔定律能够延续下去吗2022-07-05 1347

-

后摩尔定律时代,国产EDA如何“从0到1”做创新?2022-08-16 2065

-

摩尔定律不会死去!这项技术将成为摩尔定律的拐点2023-11-03 287

-

功能密度定律是否能替代摩尔定律?摩尔定律和功能密度定律比较2024-02-21 209

全部0条评论

快来发表一下你的评论吧 !