资料下载

×

如何使用FPGA实现JPEG解码算法的研究与实现论文免费下载

消耗积分:0 |

格式:rar |

大小:3.42 MB |

2021-01-29

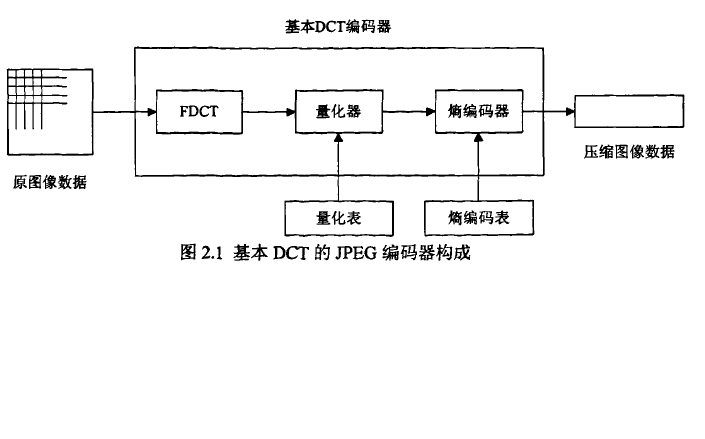

在多媒体通信技术中,JPEG以其对静止图像的优良的压缩特性获得了广泛应用,成为国际通用的标准。本文在简要介绍JPEG标准和FPGA(Field Programmable Gate Array,现场可编程门阵列)设计流程的基础上,从总体规划的角度提出了整个系统结构的设计思想,对JPEG解码器各部分算法进行了深入的研究,接着对各个模块的设计进行了详细的描述。采用了Verilog硬件描述语言对JPEG基本模式硬件解码器的各主要模块进行设计实现,并给出了功能仿真波形图及测试结果。在JPEG图像解码器中,二维IDCT(离散余弦逆变换)单元在整个解码过程中消耗的时间占了很大的比例,因此提高二维IDCT变换的速率显得很有必要,本文利用行列分解的方法实现二维IDCT变换,有效地减少了二维IDCT单元的运算时间。将反Zig-Zag扫描集成到了反量化器上,节约了反量化和反Zig—Zag扫描的时间。基于JPEG标准中Huffman码表的规律提出并行熵解码的算法,实现了快速Huffman解码。本课题的JPEG解码器的设计与实现,为复杂的图像解码器在FPGA上实现做了探索性的尝试,对其他的图像解码系统的IP核设计以及FPGA实现有着积极的借鉴意义。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章