【紫光同创国产FPGA教程】【第六章】PDS下按键消抖实验

描述

原创声明:

本原创教程由芯驿电子科技(上海)有限公司(ALINX)创作,版权归本公司所有,如需转载,需授权并注明出处(http://www.alinx.com)。

适用于板卡型号:

PGL22G/PGL12G

1. 文档简介

本文主要讲解按键消抖原理及程序编写,程序实现按键按下后数字加1,并在led出来,通过PDS软件编译调试。

2. 实验环境

-

Windows 10 64位

-

Pango Design Suite 2020.3

-

开发板

3. 实验原理

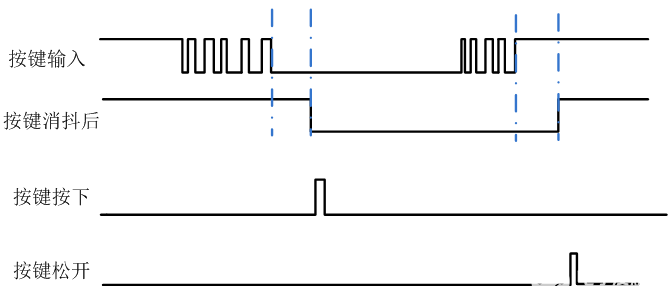

按键做为基本的人机输入接口,在很多电子设计中都能见到,由于机械特性,在按键按下或松开的时候,按键输入值是有抖动的,无论按下去是多平稳,都难以消除抖动,按键消抖方式有很多,本实验主要是通过FPGA计时来消抖。实验中设计了一个计数器,当按键输入有变化时,计时器清零,否则就累加,直到加到一个预定值(例如10ms),就认为按键稳定,输出按键值,这样就得到以后没有抖动的按键值。由于在很多地方需要用到按键下降沿或上升沿的检测,按键消抖模块直接集成了上升沿和下降沿检测的功能。

4. 程序设计

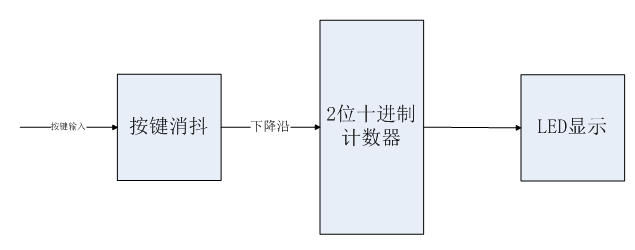

如下图所示,通过按键消抖后,在按键按下时,十进制计数器加1,通过数码管译码扫描后显示出来。

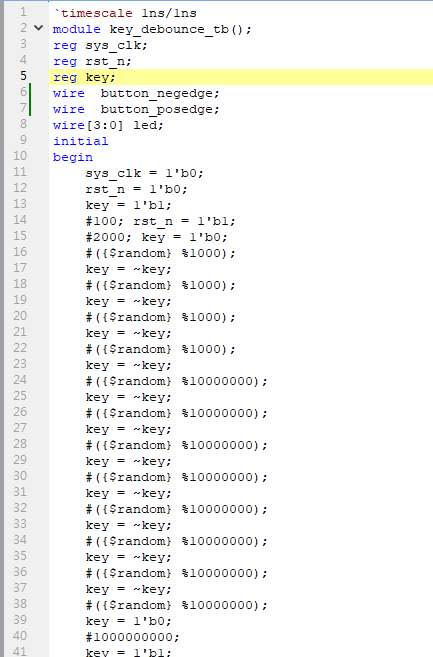

按键消抖部分的原理在上节已经讲过,按键消抖部分代码写的非常精炼,阅读起来稍显费解,建议结合仿真波形去读代码。在提供的例程文件下的src文件夹中同时提供了仿真文件key_debounce_tb.v,可以通过添加仿真文件来进行仿真观察代码中信号的变化

| 信号名称 | 方向 | 说明 |

| clk | in | 时钟输入 |

| rst_n | in | 异步复位输入,低复位 |

| button_in | in | 按键输入 |

| button_posedge | out | 消抖后按键上升沿,高有效,1个时钟周期 |

| button_negedge | out | 消抖后按键下升沿,高有效,1个时钟周期 |

| button_out | out | 消抖后按键输出 |

按键消抖模块(ax_debounce)端口

LED显示部分在本章不做说明,就例程中按键消抖模块“ax_debounce”模块做一些讲解,模块中通过了两级D触发器来寄存键值,只有当键值稳定时才将键值输出。我们可以看到在assign赋值语句中有一条“assign a_reset=(DFF1 ^ DFF2)”,学过数字电路的应该都知道“ ^ ”是异或运算符,运算符两边相同运算结果为0, 不同运算结果为1。在程序中DFF1和DFF2比较运算后的值通过“assign”赋给“a_reset”表示比较锁存键值的前后两级寄存器的值是否一致,只有前后两级寄存器的值一致,也就是a_reset的值为0时才表示当前锁存的键值没有变化。当计数器累加到“TIMER_MAX_VAL”,表示锁存的键值已经稳定可以输出。另外在模块中我们可以看到“{.......}”符号,要注意这可不是大括号,这表示位拼接运算符,其作用是将运算符内的两位,或是多位信号拼接在一起,具体用法请参考例程。

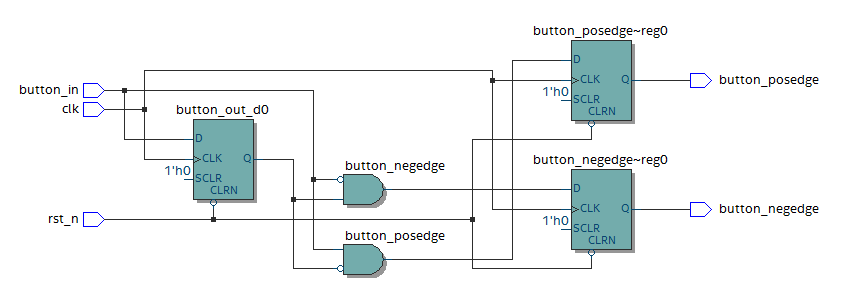

最后,程序中需要说明的是“button_posedge”和“button_negedge”两个输出信号,这是一种常用的上升沿和下降沿的采集方法,其描述的RTL视图如下:

当然还有其他的边沿检测电路的描述方法,但是其基本原理都是在逻辑时序电路里先将需要检测的信号作为输入非阻塞赋值给一个自定义寄存器,通过判断前后两级寄存器的值来判断是上升沿或是下降沿,由0 ->1 变化是上升沿,由1 -> 0变化是下降沿;

5. Modelsim仿真

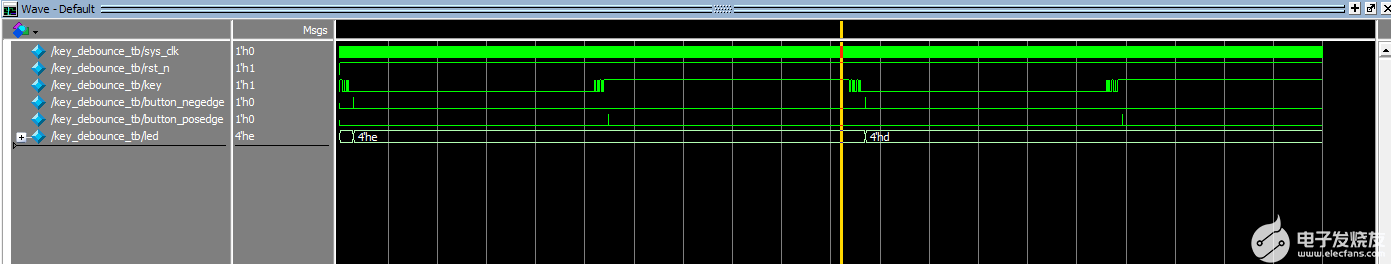

$random生成随机数模拟按键抖动,按下按键对应输出二进制数据加一。按键的按下和释放经消抖后会得到一个稳定的下降沿和上升沿。仿真结果和部分仿真文件如下图所示:

button_negedge为按键经过消抖后按键的下降沿,button_posedge为按键经过消抖后按键的上升沿。

6. 实验现象

开发板上电后下载程序,按下“KEY2”按键,可以看到4个LED会变化,对应二进制数据,按一次加一,如果不经过消抖,是无法实现按一次加一的。

开发板操作

-

求王庆利《单片机设计标准教程》第六章的一个函数!!2013-05-05 0

-

国产FPGA介绍-紫光同创2024-01-24 0

-

【紫光同创盘古PGX-Nano教程】——(盘古PGX-Nano开发板/PG2L50H_MBG324第二章)按键消抖实验例程2024-04-28 0

-

fpga教程之——按键消抖2012-02-27 0

-

数据采集光盘实例第一章至第六章2012-06-28 0

-

数据采集光盘实例第六章至第十二章2012-06-28 0

-

【ALIENTEK 战舰STM32开发板】STM32开发指南--第六章 跑马灯实验2013-01-10 0

-

《测控电路》习题完整参考答案(第六章)2017-05-07 0

-

【视频教程】紫光同创FPGA教程@PDS软件使用流程2023-06-12 0

-

从零开始学习紫光同创FPGA——PGL22G开发板之按键消抖(二)2023-06-15 0

-

【紫光同创国产FPGA教程】【PGC1/2KG第二章】LED 流水灯实验例程2023-08-09 0

-

【紫光同创国产FPGA教程】【PGC1/2KG第三章】键控彩灯实验例程2023-08-09 0

-

数字信号处理 第六章2017-10-19 575

-

静噪基础第六章_EMI静噪滤波器2018-01-24 949

-

【紫光同创国产FPGA教程】【第三章】按键检测实验2021-02-02 4128

全部0条评论

快来发表一下你的评论吧 !