资料下载

PCB设计十大误区-绕不完的等长(一)

作者:吴均 ,一博科技高速先生团队队长;来源:高速先生微信公众号

1.关于等长

第一次听到“绕等长工程师”这个称号的时候,我和我的小伙伴们都惊呆了。每次在研讨会提起这个名词,很多人也都是会心一笑。

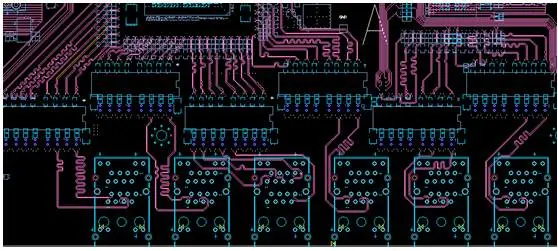

不知道从什么时候起,绕等长成了一种时尚,也成了PCB设计工程师心中挥不去的痛。需要等长设计的总线越来越多,等长的规则越来越严格。5mil已经不能满足大家的目标了,精益求精的工程师们开始挑战1mil,0.5mil……还听过100%等长,没有误差的要求。

为什么我们这么喜欢等长?打开PCB设计文件,如果没有看到精心设计的等长线,大家心中第一反应应该是鄙视,居然连等长都没做。也有过在赛格买主板或者显卡的经验,拿起板子先看看电容的设计,然后再看看绕线,如果没有绕线或者绕线设计不美观,直接就Pass换另一个牌子。或许在我们的心中,等长做的好,是优秀PCB设计的一个体现。

做过一个非正规的统计(不过一博每年上万款PCB设计,我们的采样基本上也可以算做大数据了),稍微复杂一点的高速板子,绕等长要占据总设计时间的20%~30%。如果等长规则更严格,或者流程控制不好,做了等长之后再反复修改,这个时间还会更多。

2.那些年,我们一起绕过的等长

培训的时候,我们经常会玩一个游戏,游戏的名字叫做:那些年,我们一起绕过的等长……

说到等长要求,先说说什么是“裕量”哈。“裕量”是设计时保留的安全间距,百度百科的解释更简单:多出来一部分,就称之为裕量。到底要多多少,什么才是安全,那就见仁见智了。每个人的安全感不同,对“裕量”的定义就不一样。但是在时序设计的时候,有一个现象比较普遍,那就是裕量层层放大,比如产品经理可能要求等长范围是±100mil,项目经理可能就会更严格到±50mil,然后到具体的实施工程师,可能就变成±5mil了。碰到一些“安全感”不足的工程师,那就恨不得是完全等长,没有偏差。

所以,后面的讨论里面,我们不会太多纠结在等长到底是10mil还是±5mil,我们集中精力来看看哪些等长是没有必要的,哪些等长反而破坏了系统的时序设计要求。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章