硬件乘法器原理_硬件乘法器电路结构

电子常识

描述

硬件乘法器原理

硬件乘法器的实现本质是“移位相加”。对于二进制,乘数和被乘数的每一位非0即1,相当于乘数中的每一位分别和被乘数的每一个体位进行与运算,并产生其相应的乘积位。这些局部乘积左移一位与上次的和相加。即从乘数的最低位开始,若其为1,则被乘数左移一位并与上一次的和相加;若为0,左移后以全零相加,如此循环至乘数的最高位。

硬件乘法器,其基础就是加法器结构,它已经是现代计算机中必不可少的一部分。 乘法器的模型就是基于“移位和相加”的算法。在该算法中,乘法器中每一个比特位都会产生一个局部乘积。第一个局部乘积由乘法器的LSB产生,第二个乘积由乘法器的第二位产生,以此类推。如果相应的乘数比特位是1,那么局部乘积就是被乘数的值,如果相应的乘数比特位是0,那么局部乘积全为0。每次局部乘积都向左移动一位。

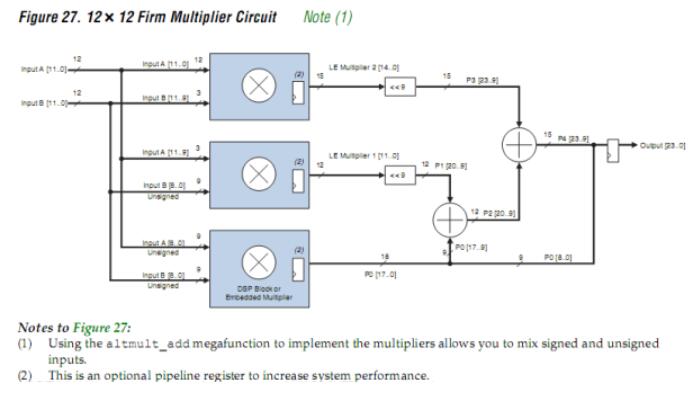

硬件乘法器电路结构

从理论上讲,两个二进N位操作数相乘,乘积的总宽度为2N,因此需要一个宽度为2N的移位寄存器和加法器。但在dao实际执行过程中,一是每个部分积的宽度和移位相加的有效宽度都为N位,从资源的利用率角度考虑,仅需N位宽度的加法器即可;二是按照先移位再相加的原理,两个N位操作数则需要2N个时钟周期才能完成整个运算,在此考虑将移位和相加两个运算步骤合并,从速度上就可在N个时钟周期内完成。

根据上述分析,8位移位相加型硬件乘法器应包括16位锁存器、8位移位寄存器、8位乘法器、8位加法器等4个组成部分。具体电路结构如图1所示。

锁存器发挥着锁存的作用,用于锁存部分和。

移位寄存器则具备移位作用,当加载信号有效时乘数将加载于8位右位寄存器,随着时钟上升沿的到来,乘数即由低位开始逐位移出。

乘法器功能类似一个特殊的与门。有两个输入端口,一个端口用于输入8位并行操作数(被乘数),另一个端口在时钟信号控制下输入由移位寄存逐步移出的串行操作数,并将这两个操作数进行与运算。

加法器用于将本次时钟脉冲控制下得到的8位部分积与锁存于锁存器高8位的前一个时钟脉冲下得到的部分和相加。

责任编辑:YYX

-

硬件乘法器2015-11-03 0

-

怎么设计基于FPGA的WALLACETREE乘法器?2019-09-03 0

-

硬件乘法器的相关资料分享2021-12-09 0

-

硬件乘法器是怎么实现的?2023-09-22 0

-

乘法器的基本概念2010-05-18 13500

-

1/4平方乘法器2010-05-18 1815

-

脉冲-宽度-高度调制乘法器2010-05-18 1821

-

N象限变跨导乘法器2010-05-18 1578

-

变跨导乘法器2010-05-18 1115

-

乘法器在通信电路中的应用2010-05-18 1279

-

基于IP核的乘法器设计2011-05-20 837

-

乘法器2016-12-01 1092

-

硬件乘法器是什么?2018-05-11 8571

-

使用verilogHDL实现乘法器2018-12-19 10518

-

乘法器原理_乘法器的作用2021-02-18 24740

全部0条评论

快来发表一下你的评论吧 !