采用全差分结构和增益自举运算放大器实现采样/保持电路的设计

描述

作者:张奉江,张红,张正璠

采样/保持电路是模数转换器的重要组成部分,它的性能决定着整个A/D转换器的性能。随着科学技术的发展,系统对A/D转换器的速度和精度要求越来越高,因此,设计一个高性能的采样/保持电路就显得尤为重要。

一般的采样保持电路都是采用开关电容电路来实现的。由于MOS开关固有的电荷注入与时钟馈通效应,采样/保持电路一般难以得到理想的情况。尽管已经提出了许多技术和电路结构但是电荷注人和时钟馈通效应所导致的非线性对电路性能的影响还是很大。

采样/保持电路的另外一个设计难点在于运算放大器的设计。采样/保持电路的精度决定于放大器的增益,高增益的运算放大器能够保证采样/保持电路达到很高的采样精度。而采样保持电路的速度则决定于运算放大器的带宽,高带宽的运算放大器能够保证采样/保持电路在很短的时间内达到所需的采样精度。而运算放大器的增益和带宽又是一种相互制约的关系。 本文介绍的采样/保持电路采用全差分结构,并通过底板采样技术有效的抑制电荷注入和时钟馈通效应 它采用高性能的增益自举运算放大器来减小由于有限增益和不完全建立带来的误差。该采样/保持电路在3.3V的电源电压下可实现60MHz的采样频率,其采样精度可以达到10位以上,完全能适用流水线AD转换器的采样部分。

1 增益自举运算放大器的设计

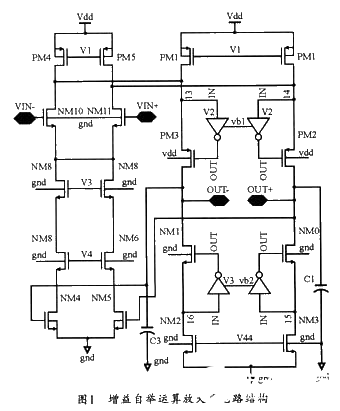

实际上,两级运算放大器可能有较大的增益,但是带宽却很小,这样就很容易导致较慢的反应速度。所以本文采用折叠式共源共栅增益自举运算放大器。这种放大器既有较大的增益,又能满足速度要求,同时,折叠式共源共栅电路还可以接成跟随器的形式。由于该电路不需要外接复杂的共模反馈电路(CMFB),因而可以降低功耗,并免去外加共模反馈电路对整个运算放大器速度的影响。图1所示是增益自举运算放大器的电路结构。

摆率Slew Rate(SR)是每个时钟周期所允许的扰动时间。通常,采样保持电路中对运算放大器的建立时间要求大约为时钟周期的1/8,即要求运算放大器的输出能够驱动0.3 Vpp(Vpp为信号满摆幅的一半),因此,建立时间可以由以下公式估算,其中Ts是建立时间,fs是采样频率:

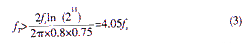

对于单位增益频fT的估算,首先应计算出采样/保持电路分别在采样和保持状态下的反馈系数Bt和Bh。假设信号在建立时间之后的1LSB之内出现,那么,所需精度P在N=10的时候为:

由采样保持电路可知Bt≈1,Bh≈0.8。由此 可以得出:

此时若运算放大器的直流增益为A0,那么, 线性建立误差系数为:

因为E必须小于1/2LSB,所以有:

开关电容电路中一般的相位裕度要求为60到75度之间。而电路设计中希望尽量做到线性建立,所以一般要求具有较大的相位裕度。但是,考虑到相位裕度与增益的矛盾,在折中考虑的情况下,本设计选择的相位裕度为70度左右。

运算放大器的总增益同时得益于的增益提升放大器的应用。由于增益提升放大器会带入额外的电容和极点,所以要求增益提升放大器的单位增益带宽应尽量做大,这样才能把它对整个放大器频率特性的影响降到最小。因此,这里选择一般的反向器作为增益提升电路。事实上,该提升电路结构也比较简单,它即可以满足电路对增益的要求,又可以达到满意的单位增益带宽。因而对整个电路的频率性能不会产生很大的影响。

本设计让晶体管NM4和NM5工作在线性区,这相当于一个压控电阻的作用。晶体管的栅极连到运算放大器的输出端。由于VOUTCM对V4比较敏感,而且随着V4的增加,NM5和NM6的电流也将随之增加,从而将导致共模电平的下降。而通过晶体管NM4和NM5则可纠正这个误差。这就相当于在运算放大器的输出端施加一个稳定的共模电平。

2 采样开关的设计

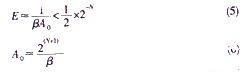

AD转换器和采样/保持电路中通常都会用到很多的开关。因此,开关的大小、宽长比以及所影响到的电荷注入效应和时钟馈通效应等都会直接影响到整个电路的性能。 开关的导通电阻是衡量一个开关特性好坏的重要指标。由MOS管的工作原理可知,其导通电阻RON是VGS的函数。对于一般的单个MOS管作为开关的情况,其实际的导通电阻可以通过以下等式得出:

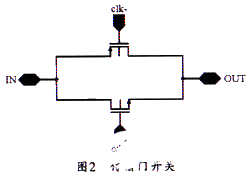

由上式可以看出:开关的导通电阻与输入信号Vgs是非线性关系。这一特性将在输出信号中引入谐波失真,从而极大地影响到采样电路的动态特性。本文采用的对称CMOS开关由一个PMOS和NMOS晶体管组成。其电路如图2所示。设计时,可将NMOS的栅极接高电位VDD,PMOS的栅极接低电位(零),此时开关处于导通状态。在对称CMOS开关中,PMOS管和NMOS管的导电因子Kp和Kn是相同的。假设导通电阻的非线性特性可由下式来描述:

那么,从上式可以得出:

式中,I是通过开关的电流。假设一个正弦波加在开关的两边,则开关上的电压为:

开关的三阶效应会使电路的SFDR下降。由上式可知,三阶效应是由最后一项产生的。R2为零即可消去这一项。而优化对称CMOS晶体管的宽、长参数可以使R2为零,从而使对称开关的导通电阻基本恒定且与输入信号无关。在本设计工艺条件下,通过对开关的仿真可知,当PMOS管的宽长比是NMOS管宽长比的8倍时,开关的导通电阻较小且与输入信号基本无关。

3 采样保持电路设计

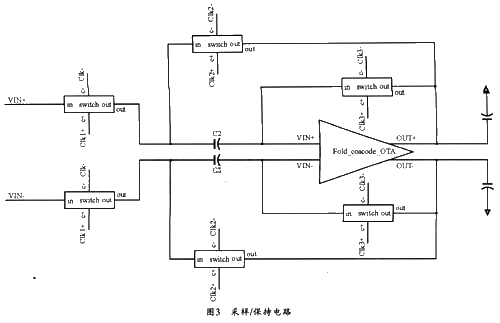

采用全差分采样/保持电路的电路结构如图3所示。它主要包括采样/保持放大器和一些开关电路。该电路结构采用输出端直接反馈到输入端的方式,它不需要外加共模反馈电路。这样可以减小电路复杂程度,有效地降低功耗,并可获得更高的速度。

为了获得更好的性能,此电路采用了底板采样技术。传统的采样保持/电路采用的是电容上极板采样。这种结构的采样保持电路会引入额外的寄生电容,从而增加运算放大器的输入电容,而这将大大降低运算放大器的带宽,同时也增大了采样与反馈电容值的失配,这些都会直接影响到采样保持/电路的速度和精度。为此,本电路引入底板采样技术,设计时可使用两层多晶硅来实现。这样不仅有效地消除了运算放大器的输入电容,而且还能抑制来自衬底的噪声。此外,该电路结构能够有效地抑制时钟馈通和电荷注入效应,减小电路复杂程度,有效减小寄生电容、降低电路的整体功耗。

4 性能仿真

笔者在Cadence仿真环境下,采用Charter公司0.35μm标准CMOS工艺库对电路进行了仿真。图4给出了增益自举运算放大器在交流扫描下的增益和相位曲线。可以看出,该运算放大器的增益可以达到79dB,当负载电容为10 pF时,相位裕度为72°,建立时间为3.9 ns。可见,能很好的满足采样保持/电路对运算放大器的要求。

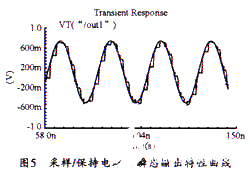

该采样/保持电路的电源电压为3.3 V,采样频率为60 MHz。图5是该采样/保持电路的瞬态特性曲线图。实际上,对该电路的输出波形进行离散傅立叶变换可得到低于-75 dB的信噪比。可见该采样/保持电路具有很高的转换精度。

5 结束语

本文介绍了一个高性能采样/保持电路的设计方法。该电路采用全差分结构来减小时钟馈通效应和电荷注入效应所带来的误差。开关部分使用优化的对称CMOS开关来降低其导通电阻。运算放大器则使用折叠式增益自举电路,以便在获得较高增益的同时,得到较快的建立时间。版图设计采用噪声分析法来选择合适的采样电容,以提升整体电路的信噪比。仿真证明:该电路在3.3V电源下,其采样频率为60 MHz,并可达到10位以上的采样精度,而电路的功耗仅1 2 mW。完全可以适用高速高精度流水线型A/D转换器的需要。

责任编辑:gt

-

什么是运算放大器和比较器?2019-04-23 0

-

运算放大器和比较器的电路结构2019-04-26 0

-

经典架构新玩法:用单端仪表放大器实现全差分输出2019-10-08 0

-

放大器教程:运算放大器基础学习2020-12-25 0

-

环路增益对运算放大器电路有什么影响?2021-04-12 0

-

求一种低电压全差分套筒式运算放大器的设计方法2021-04-14 0

-

如何设计一个适用于12bit流水线ADC采样保持电路?2021-04-20 0

-

请问怎么设计一种单级全差分增益增强的折叠共源共栅运算放大器?2021-04-20 0

-

请问采样保持电路的结构分为哪几种?2021-04-20 0

-

常规运算放大器的自举电路设计2021-09-13 0

-

交叉连接技术保持仪表放大器实现全差分输出2021-10-15 0

-

一种100MHz采样频率CMOS采样/保持电路2010-05-24 661

全部0条评论

快来发表一下你的评论吧 !