英特尔展示了其基于nanoribbon板状纳米沟道的n/p型堆叠的器件

电子说

描述

在IEDM 2020上,英特尔展示了其基于nanoribbon板状纳米沟道的n/p型堆叠的器件,这种器件结构与IMEC研发制备的CFET结构近似,被认为是3nm之后晶体管结构的必然解决方案。

研究背景

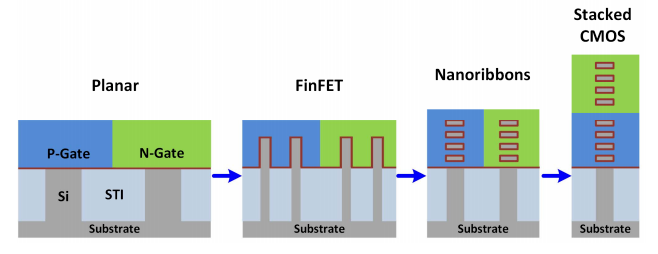

在先进逻辑集成电路的制造工艺进入10nm后,单纯依靠缩小器件工艺单元尺寸已经无法获得足够的能效增益。在28nm向下前行的过程中,从平面CMOS工艺到FinFET工艺的转变带来了更强的沟道控制能力,同时缩小了栅极间距和工艺单元的高度。

而在nanoribbon*(以下简称NR)的加持下,对于沟道的控制能力进一步增强,并且可变的NR堆叠层数和NR宽度,可以允许更大的载流子通量,从而进一步提高单元密度。在NR基础上,将nMOS和pMOS进行堆叠,可以进一步将摩尔定律推进到极限。

在IEEE IEDM 2020会议上,英特尔发布了基于NR的垂直堆叠CMOS结构的研究成果,这种结构与IMEC在VLSI国际会议上展示的CFET*的技术路线近似,都是在垂直方向上实现一个CMOS单元的构成,通过在y轴上同时堆叠pMOS和nMOS以缩小工艺单元的中心间距,实现晶体管面积的缩小。

*Nanoribbon:GAA环栅晶体管的一种形态,与nanosheet类似,同样为片状结构的沟道。

*CFET:Complementary Field Effect Transistor,是将nMOS和pMOS垂直堆叠的一种新型晶体管结构,通过将Contact Poly Pitch(PP)做到最小,极大地缩小了CMOS单元面积。

从平面CMOS晶体管结构到堆叠CMOS晶体管结构

该成果以“3-D Self-aligned Stacked NMOS-on-PMOS Nanoribbon Transistors for Continued Moore’s Law Scaling”为题发表,内容于2021年3月解禁,G. Dewey、E. Mannebach等28位英特尔研究人员共同完成了该成果,通讯作者为Cheng-Ying Huang。

研究内容

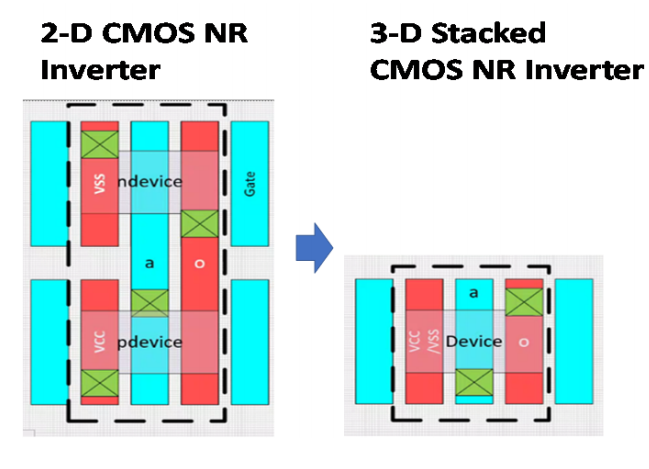

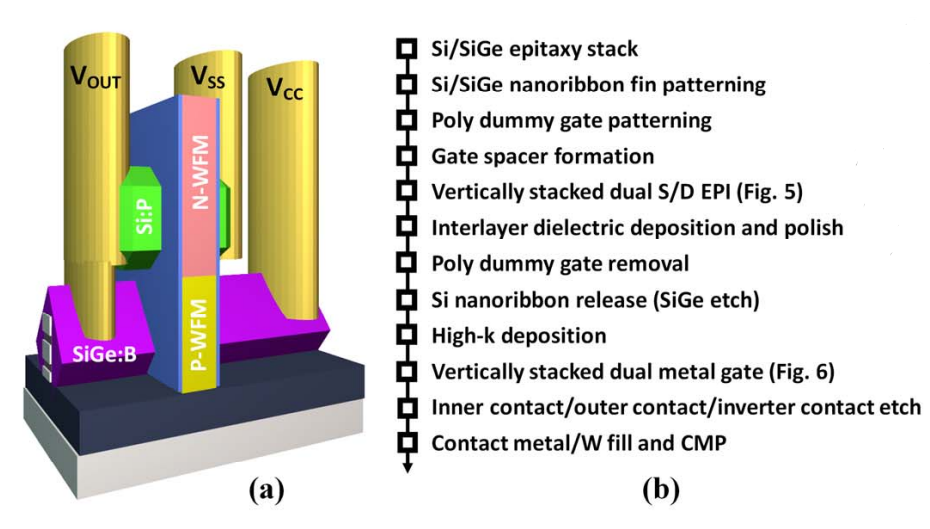

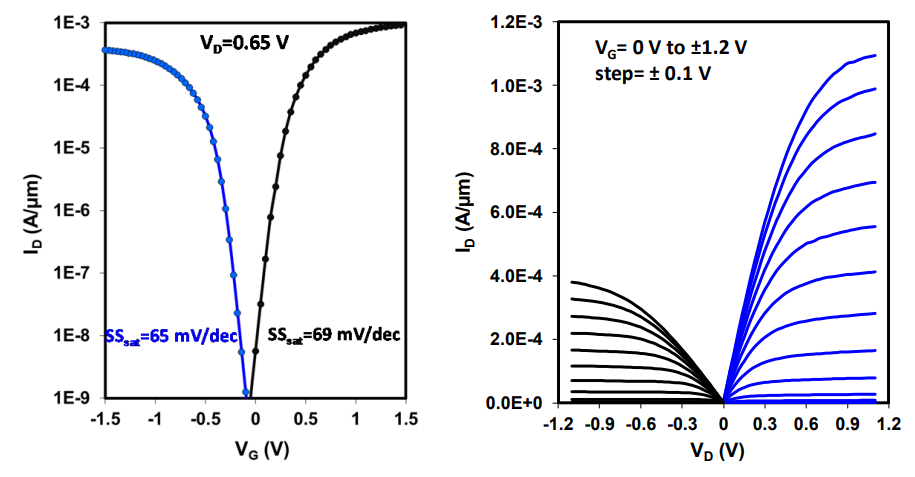

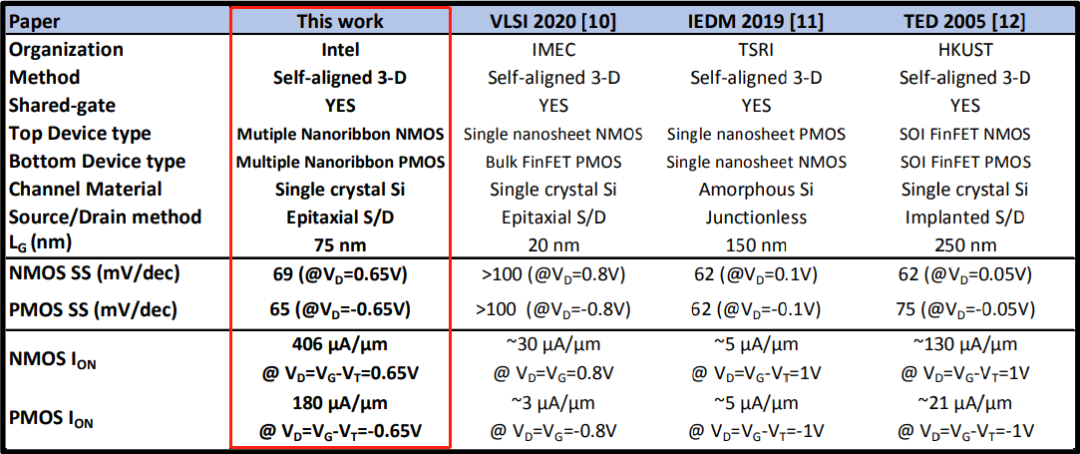

该成果展示了三维自对准*堆叠的nMOS-on-PMOS的NR结构晶体管,成功地在垂直方向上完成了CMOS工艺单元的集成,相比在平面上分别排布nMOS和pMOS的结构,可缩小50%的器件排布面积;该结构中上部的nMOS和底部pMOS均显示出高导通性能和优秀的短沟道控制能力,在电特性测试中CMOS反相器也显示出良好的电压传输特性。英特尔的研究人员认为,这一新的器件结构将会延续摩尔定律的发展。

*自对准:制作大规模集成电路的一种重要工艺,可有效减少MOSFET中的寄生电容,提升电路工作频率和速度。

n/p堆叠式的NR晶体管结构将节约50%的面积

8层NR沟道堆叠晶体管的TEM形貌像及外延的RSM点阵图

晶体管3D建模图以及制造工艺流程

5层沟道堆叠结构的TEM形貌像

ID-VG特征曲线和ID-VD特征曲线,LG=75nm

研究成果性能对比

前景展望

在过去的数年中英特尔受困于悬而未决的良率问题,技术节点停滞在14nm而更先进的10nm工艺则未能实现预期量产规模,使得一直以来的摩尔定律先锋逐渐落后于台积电。而在IEDM的新成果展示中,英特尔展示出了与IMEC的CFET技术路线类似的前沿研究成果,并喊出了“延续摩尔定律”的响亮口号。

根据英特尔公开的技术路线规划,在5nm节点将会使用nanosheet或nanoribbon形态的GAA结构,本项成果作为GAA的再升级版本则可能在3nm或2nm量产,从具体技术参数来看,本项成果的栅长与对应节点的参数要求还有很大距离,恐怕仅仅是初步的技术原型,还有很多进一步的工作尚未完成。这会是英特尔王者归来的助推剂,抑或是另一个久不落地的大卫星?让我们拭目以待。

责任编辑:lq

-

#高通 #英特尔 #Elite 高通X Elite芯片或终结苹果、英特尔的芯片王朝深圳市浮思特科技有限公司 2023-10-27

-

支持嵌入式计算的基于英特尔赛扬处理器U3405、P4500和P4505的平台2011-03-11 0

-

英特尔将在2014年推出14纳米处理器芯片2011-12-05 0

-

英特尔效仿联发科 再战手机叫板高通2012-08-07 0

-

英特尔转型移动领域难言乐观2012-11-07 0

-

产业风暴,英特尔能否扳倒ARM?2016-09-26 0

-

5G芯片市场,你看好英特尔还是高通?2017-03-01 0

-

【AD新闻】英特尔解读全球晶体管密度最高的制程工艺2017-09-22 0

-

英特尔凌动N450受到幽灵的影响2018-10-26 0

-

英特尔爱迪生闪存失败2018-11-02 0

-

OpenCL平台和英特尔Stratix 10 FPGA的结合使用2019-07-17 0

-

英特尔半导体制程的节点命名2019-07-17 0

-

为什么选择加入英特尔?2019-07-25 0

-

英特尔重新思考解决芯片短缺的常用基板2022-06-20 0

-

N沟道和P沟道MOSFET的区别是什么2023-02-02 0

全部0条评论

快来发表一下你的评论吧 !