如何制造出具有更高采样率的示波器?

电子说

描述

当 ADC 技术已经在最大采样率方面达到限制时,示波器厂商如何制造出具有更高采样率的示波器?追求更高采样率或许只是想满足示波器用户对于“越高越好”的认知,或者用户认为若要获得更高的带宽实时示波器测量效果,实际上可能需要更高的采样率。但是,若使示波器具有更高的采样率,并非像选择具有更高采样率的现成模数转换器那样简单。

所有主要示波器厂商均采用一种常见的技术,即交叉多个实时 ADC。但是,请不要将此交叉采样的技术与重复采集技术相混淆,我们将后者称之为“等效时间”采样。

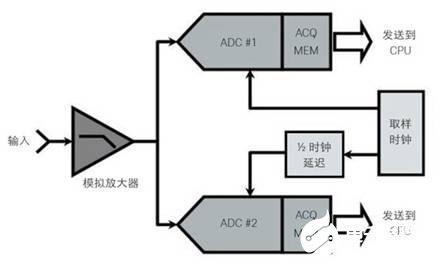

图 1 显示由两个 ADC 利用相位延迟采样技术构成的实时交叉 ADC 系统结构图。在本例中,ADC 2 一律对 ADC 1 采样之后的 ½ 时钟周期进行采样。在每个实时采集周期完成后,示波器的 CPU 或波形处理 ASIC 会对存储在每个 ADC 采集存储器中的数据进行检索,然后交叉样本以获得实时的数字化波形,且样本密度也会翻倍(是采样率的两倍)。

具有实时交叉采样特征的示波器必须遵守两个要求。一是,若要实现无失真的准确交叉,每个 ADC 的垂直增益、偏移和频率响应必须严格匹配。其二,必须对相位延迟时钟进行高精度的校准,以满足 Nyquist 规则二的要求,即等间隔采样。换句话说,ADC 2 的取样时钟必须在样品 ADC 1 之后精确地延迟 180 度。这两个条件对于准确交叉都非常重要。但是,为了对因交叉不良而导致的错误有更直观的理解,后文将重点分析仅因相位延迟定时不佳而导致的错误。

图 1:由两个交叉 ADC 构成的实时采样系统

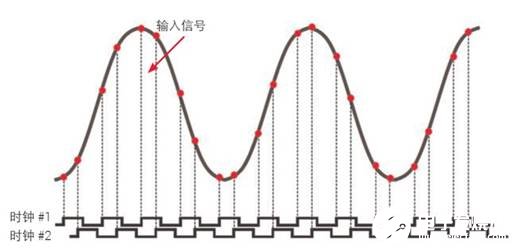

图 2 中所示的定时图说明,如果两个交错的 ADC 相位延迟时钟系统彼此之间没有呈现精确的 ½ 采样周期延迟,则交错采样会出现定时误差。此图显示了实时数字化的点(红点)相对于输入信号进行实际转换的位置。但是,由于对相位延迟定时校准不理想(紫色波形),这些数字化的点没有进行等间隔采样,因此也就违背了 Nyquist 的第二条规则。

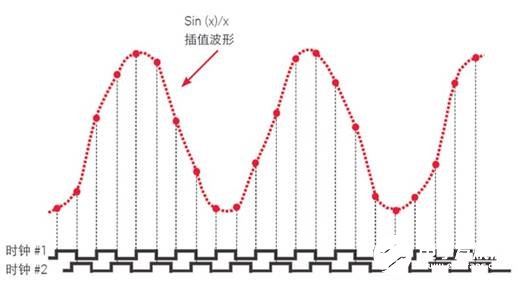

当示波器的波形处理引擎对每个 ADC 采集存储器所存储的数据进行检索时,首先会假设每个存储设备中的采样数据为等间隔采样。当您尝试着对初始输入信号的形状进行重建时,示波器 Sin(x)/x 重建滤波器所表示的信号将出现严重失真(如图 3 所示)。

由于输入信号与示波器取样时钟之间的相位关系是随机的,当您查看重复采集时,实时采集失真(有时称为“采样噪声”)可能会被误释为随机噪声。但该相位关系也不完全是随机的,也具有一定的确定性,且与示波器的取样时钟直接相关。

图 2:非等间隔采样的定时图

图 3:该定时图显示了因相位延迟定时不佳而造成失真的波形,使用 Sin(x)/x 滤波器对其进行重建

编辑:lyn

-

示波器的采样率和示波器存储深度2009-08-25 0

-

如何理解制造出这块电路板2016-02-25 0

-

示波器的采样率知识详解2018-12-04 0

-

【示波器维修】告诉您什么是示波器的采样率?2019-03-25 0

-

如何选择采样率,避免采样率不足对测试结果的影响2020-02-12 0

-

制造出高品质的线路板需要哪些条件2020-03-11 0

-

请问ARM是怎么制造出来的?2020-07-13 0

-

示波器采样率是什么2020-08-23 0

-

芯片是怎样制造出来的2021-10-25 0

-

示波器的采样率和存储深度2009-08-24 7157

-

示波器的带宽与采样率是什么关系2018-04-09 67078

-

示波器的采样率不足对测试结果有什么影响?2020-03-13 11206

-

什么是示波器的实时采样率?什么是示波器的等效时间采样?2023-10-17 1040

全部0条评论

快来发表一下你的评论吧 !