如何去正确理解采样时钟抖动(Jitter)对ADC信噪比SNR的影响

描述

前言:本文我们介绍下ADC采样时钟的抖动(Jitter)参数对ADC采样的影响,主要介绍以下内容:

时钟抖动的构成

时钟抖动对ADC SNR的影响

如何计算时钟抖动

如何优化时钟抖动

1.采样理论

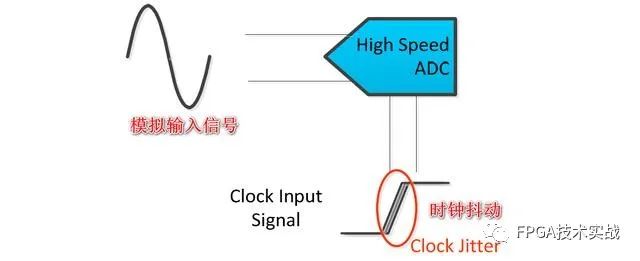

高速ADC使用外部输入时钟对模拟输入信号进行采样,如图1所示。图中显示了输入采样时钟抖动示意图。

图1、ADC采样

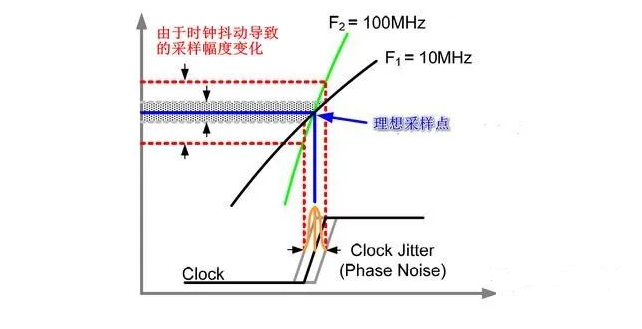

输入模拟信号的频率越高,由于时钟抖动导致的采样信号幅度变化越大,这点在图2中显示的非常明显。输入信号频率为F2=100MHz时,采样幅度变化如图红色虚线所示,明显大于输入信号F1=10MHz时采样幅度的变化。

图2、时钟抖动对不同频率输入模拟信号的影响

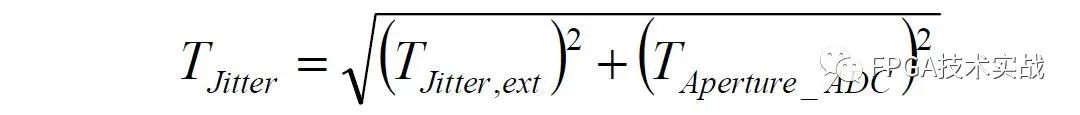

2.采样时钟抖动

采样时钟抖动主要由两部分组成:

外部输入时钟抖动

ADC孔径抖动

图3、时钟抖计算公式

时钟沿速率越快,带来的时钟抖动越小,同时也会增加PCB设计难度。

图4、时钟抖动构成

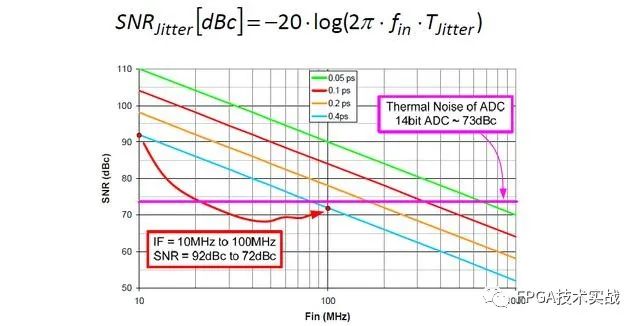

3.时钟抖动对SNR的影响

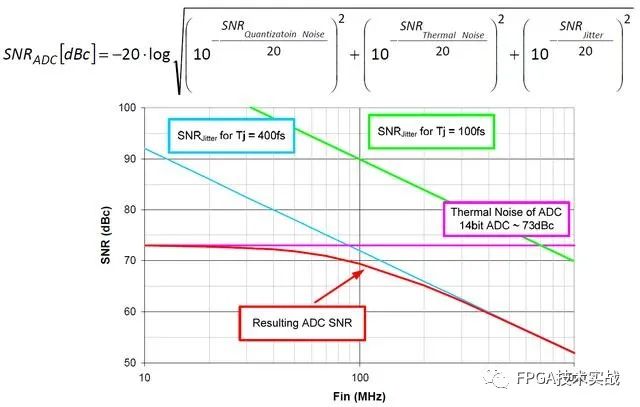

由于时钟抖动对ADC信噪比SNR的影响由图5所示公式计算。在图5中,可以看到时钟抖动对高频模拟输入信号影响更大。

图5、时钟抖动对SNR的影响

ADC噪声下限SNR一般由三部分构成:

ADC量化噪声

ADC热噪声

抖动衰减

图6、ADC噪声下限计算

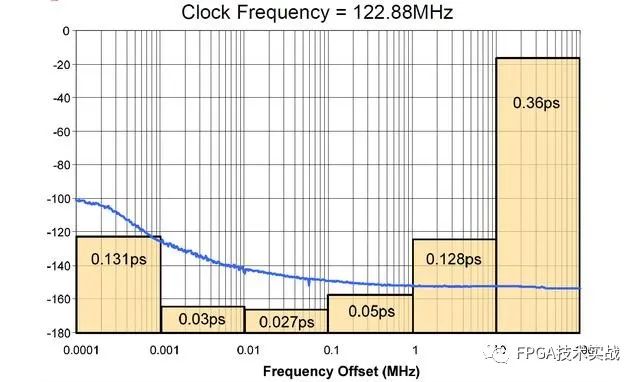

4.计算抖动的幅度

时钟抖动通过对时钟信号的相位噪声进行积分运算得到。典型的计算应用要求如图7所示。

图7、典型的时钟抖动计算要求

积分上限一般由以下因素限制:

时钟滤波器带宽

ADC时钟输入带宽

ADC采样速率

图8、时钟频率偏移对应的抖动值

5.SRN在频率的影响

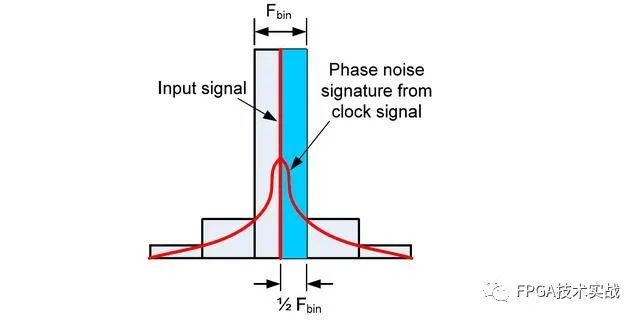

在采样过程中,时钟信号相位噪声被加到输入信号中。输入信号频率越高,相位噪声幅度越大,越大的相位噪声会导致越大的ADC噪声下限恶化,降低ADC有效分辨率。

图9、相位噪声在频率的频谱图

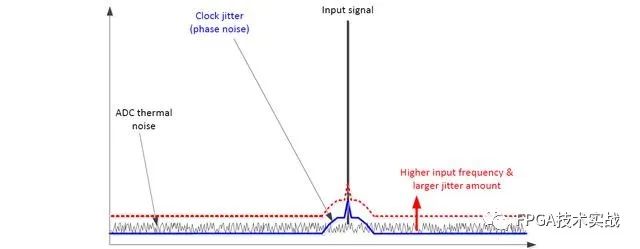

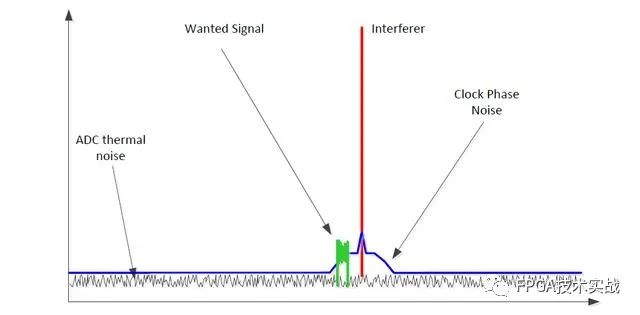

6.为什么时钟抖动/相位噪声如此关键

典型的接收机在“阻塞条件”下的性能包括两个方面:

一是,接收机需要在噪声背景下检测出想要的小信号

二是,在带内有大的干扰无法滤除,此干扰会影响小信号检测

图10、时钟抖动增强带内干扰影响

7.如何优化时钟抖动性能

为了使给定ADC的信噪比性能最大化,系统设计者可以采取几个步骤:

使用低抖动/相位噪声时钟源

使用低插入损耗的带通滤波器限制宽带噪声衰减

确保时钟振幅足够且不会降低ADC孔径抖动

编辑:jq

-

10.2 抖动对高速模数转换器(ADC)信噪比(SNR)的影响#ADC #SNREE_Voky 2022-08-16

-

PCB接地设计宝典4:采样时钟考量和混合信号接地的困惑根源2014-11-20 0

-

如何实现低抖动采样时钟电路的设计?2021-04-14 0

-

为高速A/D转换器设计时钟2009-09-30 333

-

高速ADC的低抖动时钟设计2009-11-27 543

-

高速ADC抖动产生SNR问题解析2010-12-25 2905

-

抖动和SNR详细介绍2011-01-05 1298

-

如何估算采样时钟抖动2012-04-01 1695

-

时钟抖动时域分析(中)2012-05-07 1444

-

正确理解时钟器件的抖动性能2013-06-21 14429

-

高速ADC时钟抖动的影响的了解2017-05-15 1184

-

时钟抖动时域分析2017-05-18 958

-

高速ADC在低抖动采样时钟电路设计中的应用2017-11-27 950

-

考虑数据采集应用中的采样时钟抖动2022-07-19 1591

-

估算SNR和SFDR的实际考虑因素2022-08-11 2856

全部0条评论

快来发表一下你的评论吧 !