浅谈一种用于MEMS姿态检测的FIFO设计

电子说

描述

摘 要: 通过在MEMS信号处理电路中设计一个异步结构的FIFO,可以有效地降低系统对MEMS的频繁访问。设计一个具有多种工作模式的FIFO,可以满足一些特殊的姿态检测需求,更好地满足系统智能化操作需要。实现了一个具体可行的方案,可以实际应用到各种MEMS电路模块中。

MEMS传感器是采用微电子和微机械加工技术制造出来的新型传感器。目前,加速度计已普遍用于智能终端(如智能手机)中,未来几年,陀螺仪也将普遍应用到智能终端中。同时,组合传感器,如3轴加速度计+3轴磁力计,3轴加速度计+3轴陀螺仪,甚至9轴组合传感器未来都会得到广泛应用,相应地也会带来数据处理量的增加。

目前的加速度计、陀螺仪和磁力计等MEMS电路的数据输出速率一般在几赫兹到几百赫兹之间。主系统处理单元一般通过串行通信接口I2C或者SPI访问MEMS电路来获取数据,除了需要实时响应的一些数据以外,主系统单元有时可能不希望频繁地用串行接口去检测MEMS电路状态,看内部数据是否已经准备好,然后读取有效数据,因为这样会降低整个系统的工作效率。对于类似于智能手机的智能终端而言,随着功能越来越强大,系统处理的任务也越来越多,如何平衡将是一个问题。

针对上述情况,本文设计了一个48 bit数据宽度、64级存储深度的异步FIFO(First In First Out),可以有效解决主系统单元频繁访问MEMS电路的问题。这个FIFO具有旁路模式、连续模式、先入先出模式和中断模式4种工作模式,在中断模式下,通过设置不同的条件,可以在不需要主系统单元干涉的情况下自动抓取一些特殊状态的数据。这样可以节省很多系统资源。

1 FIFO系统设计

传统异步FIFO[1-2]采用触发器同步异步输入信号来降低出现亚稳态的几率,然后地址通过格雷码编码方式来消除地址多位变化导致的空满状态误判,需要用到真正的双端口RAM。采用触发器同步虽然可以降低亚稳态的几率,但也带来了时序分析和综合后仿真的难点。格雷码带来了设计的复杂性,可以通过时序逻辑的设计方式,在布局布线时插入时钟树来避免空满状态的不定。同时真正的双端口RAM不是每个集成电路工艺线都支持的,采用伪双端口RAM更实际,也能使设计适用范围更广泛。

整个系统实现还要包括I2C和SPI接口模块、信号处理模块以及中断检测模块,本文仅仅描述FIFO模块。FIFO模块的实现框图如图1所示。写时钟是MEMS数据采样时钟,读时钟是串口I2C或者SPI读数据时钟。为了消除读写同时进行产生的冲突,增加了一个写使能信号,其与写时钟同时由内部逻辑产生,写时钟比读时钟优先级高。

这样可能会引入一个问题,那就是读写恰好同时进行的时候,读的数据依然是上一个数据,但可以设置为先入先出模式,数据满了之后不再更新,这样就不会有这个问题。模式设置和水印阈值设置通过串口I2C或者SPI写入。同步双端口RAM采用SMIC 0.18 m工艺Memory Compiler综合出来的64×48 bit的IP模块,这是一个伪双端口RAM,读写时钟是共用的。48 bit数据宽度可以同时存储3个轴的MEMS检测数据,每个轴16 bit数据宽度,基本可以满足目前的MEMS精度要求。

2 功能模块设计

2.1 读地址产生逻辑

读地址产生逻辑,根据工作模式和FIFO的状态,生成读地址指针。假如读时钟有效,并且FIFO不为空,则读地址加1,假如FIFO为空,则读地址保持不变。在连续工作模式下,由于数据不断滚动更新,当数据满的情况下,假如写入有效,读地址加1,保证读地址指针指向最先写入的数据地址。

2.2 写地址产生逻辑

假如写入有效,写地址指针自动加1。通过控制RAM时钟,在先入先出模式下,假如FIFO满,终止写入新的数据到RAM中,因此写地址指针不再更新,除非重新使能整个FIFO模块。

2.3 状态生成逻辑

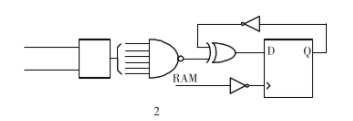

FIFO的状态可以直接用写地址指针减去读地址指针来获得,但也需要考虑到当FIFO满的时候,读地址指针和写地址指针是指向同一个地址的,这时候减出来数据就为0了。因此需要增加中间寄存器,在未满的时候输出减法器的数值,在满的时候输出全1数值。满和空状态信号、水印标记信号和FIFO停止信号都由时序逻辑生成,满信号逻辑电路图如图2所示,用RAM时钟的反相信号来触发。

水印标记可以通过设置水印的阈值来获得,阈值范围可以是0~63。当FIFO的状态值超过设置的阈值,就产生水印标记中断;当FIFO的状态小于设置的阈值,水印标记中断就清除,这可以让主系统根据应用场合灵活选择。FIFO停止信号有两种情况,在先入先出模式下,满了之后产生FIFO停止信号,RAM数据停止更新;在中断模式下,在中断信号产生之前,不产生FIFO停止信号,中断信号产生之后,根据满状态信号产生FIFO停止信号。

3 工作模式

3.1 旁路模式

在旁路模式下,复位信号有效,FIFO不工作,主系统单元直接读出ADC输出的数据。

3.2 连续模式

在连续模式下,数据在FIFO里面不断更新,相应地,读地址指针和写地址指针也不断滚动更新,读地址指针指向最先输入的RAM地址。在连续模式下,假如数据满了之后,写时钟有效,读地址指针和写地址指针需要同时加1,因为最先的数据已经被覆盖了。同时在写时钟无效的时候,读时钟有效,读地址指针也要加1。

3.3 先入先出模式

在先入先出模式下,数据填充满了就自动终止,产生满中断信号。在没有读时钟的情况下,最终读地址指针和写地址指针将会同时指向地址0。相应地,在未充满的情况下,假如读时钟有效,最终读地址指针和写地址指针会同时指向中间某一个地址。

3.4 中断模式

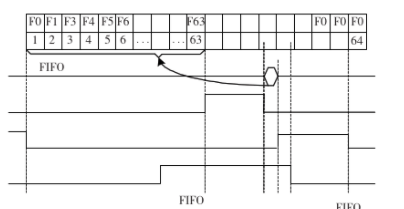

在中断模式下,数据先是以连续模式工作,假如中断信号有效,进入先入先出模式,数据填充满了就自动终止。工作时序图如图3所示,数据在未填充满的情况下,产生中断信号,数据填充满了就产生终止信号,满中断信号置1,数据开始读出之后,满中断信号清0,当数据完全读完后,空中断信号置1。假如FIFO需要重复上面的工作流程,需要清中断,重新启动FIFO,在数据开始重新写入FIFO时,空中断信号清0。

与传统的异步FIFO不同,本文实现了一个更加简单、并且实际可行的FIFO结构,操作灵活可靠。通过在MEMS信号处理电路中加入异步FIFO设计,可以更好地满足系统对低功耗和操作灵活性的需求。通过DC综合并流片验证,该FIFO电路已经应用到多个MEMS电路产品中,得到很好的效果。特别对于未来MEMS组合传感器、数据量的增加以及特殊姿态的处理,引入更多灵活性的FIFO将会带来更多的优越性。

参考文献

[1] 于海,樊晓桠.基于FPGA异步FIFO的研究与实现[J].微电子学与计算机,2007(3):210-213.

[2] 刘祥远,陈书明.一种高性能的异步FIFO结构[J].电子学报,2007(11):2098-2104.

编辑:jq

-

MEMS组装技术浅谈2014-08-19 0

-

基于MEMS姿态传感器的温度补偿方法2018-11-06 0

-

基于MEMS和MR传感器的嵌入式系统姿态测量2018-12-04 0

-

一种应用于X波段的RF MEMS电容式并联开关设计2019-06-25 0

-

嵌入式姿态测量系统的姿态参数怎么计算?2019-08-22 0

-

介绍一种基于FIFO结构的优化端点设计方案2021-05-31 0

-

请问怎样去设计一种异步FIFO?2021-06-18 0

-

请问怎样去设计一种基于MEMS的声级计?2021-07-02 0

-

如何去实现一种基于单片机的云台姿态测量系统设计2021-11-25 0

-

基于MEMS的姿态测量系统2009-06-08 826

-

基于MEMS姿态传感器温度补偿方法2014-05-07 4769

-

基于磁强计和MEMS陀螺的弹箭全姿态探测2016-12-17 646

-

基于MEMS的捷联姿态系统的设计与试验_胡佳兴2017-01-12 487

-

MEMS信号处理电路中的FIFO系统设计2018-05-05 1554

-

MEMS陀螺仪姿态算法研究综述2021-05-26 1384

全部0条评论

快来发表一下你的评论吧 !