详解基于SOPC多波形信号发生器设计

电子说

描述

1引言

随着现代电子技术和大规模集成电路的发展,DDS技术是一种新颖的频率合成技术,并得到了飞速的发展,已成为最重要的频率合成技术,其具有易于控制、相位连续、输出频率稳定度高、频率转换速度快和分辨率高等优点。SOPC(system on a programmable chip)片上可编程系统是一种灵活、高效的SOC解决方案,它具有双重含义,首先是片上系统,有单个芯片完成整个系统的主要的逻辑功能,其次他是可编程的系统,具有灵活的设计方式,可裁减、可扩充、可升级,并具有软硬件在系统可编程的功能。通过NiosII嵌入式系统实现SOPC,设计一种基于FPGA的多波形发生器,可以输出正弦、余弦、方波、三角波和锯齿波等常见波形,同时可以完成AM调制、FM调制、FSK调制等多种调制信号,具有很强的实用价值。

2系统设计

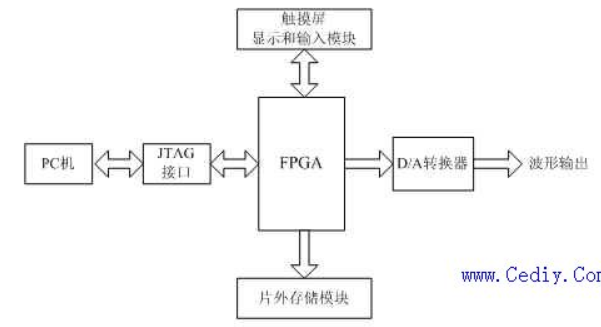

系统包括FPGA、触摸屏显示和输入模块、片外存储模块、D/A转换器和JTAG接口,FPGA中配置NiosII软核CPU、信号发生模块和相关的接口控制逻辑电路,所述触摸屏显示和输入模块、片外存储模块、D/A转换器和JTAG接口均与FPGA相连,FPGA通过JTAG接口和PC机连接,FPGA通过D/A转换器后波形输出。触摸屏显示和输入模块为TFT液晶触摸屏,提供人机交互界面,负责界面显示和外部输入。片外存储模块为SDRAM存储器。D/A转换与滤波电路主要由D/A转换、滤波、幅值调节和电源模块组成。PC端软件有Matlab编程实现,完成用户界面(GUI)、编辑产生波形数据、频率控制和与片上系统通讯等功能,系统框图如图1所示。

3 SOPC硬件设计

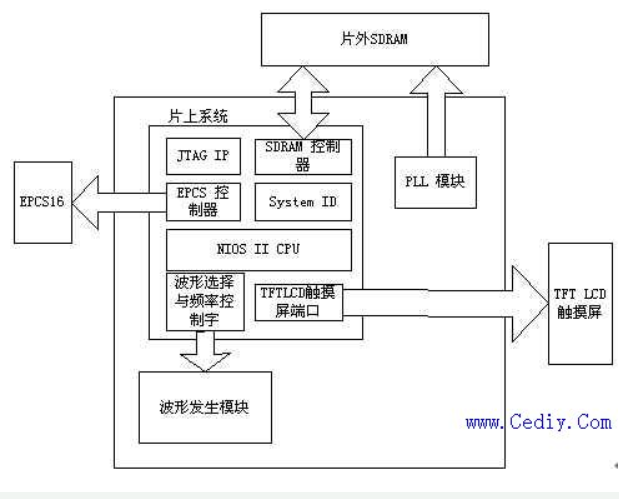

SOPC系统主要包括NIOSIICPU、SDRAM控制器、和I/O接口,通过调用Altera公司提供对应的IP进行定制设计,整个NiosII系统如图2所示。

图2.片上系统总体框图

该模块通过SOPC Builder中调用IP库组建实现,主要由NiosII CPU、SDRAM控制器、通用IO、EPCS控制器、system ID、JTAG UART,与外部链接的端口主要五个部分,分别是系统时钟与复位、TFT LCD控制信号线、触摸屏控制信号线、SDRAM接口控制线、序列信号发生器控制信号线等,构成了整个系统的软件底层硬件平台部分,系统时钟100MHZ。

设计中考虑到片上RAM存储的数据量较大而NIOSII CPU只负责UART串口的数据传输可简单的接口控制,故NIOSII CPU选择NiosII/f经济型内核。SDRAM控制器用来连接板上集成的64MByte SDRAM。SDRAM控制器的数据端dq[15.。.0]连接输入输出端口bidir。在Presets中选择第一项Custom,在Bits中选择16,完成SDRAM控制器的设置。IO口主要用于TFT LCD触摸屏的控制以及相关信号线,还包括信号的输出、SDRAM的控制信号线等。System ID是一种标示符,类似校验,在下载程序之前或者重启之后,都会对其进行检验,以防止Quartus和NIOS程序版本不一致的错误发生。JTAG UART是实现PC和NiosII系统间的串行通信接口,它用于字符的输入输出,在NiosII的开始调试过程中扮演了重要的角色。PLL模块通过调用QuartusII内嵌的器件函数实现,QuartusII内嵌了许多常用器件的函数,用户只需要进行设置即可直接调用,而不需要自己编程,这大大提高了系统开发的效率。SDRAM芯片必须和Avalon接口一样以相同的时钟驱动,片内的锁相环(PLL)通常用于调整SDRAM控制器内核与SDRAM芯片之间的时钟相位差。由于PLL不是包括在SDRAM控制器内,所以必须手动添加生成PLL模块。设计中,片外SDRAM的时钟输入必须比系统的时钟滞后-75度相位(注意不同型号的SDRAM器偏移角度不同)。

4波形发生模块的设计

4.1 DDS原理

DDS技术是一种把一系列数字量形式的信号通过DAC转换成模拟量形式的合成术,目前使用最广泛的一种DDS方式是利用高速存储器作为查寻表,然后通过高DAC产生已经用数字形式存入的波形。DDS的主要思想是从相位的概念出发合成所需要的波形,其结构由相位累加器、波形存储器、数模转换器、低通滤波器和参考时钟五部分组成。相位累加器由N位加法器与N位累加寄存器级联构成,每来一个时钟脉冲fs,加法器将频率控制字k与累加寄存器输出的累加相位数据相加,把相加后的结果送至累加寄存器的数据输入端。累加寄存器将加法器在上一个时钟脉冲作用后所产生的新相位数据反馈到加法器的输入端,以使加法器在下一个时钟脉冲的作用下继续与频率控制字k相加。这样,相位累加器在时钟作用下,不断对频率控制字进行线性相位累加。由此可以看出,相位累加器在每一个时钟脉冲输入时,把频率控制字累加一次,相位累加器输出的数据就是合成信号的相位,相位累加器的溢出频率就是DDS输出的信号频率。用相位累加器输出的数据作为波形存储器(ROM)的相位取样地址,把存储在波形存储器内的波形抽样值(二进制编码)经查找表查出,完成相位到幅值转换。波形存储器的输出送到D/A转换器,D/A转换器将数字量形式的波形幅值转换成所要求合成频率的模拟量形式信号。低通滤波器用于滤除不需要的取样分量,以便输出频谱纯净的正弦波信号。

4.2频率和幅度调节

用上述方法产生的波形,其波形频率由两方面决定:

(1)波形的频率由地址计数器的计数时钟决定,当波形存储器的点数一定时,计数器的计数时钟频率越快,读出一周期波形数据的时间就越短,输出波形的频率就越高,反之则波形频率低。

(2)波形的频率也由组成一周期波形的点数来确定,当地址计数器的时钟频率一定时,一周期波形的发生器点数越多,读完一周期波形所需的时间越长,波形频率就越低,反之则越高。

由于相位累加器字长的限制,相位累加器累加到一定值后,其输出将会溢出,这样波形存储器的地址就会循环一次,即意味着输出波形循环一周。故改变频率控制字即相位累加器步进,就可以改变相位累加器的溢出时间,在时钟频率不变的条件下就可以改变输出频率。

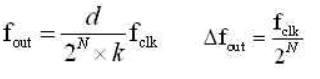

由此,可推出该系统的输出频率fout与系统时钟频率fclk之间的关系为:

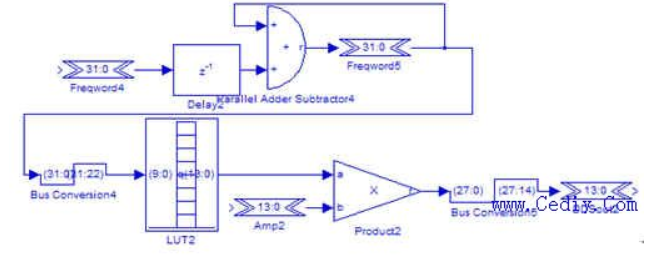

4.3 Matlab/DSP Builder中的常规波形设计

根据DDS工作原理,在Matlab下建立DDS基本原理图的模型如图3所示,设计中频率控制字Freqword为32位,ROM表中LUT2中共存储了位宽为14位的2048个波形数据,其中在波形ROM查找表的MatlabArray中根据输出的波形填写不同的数据公式,详细公式如下:

正弦波:8191*sin([0:2*pi/(2^11):2*pi])

方 波:8191*square([0:2*pi/(2^10):2*pi])+8192

三角波:8191*sawtooth([0:2*pi/(2^10):2*pi],0.5)+8192

锯齿波:8191*sawtooth([0:2*pi/(2^10):2*pi])+8192

Delay为延时单元,综合后为寄存器,Haraller Adder Subtractor是并行加法器,Bus Conversion是总线宽度转换,Product为加法器,Amp为波形幅度控制数据14位宽。

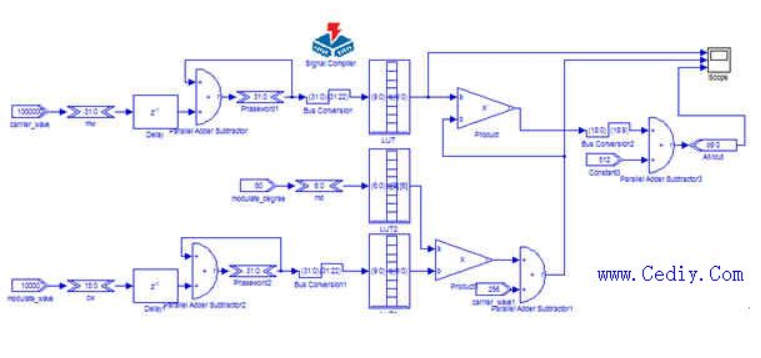

4.4 Matlab/DSPBuilder中的调制信号的设计

4.4.1 AM调制信号

AM幅度调制函数可简单表示为F=Fdr*(1+Fa*m),其中Fdr,Fa,F分别是载波信号,调制波信号及调制后AM输出的信号,他们都是有符号函数;m是调制度(0《m《1)。根据AM调制信号的工作原理,利用Matlab建立AM基本原理图的模型如图4所示,首先根据公式构建一个载波信号Vo(t)=VoCOSωot频率carrier_wave为1000000的载波信号,波形函数为511*sin([0:2*pi/(2^10):2*pi]),其次再构建一个谐调制信号:VΩ(t)=VωcosΩt频率modulate_wave为10000,波形函数为255*sin([0:2*pi/(2^10):2*pi]),与调制度modulate_degree为0.5相乘后再与载波信号经过Product相乘便可得到AM调制信号,由于ADC输出的正信号因此再将信号由-512~+512转换成0~1024,以便于后期输出转换。

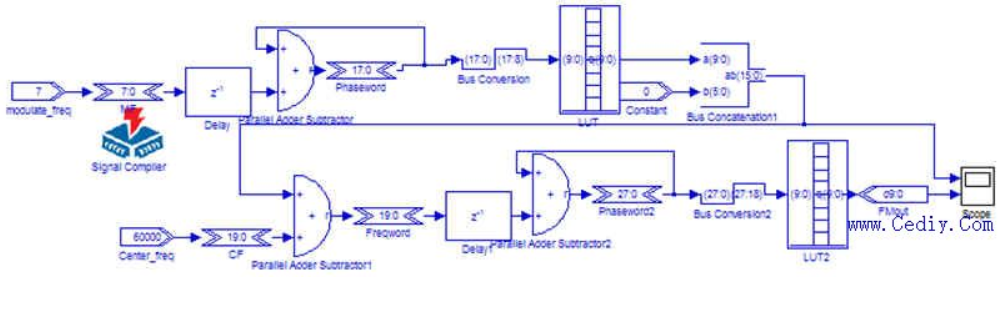

4.4.2 FM调制信号

根据FM调制信号的工作原理,利用Matlab建立FM基本原理图的模型如图5所示,先构建调制信号函数为511*sin([0:2*pi/(2^10):2*pi])将输出数据向左移动6位,低6位补0构成16位数据再与中心频率控制字相乘控制中心频率的输出,中心频率ROM函数511*sin([0:2*pi/(2^10):2*pi])+512。

图5.FM调制模型

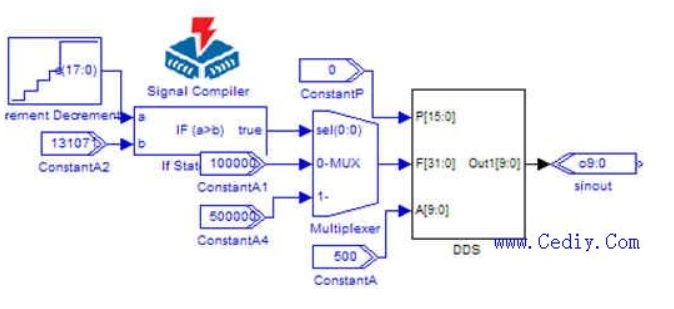

4.4.3 FSK调制信号

根据FSK调制信号的工作原理,利用Matlab建立FSK基本原理图的模型如图6所示,incerment Decerment是一个递增的时钟计数模块位宽是18位与131071相比较生产二进制序列,控制选择模块Multiplexer来选择送给DDS模块的频率控制字,在此分别设置了两个频率Constant1和Constant2,DDS模块负责频率的输出结构与前面常规波形设计形似,在此不再赘述。

5 PC端软件设计

系统另一大特点就是能与PC联机使用,通过个人计算机对FPGA进行调度指挥控制,并能监控设备的运行状态,使波形输出。在GUI界面中,设置了公式波的公式输入文本编辑框,只需要在文本编辑框中输入公式,根据它已有的条件就可以产生信号波形,由于输入的公式是用户自定义的,用户可以使用多种算法或者运用MATLAB自带的函数库。文本编辑框里输入文本后,MATLAB会把输入的文本默认成字符串。当想对这些输入在文本编辑框里的公式进行计算时,MATLAB无法识别,故使用Eval函数对字符串进行处理。Eval符号表达式转化为数值表达式,这样就能使MATLAB执行公式,公式法产生的波形更精确。

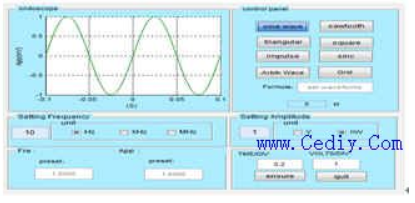

用户界面软件如图7所示,波形选择按钮中,用户可以选择正弦波、方波、锯齿波、三角波、sinc波、线性调频信号等,选择波形的同时将波形数据发送给信号发送给信号发生器。用户也可以自定义编辑波形,有公式法编辑和绘图法编辑,使用绘图法编辑波形,只需点击“任意波形”按钮,然后按照提示在坐标轴内点击鼠标右键取点画出所要波形的大概形状,再点击鼠标左键就可以产生用户想要的波形;当使用公式法编辑波形,只需按提示在编辑框中写入所要产生的波形公式,点击“任意波”按钮,系统就会立刻对输入公式进行计算,并向硬件传送改变波形类型的字符,然后再把数据发送到硬件上。界面幅频预值设定中频率单位在Setting Frequency中选择,幅度单位在Setting Amplitude中选择。用户可以在Fre和App一栏中预设幅频大小,通过改变文本框中的数值,可以改变输出波形的值以及界面图形的显示比例。

6 系统仿真和测试

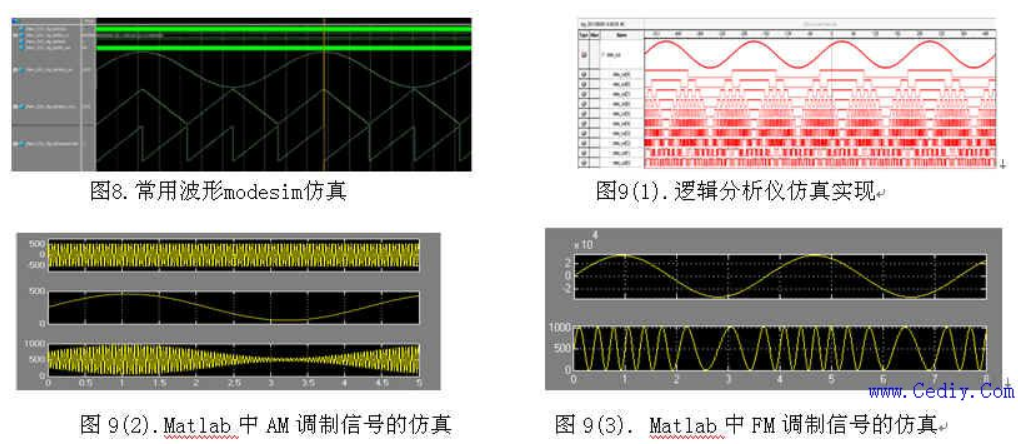

系统使用第三方仿真工具Modelsim对DDS模块进行功能仿真,也就是前仿真,仿真结果如图8所示。由于Modelsim只在功能上进行仿真,对器件的延时没有考虑在内,因此将系统下载配置到FPGA当中,使用QuartusII自带的signalTapII逻辑分析仪对波形输出端口数据进行采集,能够真实的反映本设计在硬件上的实现情况,如图9所示。

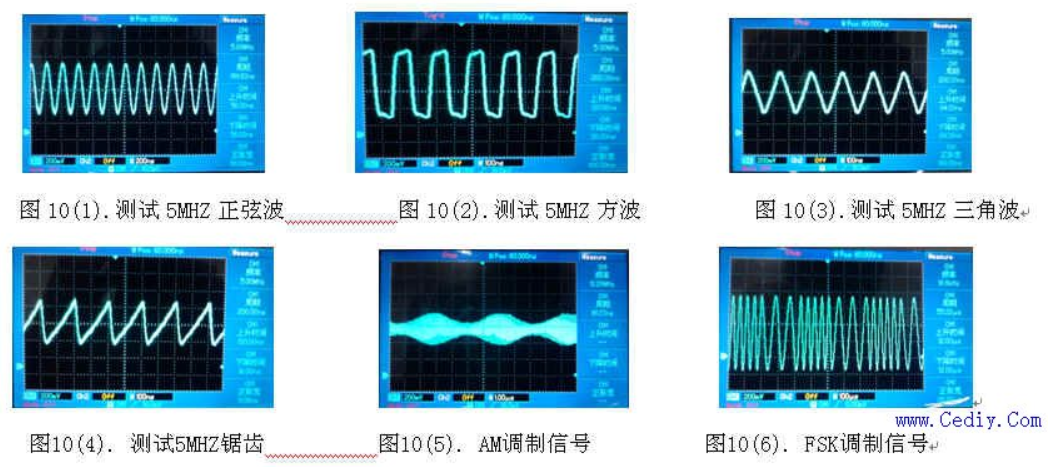

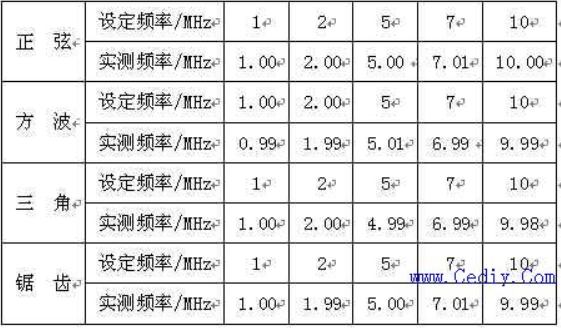

将输出信号连接至示波器对系统的各项指标进行测试,测试条件:(示波器UTD2062CEL,60MHZ,1GS/s,输出5MHZ正弦波、三角波、方波、锯齿波),显示的频率为5.00MHZ。主要分以下几个步骤:在波形选择界面分别选择正弦波、三角波、方波、锯齿波的波形和频率;选择AM调制信号输出,在示波器观察AM信号的调制;选择FM调制信号输出,在示波器观察FM信号的调制;选择FSK调制信号输出,在示波器观察FM信号的调制;连接至PC端测试在PC端控制波形输出和频率控制,示波器输出如图10所示,测量数据结果如表1示:

表1.波形频率数据测试表格

可以计算出,数据率平均误差约为0.1576%。在测试为随机信号的时钟时发现其时钟信号有信号的反射现象,进过分析发现如果IC之间的互连线比较长,线的特性阻抗又不均匀,或者终端没有匹配,会引起反射,如果始端也不匹配,则会来回反射而造成振铃。该现象的决定因素:特性阻抗、匹配方式、失配大小终端反射系数、始端反射系数、线长,分析原因是因为电路板是手工焊接的,信号完整性不是太好,同时也由于传输阻抗不匹配,因此通过在时钟信号线的终端和源端分别串接一个33Ω的电阻发现这种振铃现象得到了很大的抑制。

7 结束语

系统采用DDS技术,通过基于NIOSII的SOPC系统实现了任意发生器在相对带宽、频率转换时间、相伴连续性、正交输出、高分辨率及集成化的性能方面较好,同时基于NiosII的SOPC系统可以根据用户需要自由定制CPU及其个性,具有较强的灵活性和通用性。

参考文献

[1]魏丽娟,肖铁军,郎沁争等。基于SOPC的任意波形发生器人机交互系统设计[J]。计算机测量与控制,2012,10:2860-2862

[2]杨守良。利用Matlab/DSP Builder实现DDS的设计[J]。微计算机信息,2006,20:211-212

[3]吴丽华,刘洪涛,李胜明等。基于FPGA的程控多波形发生器的研制[J]。电测与仪表,2007,12:52-54

[4]刘畅,李智。基于FPGA的任意波形发生器的设计[J]。微计算机信息.2010(02):130-131

[5]周俊峰,陈涛。基于FPGA的直接数字频率合成器的设计和实现[J]。电子技术应用.2002(12):74-76

[6]孙超,林占江。基于DDS的雷达任意波形信号源的研究[J]。电子测量与仪器学报.2008(02):31-35

[7]陈科,叶建芳,马三涵。基于DDS+PLL技术频率合成器的设计与实现[J]。国外电子测量技术.2010(04):43-47

[8]陈风波,冒燕,李海鸿。基于FPGA的直接数字频率合成器的设计[J]。微计算机信息.2006(05):189-190

[9]张芳芳,周火凤,宋丽辉等。基于DSP和USB的数据采集系统的设计[J]。仪表技术与传感器.2010(07):66-68

[10]邓岳平,肖铁军。基于FPGA的并行DDS信号发生器的设计与实现[J]。计算机工程与设计.2011(07):2319-2323

编辑:lyn

-

制作多波形发生器信号发生器,简单的 #硬声创作季jf_49750429 2022-10-29

-

用555制作的多波形信号发生器2008-10-17 0

-

在SoPC上实现的波形发生器2009-06-25 0

-

请问怎么设计一个多波形信号发生器?2021-04-20 0

-

如何在SoPC上实现的波形发生器?2021-04-27 0

-

请问一下怎么在SoPC上实现波形发生器的设计?2021-05-06 0

-

怎么实现基于DSP和SOPC数字信号发生器的设计?2021-05-12 0

-

怎么实现基于SOPC的任意波形发生器设计?2021-05-18 0

-

在SoPC上实现的波形发生器设计2009-06-25 412

-

多波形信号发生器2008-10-17 4085

-

基于DSP和SOPC数字信号发生器的设计2009-10-22 638

-

多波形信号发生器设计原理分析2022-06-20 5686

-

是德信号发生器导入波形教程2023-02-24 958

-

关于波形发生器,你知道多少?2023-08-05 1979

-

信号发生器的特点 信号发生器可以产生哪些波形?2023-12-21 739

全部0条评论

快来发表一下你的评论吧 !