关于SPI基本知识和工作原理及硬件电路设计浅析

电子说

描述

设计之前先了解基本知识和工作原理

概述:SPI(Serial Perripheral Interface),中文是串行外围设备接口,由Motorola 公司开发并推出的一种串行通讯接口,一般主要应用在MCU和外围设备之间的通讯,广泛应用在Flash,模数转换器,通讯模块等外围芯片或者模块与MCU之间的通讯。

特点:高速(1.受限于最大时钟频率2.受限于CPU处理SPI数据的能力;3受限于PCB走线);

全双工(两个数据线可以同时收发);

主从模式(既可当主机又可当从机工作);

提供频率可编程时钟;

接口:SCK: Serial Clock,作用是主设备往从设备传输时钟信号,控制数据交换及速率;

SS/CS:Slave Select/Chip Select,用于主设备片选从设备,由主设备控制;

SDO/MOSI:Serial Data Output/Master Out Slave In,作用是SPI设备发送数据;

SDI/MISO: Serial Data Input/Master In Slave Out,作用是SPI设备接收数据;

工作模式:有四种工作模式,工作模式是根据CPOL和CPHA逻辑配置而定的。

SPI主模块和与之通信的外设备时钟相位和极性应该一致。

时钟极性CPOL(Clock POLarity):配置为0时SPI总线空闲为低电平,配置为1时SPI

总线空闲为高电平;

时钟相位CPHA(Clock PHAse):配置为0时在SCK第一个跳变沿采样(上升或下降),

配置为1时在SCK第二个跳变沿采样(上升或下降);

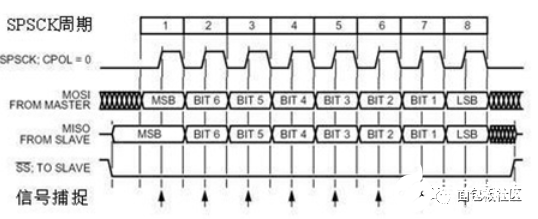

工作模式0:当CPHA=0、CPOL=0时

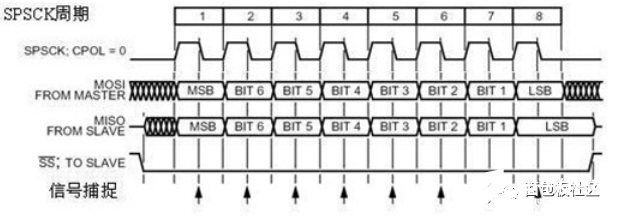

工作模式1:当CPHA=1、CPOL=0时

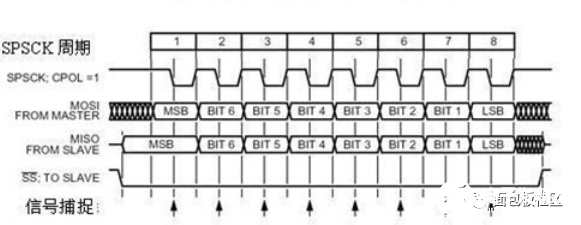

工作模式2:当CPHA=0、CPOL=1时

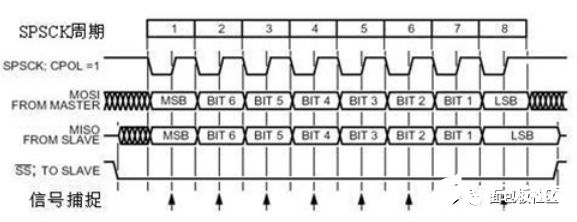

工作模式3:当CPHA=1、CPOL=1时

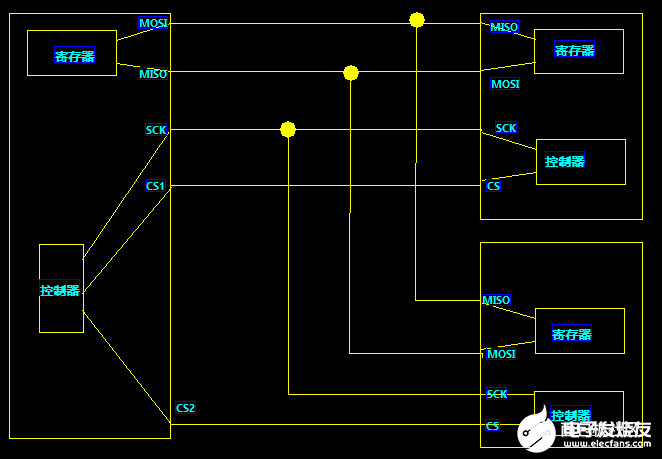

硬件电路设计

系统物理连接:SCK—SCK SDO/MOSI—SDI/MISO SS/CS—SS/CS

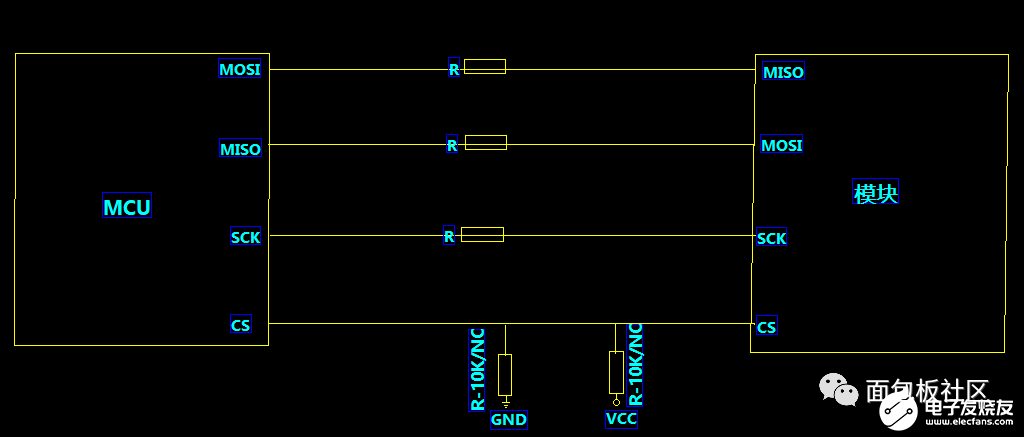

实际电路设计:

1.信号线和时钟线串电阻:终端阻抗匹配:高速信号一般在电路的终端串接小电阻用于阻抗的匹配,TTL

信号阻抗约13,串接33Ω即可,防信号完整性问题;

过ESD测试:用于过ESD测试;

接口防护:当信号线连接外部接口时,在接插件拔插瞬间可能会有高压,串接电阻可保护IO;

2. 片选信号:是否要接上拉电阻或者下拉电阻,看具体规格书要求;

3. 线能粗则粗,能短则短。减小线路寄生电容,电感(走线长度小于波长的20分之一,最长不要超过75cm;

4. 可以走弧形线就走弧形线;

5. 严格用地包络屏蔽;

6. 如果要求严格的话,可以把时钟线和数据线分开;

信号测试:

1.高低电平值;

2.最大和最新的过冲;

3.正回冲和负回冲;

编辑:lyn

-

关于电源的基本知识2012-05-29 0

-

关于ARM的基本知识2012-05-30 0

-

MOS管驱动电路设计秘籍(工作原理+电路设计+问题总结)2020-07-21 0

-

舵机的基本知识2021-09-13 0

-

硬件电路设计流程--原理图设计2016-10-10 1395

-

电路设计--储能元件工作原理2017-02-28 1162

-

开关电源的工作原理与电路设计2017-12-11 1220

-

硬件设计——关于电路设计的一些知识2021-11-06 528

-

采样保持电路设计及其工作原理2022-10-20 5371

-

仪表放大器工作原理、公式推导、电路设计2022-11-02 4321

-

DCDC电路设计的一些基本知识2023-03-07 3466

全部0条评论

快来发表一下你的评论吧 !