如何采用模块化思路构建一个3-8译码器

电子说

描述

我们用一个3-8译码器来结束本次对组合逻辑电路的介绍,并且最后我们还给大家准备了一个略微酸爽的任务,确保大家的脑神经都可以得到充分的摩擦。闲话不多,现在开始。

本次实验的任务是构建一个3-8译码器,且将译码结果通过小脚丫的LED灯显示。

听上去并不难,而且我能想象到,一定会有不少同学会立刻开始画一个8行的真值表,然后通过卡诺图进行化简,且根据最终的逻辑表达式画出门电路图。这个方法当然没有错,不过,如果面对更多位数的系统,比如4-16或者是8-256的译码器,建一个几百行的真值表并进行逻辑运算听上去似乎不那么科学。

在这里我们将采用模块化的思路来完成我们的实验设计。

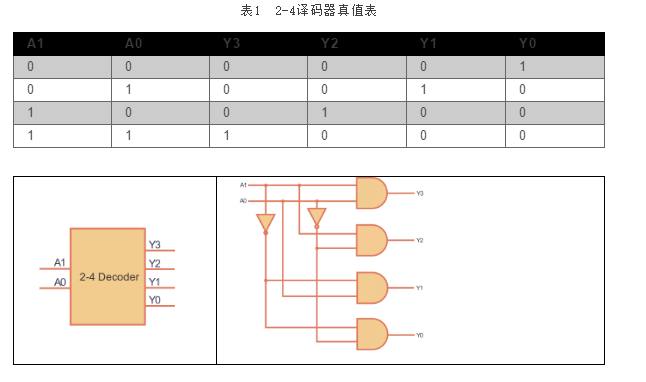

在开始进行模块化设计之前,我们先做一个2-4译码器,也就是译码器系列中最底层的基础模块。

这次的代码我们采用行为级描述(Behavioral-level)的写法,直接根据真值表将输入与输出的各种组合进行直接关联。可以看出,行为级的写法甚至不需要构建门电路,仅通过输入输出对应关系即可构建,因此最为抽象。

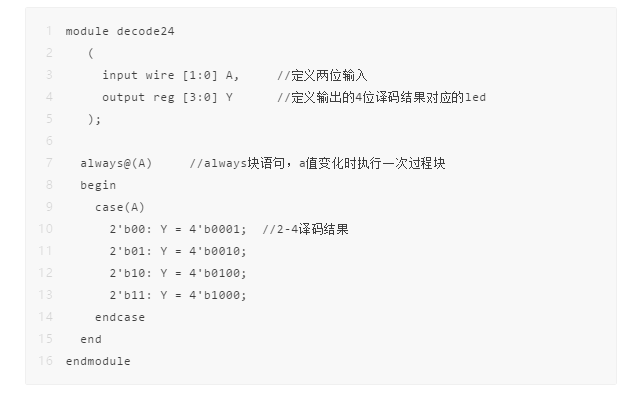

有了最基础的模块,如何通过它搭建出3-8译码器呢?现在,我们在原有的真值表上加上一路使能信号E,再来观察一下新的真值表。可以发现,当E为低电平时,不论输入的取值如何,前四位输出均为0。当E为高电平时,右侧仍然为2-4译码器的输出结构。

我们可以把表3看作为一个3-8译码器的真值表,只不过输入端的最高位由E代替。由于E为低电平时输出最高的四位均为0,因此确保我们在对后四位输出(黄色)进行赋值不会影响到前四位的输出。

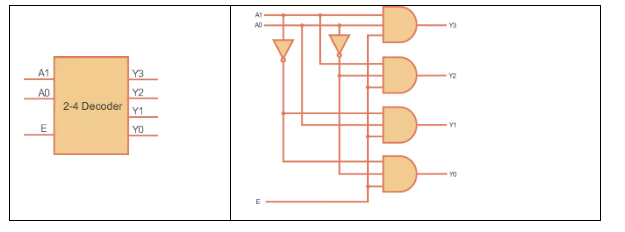

从表3不难看出,黄框和红框对应的其实就是一个带有使能端的2-4译码器,且使能端E控制着前后半端位数的输出结果。也就是说,一个3-8译码器可以由两个2-4译码器构成。同理,一个4-16译码器可以由两个3-8译码器构成,以此类推。

带有使能E的2-4译码器如下图所示。实际上就是在之前的代码上稍做修改,在这里我们就不详细写出来了,给大家自行练习的机会。

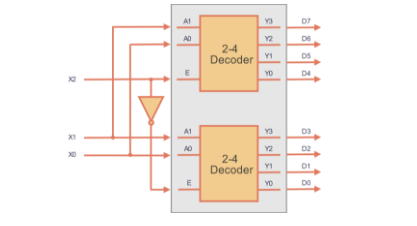

接下来,按照之前的分析,我们画出由两个2-4译码器组成的3-8译码器的结构。

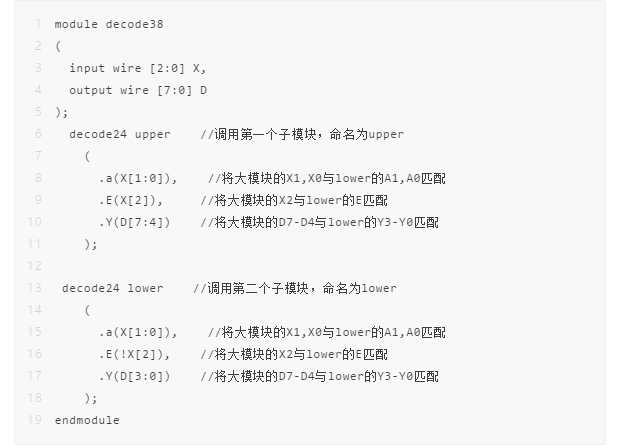

以下是用Verilog写的一个3-8译码器,在程序里我们调用了两次2-4译码器的子模块。注意,子模块的文件需要和decode38文件放在同一个工程目录下,不然就成了隔壁老王了。

当你反复在图和代码之间徘徊几轮,并有了多么痛的领悟之后,你就可以把自己编译好的程序下载到小脚丫里,然后通过实验测试你的代码了。

练习一下,当我们把输出D7-D1分别对应为小脚丫上的L7-L1,且输入X2-X0分别对应至小脚丫的SW3-SW1,请判断以下的LED状态(低电平亮)。

在倒腾了半天之后,你终于搞定了代码,并且成功在小脚丫上验证了你的设计,于是满怀信心的你终于可以尝试一下通过模块化的设计思路去构建4-16甚至更多位的译码器了。

责任编辑人:CC

-

组合逻辑3-8译码器的设计及实验2009-10-09 0

-

设计一个虚拟3-8译码器,实现138译码器的功能2012-05-15 0

-

关于 3-8译码器的 vhdl描述问题2012-10-17 0

-

什么是3-8译码器2013-03-26 0

-

3-8译码器2014-06-12 0

-

用QT的强制转换函数写3-8译码器2014-10-10 0

-

3-8译码器进行仿真设置问题2015-09-22 0

-

Xilinx FPGA入门连载20:3-8译码器实验2015-11-02 0

-

怎么用3-8译码器实现8个led的简单算法的循环点亮2016-10-31 0

-

勇敢的芯伴你玩转Altera FPGA连载57:3-8译码器实验2018-03-26 0

-

请问怎么使用SN74LV4051A搭建一个3,-8译码器?2019-05-09 0

-

用2-4译码器连接为3-8译码器2020-08-23 0

-

求一种在FPGA中使用行为描述语句实现3-8译码器的设计方案2022-07-01 0

-

基于FPGA采用模块化思路设计一个译码器2023-06-20 772

全部0条评论

快来发表一下你的评论吧 !