介绍一种R&S相噪测试方案

描述

随着5G、数据中心和智能驾驶汽车的高速发展,数据传输的速率越来越高。现在最热门的Serdes PAM4技术最高速度到了112Gbps。这对高速数字芯片的设计带来了挑战,特别是时钟信号的抖动分析变得越来越重要,因为到Gbps速率范围,任何一个小的抖动都会对系统性能造成显著影响。

举例来说,高速串行链路参考时钟的稳定度会对误码率有明显影响。对于高速串行数据链路设计,准确测量以及区分由器件噪声产生的随机抖动,以及由非期望干扰产生的周期抖动,非常有助于定位抖动问题来源,提高芯片和系统的性能。

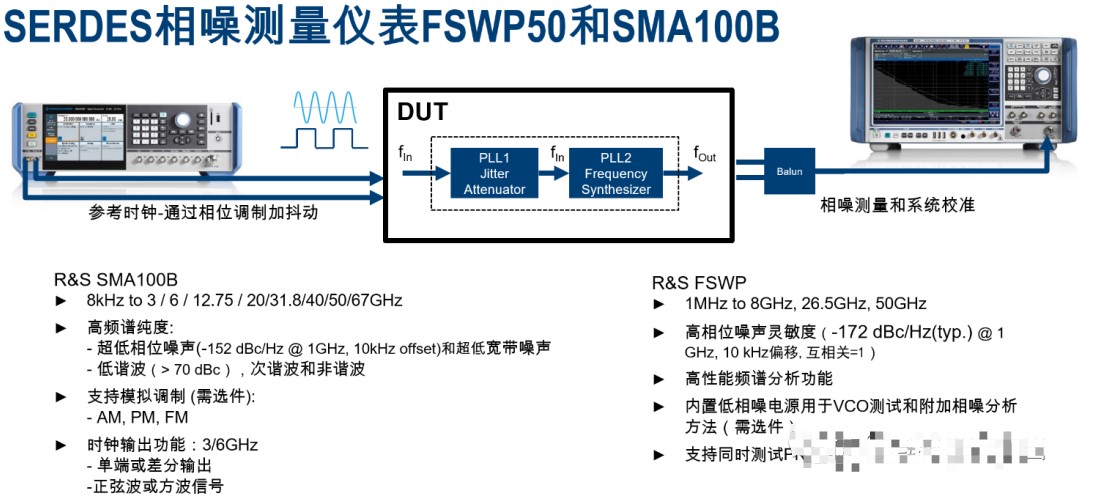

罗德与施瓦茨(以下简称“R&S公司”)Serdes PAM4相噪测试方案具有测试速度快,仪表操作简便的特点。方案核心是R&S 50GHz相噪分析仪FSWP50和提供高精参考时钟的R&S信号源SMA100B。该方案已被国内多家大型芯片设计公司选用。

R&S相噪测试方案

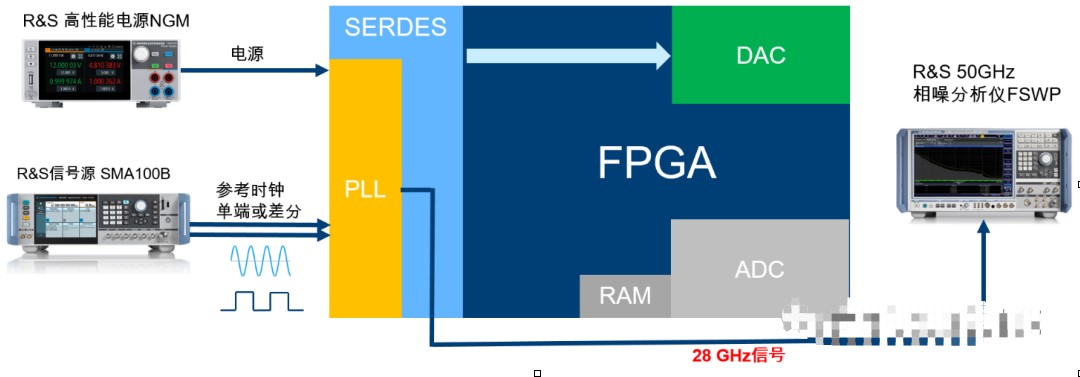

下图是R&S公司提供的相噪测量方案---速率高达112Gbps的Serdes PAM4技术的相噪测量频率在28GHz,让我们一起来看看R&S赋能Serdes PAM4技术的成果。

技术亮点

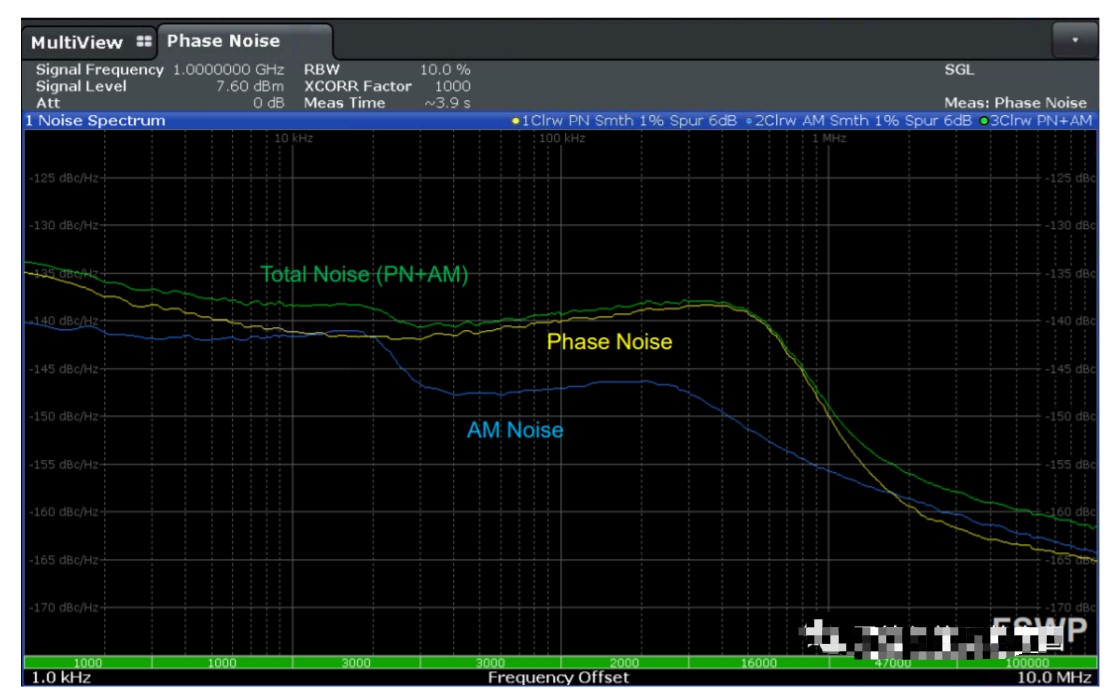

R&S相位噪声分析仪FSWP单表频率覆盖范围高达50GHz,将高性能相位噪声测试仪和频谱分析仪合二为一,使用先进的数字锁相环方法测量相位噪声,提供互相关计算功能,可增加20dB测试动态范围。

FSWP基于其自身极低仪表相位噪声和高效的杂散检测算法,适合进行分辨率要求极高。如Serdes PAM4技术中的时钟源抖动分析,PN和AM同时测试界面如下:

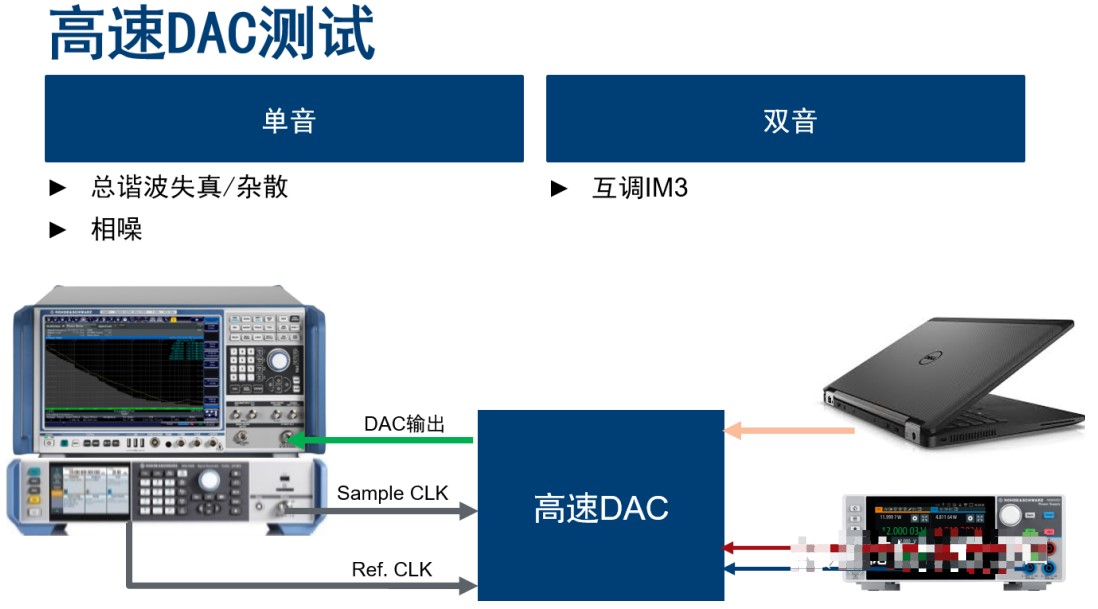

R&S ADC/DAC测试

FSWP和SMA100B也可用于Serdes的ADC/DAC验证和测试,详细测试方案和测试项目如下:

R&S芯片测试

R&S公司是欧洲最大的测试与测量厂家,测试方案覆盖通信、汽车和芯片测试等领域。在芯片领域致力于用高性能的芯片测试与测量解决方案迎接高速数字化带来的挑战,半导体/芯片测试方案主要包括射频芯片测试、分立器件产线测试和数字芯片研发/生产测试解决方案。

未来,R&S公司会推出半导体/芯片测试系列方案,致力于推动中国半导体/芯片产业的测试发展。

责任编辑:lq6

-

R&;S SFU 数字电视测试系统2012-04-20 0

-

Bluetooth基础原理与测试54页PPT讲解(R&;S CBT and R&;S CBT 32 )2015-08-26 0

-

什么是R&;TTE指令?2015-12-08 0

-

用matlab控制R&;S仪器的问题,怎么查找R&;S仪器的指令集呢2016-08-26 0

-

二手销售R&;SCMW270无线测试仪2019-04-02 0

-

安泰测试分享~R&;S预兼容EMI测试解决方案2019-11-19 0

-

二手FSQ40价格/供应R&;S FSQ402020-03-17 0

-

精品仪器介绍R&;S BTC广播电视测试系统2020-07-30 0

-

全新R&;S回收/二手SMA100A信号源2020-10-19 0

-

关于R&;S TS8997认证级测试系统的介绍2021-05-24 0

-

德国R&;S罗德与施瓦茨SGS100A(R&;S)SMA100A信号发生器2021-08-06 0

-

R&;S FSH202021-11-22 0

-

二手CMW270/R&;S无线测试仪出售2021-12-22 0

-

深圳捷扬微电子采用R&;amp;S UWB测试解决方案进行物理层测试2021-07-02 4252

-

R&;amp;S和Applus在EMC测试环境中完成eCall测试2024-01-12 979

全部0条评论

快来发表一下你的评论吧 !