双环集成锁相环频率合成器MBl5U36的性能特点及典型应用分析

描述

作者:谷国栋;田波;张永顺

1 引言

随着无线电技术的迅猛发展,雷达、导航、宇宙飞行、导弹及空间探索工作都需要高稳定度、高精度的频率源。锁相振荡源具有频率稳定度高、相位噪声低、易于集成等突出优点,因而成为通信、雷达、武器制导和电子测量仪器等系统的核心部件。在射频及微波系统中,采用串行码数据输入的数字式电荷泵频率合成器,外接压控振荡器(VCO)和环路滤波器,即可组成锁相(PLL)频率源。它具有电路设计简单、功耗低、可灵活编程控制分频比来调整锁相环路的工作频率等优点,在3GHz以下均可方便地直接构成PLL振荡源。目前,具有代表性的产品是美国国家半导体公司的LMX23XX系列、菲利普公司的UMAl0系列和SA小数分频系列、富士通公司的MB15系列频率合成器。

本文介绍的富士通公司生产的MBl5U36是一种高性能的双环集成锁相环频率合成器,芯片内集成了锁相频率合成器的多种重要部件,使用时只需再合理搭配上一或二块集成电路和少量的外围电路,即可构成一个完整且可靠性很高的频率合成器,该电路的设计简单,应用灵活,且能减小系统体积。

2 MBl5U36的结构及性能

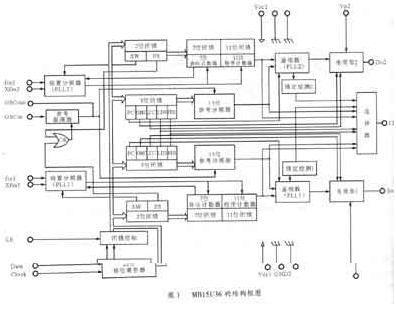

2.1MBl5U36的结构

MBl5U36为串行码数据输入的数字式电荷泵型频率合成器,图1示出其结构框图,两环路组成结构的形式相同,主要包括鉴相器、电荷泵、可编程数字分频器(主程序分频器、参考分频器)、前置分频器等部分。其主要特性如下:最高工作频率1.2GHz(RF2)、2.0GHz(BFl);具有64/65或128/129可选的双模前置分频器;电源电压范围为3.0V~5.5V;电流消耗典型值为6mA;内含平衡式、低泄漏电荷泵;具有节能工作模式。在Vcc=3V时,电流消牦典型值为10μA;采用20引脚SSOP型封装。

2.2 MBl5U36的引脚功能

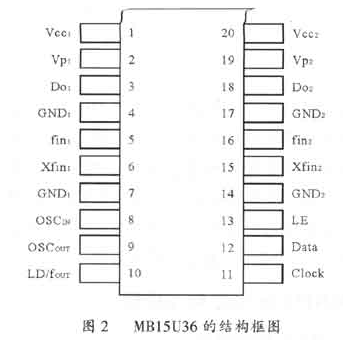

MBl5U36的引脚排列形式如图2所示,括号内的数字为引脚号。

OSGIN(8)和OSCOUT(9)是参考振荡器的输入端和输出端,外接温度补偿晶体振荡器或晶体时,通过交流耦合到输入端。

VCC1(1)是RF1-PLL(频率合成器1)电源电压输入端,电压范围为3V~5.5V,电源滤波的旁蹋器应尽可能靠近该脚,并直接连接到地。

V CC12(20)是RF2-PLL(频率合成器2)电源电压输入端,电压范围为3V~5.5V,电源滤波的旁路器应尽可能靠近该脚,并直接连接到地。

VP1(2)是RF1-PLL电荷泵的工作电压输入端。

VP2(19)是RF2-PLL电荷泵的工作电压输入端。

DO1(3)是RF1-PLL内部电荷泵输出端,可通路滤波器来控制外部VCO。

DO2(18)是RF2-PLL内部电荷泵输出端,可环路滤波器来控制外部VCO。

Fin1 (5)是RF1-PLL的前置分频器输入端,号输入,通过交流耦合形式连接VCO。

Fin2(16)是RF2-PLL的前置分频器输入端,号输入,通过交流耦合形式连接VCO。

Xfin1 (6)是RF1-PLL前置分频器补充输入端接旁路电容器应尽可能靠近该脚,并直接连接到地。

Xfin2(15)是RF2-PLL前置分频器补充输人竭接旁路电容器应尽可能靠近该脚,并直接连接到地。

GND1(4,7)是RF1-PLL接地端。

GND2(14,17)是RF2-PLL接地端。

LD/fOUT(10)是锁定检测输出或相位比较监测输出端,输出方式可通过串行格式编程数据流的LDS和FDS位进行选择。

Clock(11)是22位移位寄存器时钟输入端,数据在时钟的上升沿进入各个寄存器。

Data(12)是串行数据输入端,根据串行格式编程数据流中控制位的设置,数据被传输到相应的锁存器。

LE(13)是使能输入端,当LE端变为高电平时,根据串行格式编程数据流中控制位的设置,移位寄存器中的数据将传送到相应的闭锁。

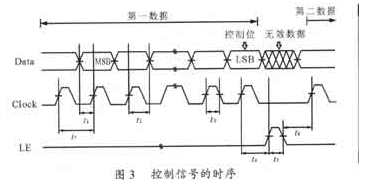

图3示出Clock、Data和LE端的控制信号时序。

3 典型应用

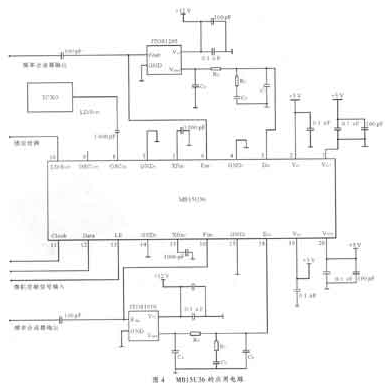

我们采用串行码数据输入的数字式微波频率合成器设计的PLL振荡源,可作为某通信系统干扰机的本振源。以MBl5U36为核心,选择适当的外部VCO,设计相应的环路滤波器,设计构成的低噪声、高稳定度的频率合成器组成框图如图4所示。两个环路锁定在同一个温补参考晶振(TCXO)频率上,各环路分别接各自的VCO及三阶环路滤波器。各环路的分频比、参考分频比率等数据(Data)在基带部分的CPU上设定后,与时钟信号(Clock)、使能信号(LE),按串行格式通过BUS总线一同送入。选用的晶振参考频率为10MHz,环路1输出频率范围为1 720MHz~1 850MHz,频率间隔为200kHz,参考分频比为50,环路总分频比8 600~9 250。环路2输出频率范围为740MHz~960MHz,频率间隔为20kHz,参考分频比为500,环路总分频比37 000~48 000。双模前置分频器工作于64/65模式,MBl5U36内部电荷泵输出误差经环路滤波器后驱动压控振荡器,从而形成锁相环路。

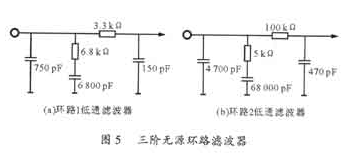

4 环路滤波器设计

频率合成器应保证很低的相位噪声,必须根据指标要求选择高性能的频率合成器、低噪声的VCO及设计滤波特性良好的环路滤波器。环路滤波器的作用是抑制鉴相器输出电压中的载频分量和高频噪声,降低由VCO控制电压的不纯而引起的寄生输出。对电荷泵型的频率合成器,MB15U36推荐使用二阶或高阶无源低通滤波器,图5为三阶低通环路滤波器。我们采用开环增益带宽和相位裕度法推导出滤波器元件计算公式,当环路带宽ωp,VCO的电调灵敏度Kr、主分频比N、鉴相灵敏度Kp及对鉴相频率所需增加的额外衰减A确定以后,可编制出计算三阶环路滤波器的程序,只需输入已知参数,即可得到元件的标称值。其中,N值变化较大,可按N=√N1N2取值,N1从分别为最小和最大环路分频比(例如本文环路2设计中对N的取值采用N= √N1N2=2 261)。利用此程序计算出环路滤波器的元件值,实验证明计算结果可靠,设计的环路滤波器元件值在图中标出。

责任编辑:gt

-

[6.10.1]--案例分析——锁相环频率合成器(视频)李开鸿 2022-11-12

-

锁相环频率合成器的方案研究2010-03-16 0

-

多环锁相频率合成器的设计2010-05-13 0

-

基于单片机和锁相环MC14046频率合成器的设计,求高手指点2012-04-11 0

-

基于锁相环芯片ADF4106的工作特性设计频率合成器2018-09-06 0

-

Milliren Technologies品牌频率合成器产品介绍2019-06-23 0

-

一种基于ADF4106的锁相环频率合成器应用实例介绍2019-07-04 0

-

如何利用FPGA设计PLL频率合成器?2019-07-30 0

-

驱动高压锁相环频率合成器电路的VCO介绍2021-01-11 0

-

如何采用CD4046实现锁相环频率合成器的设计?2021-04-12 0

-

锁相环频率合成器是什么原理?2021-04-22 0

-

MBl5U36有哪些性能?MBl5U36有哪些典型应用?2021-05-28 0

-

怎样去设计一种基于PLL(锁相环)合成器的数字调谐系统2021-08-17 0

-

集成锁相环频率合成器,什么是集成锁相环频率合成器2010-03-23 777

-

频率合成器MBl5U36的结构性能及应用分析2021-05-22 2411

全部0条评论

快来发表一下你的评论吧 !