如何采用ADI的解决方案开发UHFRFID读卡器射频前端?

描述

如何采用ADI的解决方案开发UHFRFID读卡器射频前端

超高频射频识别(UHFRFID)系统已广泛应用于资产管理、服装零售等领域。近年来,它们在无人售货超市和汽车电子标识应用方面也获得了广泛的关注。ADI基于其信号链的UHFRFID读卡器射频前端的两种实现方法。一种实现方法基于ADF9010和AD9963,另一种则基于AD9361。其中基于AD9361的解决方案大大降低了设计复杂度,减少了组件数量和板空间。

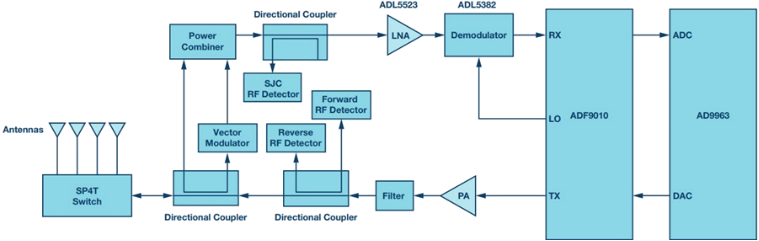

使用ADF9010和AD9963的UHFRFID读卡器RF前端。

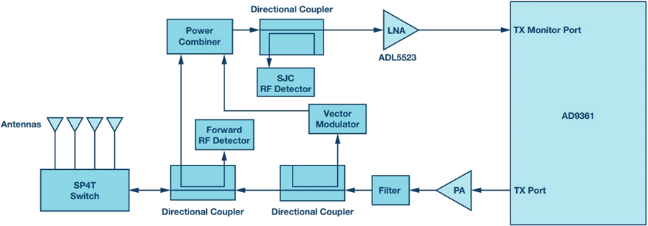

使用AD9361的UHFRFID读卡器RF前端的框图

产品推荐——AD9361

AD9361是一款面向3G和4G基站应用的高性能、高集成度的射频(RF)Agile Transceiver捷变收发器。该器件的可编程性和宽带能力使其成为多种收发器应用的理想选择。该器件集RF前端与灵活的混合信号基带部分为一体,集成频率合成器,为处理器提供可配置数字接口,从而简化设计导入。AD9361接收器LO工作频率范围为70 MHz至6.0 GHz,发射器LO工作频率范围为47 MHz至6.0 GHz,涵盖大部分特许执照和免执照频段,支持的通道带宽范围为200 kHz以下至56 MHz。

设计具有高电压 VCO 的高性能锁相环

随着特征尺寸在集成电路工艺中不断缩小,器件电源电压也呈现出下降趋势。然而,作为PLL的关键元件,压控振荡器(VCO)的实用技术的使用并没有以同样快的速度下行。许多高性能VCO设计仍然采用可能需要高达30V电源电压的离散电路来实现。这给当今的PLL或RF系统设计师带来了严峻的挑战:将低电压PLL IC与更高电压的VCO连接在一起。

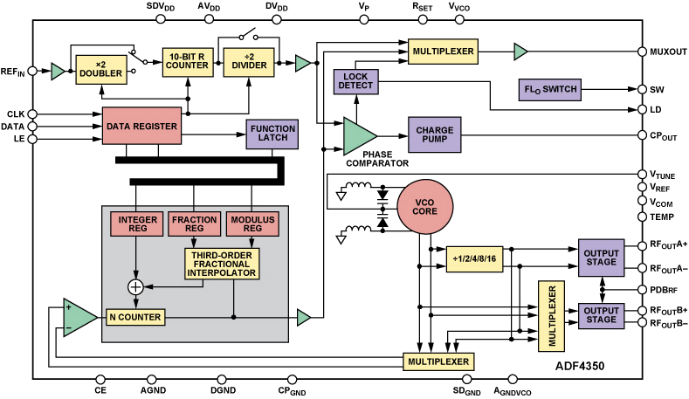

ADF4350PLL频率合成器结构框图

产品推荐——ADF4350

ADF4350结合外部环路滤波器和外部基准频率使用时,可实现小数N分频或整数N分频锁相环(PLL)频率合成器。

ADF4350具有一个集成电压控制振荡器(VCO),其基波输出频率范围为2200 MHz至4400 MHz。此外,利用1/2/4/8/16分频电路,用户可以产生低至137.5 MHz的RF输出频率。对于要求隔离的应用,RF输出级可以实现静音。静音功能既可以通过引脚控制,也可以通过软件控制。

创新集成收发器简化2G至5G基站接收器设计

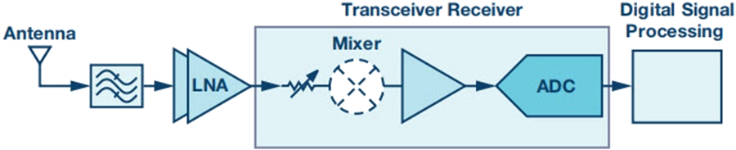

基站接收器设计是一项艰巨的任务。典型接收器组件包括混频器、低噪声放大器 (LNA) 和模数转换器 (ADC) 等,这些器件随着时间推移而不断改善。但是,架构的改变却不大。架构选择的局限性阻碍了基站设计人员向市场推出差异化产品的努力。最近的产品开发,特别是集成收发器,显著降低了最具挑战性的基站接收器设计的一些限制。此类收发器提供的新基站架构使得基站设计人员能够有更多选择和方法来实现产品差异化。

典型收发器/接收器信号链示意图

产品推荐——ADRV9009

ADRV9009是一款高集成度射频(RF)、捷变收发器,提供双通道发射器和接收器、集成式频率合成器以及数字信号处理功能。这款IC具备多样化的高性能和低功耗组合,以满足3G、4G和5G宏蜂窝时分双工(TDD)基站应用要求。

责任编辑:lq6

-

基于FPGA的无线射频读卡器的设计2012-08-06 0

-

射频读卡器2013-08-19 0

-

电脑相关的读卡器2018-09-16 0

-

RFID读卡器射频电路的组成2019-05-29 0

-

高线性度单芯片射频前端解决方案2019-06-25 0

-

USB 2.0读卡器方案设计电路资料分享2020-11-06 0

-

如何采用ADI公司的解决方案开发UHF RFID读卡器射频前端2021-01-08 0

-

求一款多协议射频读卡器的设计方案2021-05-20 0

-

如何研制RFID读卡器射频电路的相关信息?2021-05-21 0

-

基于单片机的射频读卡器2021-07-14 0

-

基于ARM的射频IC卡读卡器设计2009-09-12 501

-

无线射频读卡器的设计和应用2017-11-23 2602

-

探析无线射频读卡器的设计和应用2019-02-28 2925

-

基于ADI的UHF RFID读卡器射频前端的两种实现方法解析2019-10-25 2530

-

采用ADI公司的解决方案开发UHF RFID读卡器射频前端2019-10-25 4101

全部0条评论

快来发表一下你的评论吧 !