如何利用EN脚设计出好电源?

描述

”对于带使能 EN 引脚的 LDO,虽然我们都知道是用来开、关器件,但是您知道如何灵活使用才能达到您想要的可靠电源的设计目标吗?阅读本文您将得到启发,并能举一反三。

1. 以 ZL6205 为例,先简单介绍一下。

致远微电子推出的 ZL6205 系列 LDO,具有低压差(240mV@500mA),较好的输出电压精度(±1%),较大的负载电流特性,同时集成欠压,过流,短路,过温等保护功能。同样 ZL6205 也带 EN 脚,下文就以 ZL6205 为例,结合 ZL6205 内部集成的快速放电电路,举例说明 EN 脚在最常见的两种使能方式下对输出产生的不同效果。

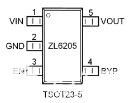

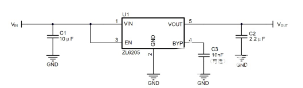

图 1 ZL6205 引脚信息

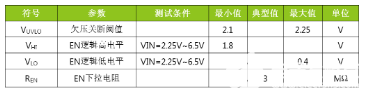

在了解 EN 脚不同使能方式之前,有必要了解下 ZL6205 的一些电气特性。表 1 为 ZL6205 数据手册里的部分电气参数。VUVLO 为 ZL6205 的欠压关断阈值电压,小于这个电压值,芯片处于关闭状态,REN 为内部集成的下拉电阻,EN 悬空时内部拉为低电平。EN 引脚为高电平使能引脚,在推荐的工作电压范围内,VHI 和 VLO 分别为可靠识别的高电平(≥1.8V)和低电平(≤0.4V)。

表 1 相关电气参数

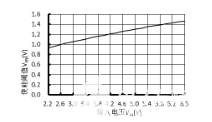

但是表 1 中的 VHI 和 VLO 不是实际的使能电压阈值,图 2 的曲线才是 ZL6205 的在不同输入电压下的实际使能电压阈值,可以看到随着 ZL6205 输入电压的升高,使能电压阈值会跟着升高,但 ZL6205 的使能电压阈值的回滞电压很小。例如 ZL6205 在 VIN=4.2V 的时候,VEN=1.2V 是上电时的使能电压阈值,也是掉电时的禁能电压阈值。

图 2 EN 使能阈值与输入电压的关系

2. 方式一:直接上拉使能

图 3 为电源常见的使能方式,EN 脚与 VIN 脚直接短接。当 ZL6205 上电时,VEN 始终 VIN 相等,有时候 VIN 与 EN 脚间串联一个电阻(常见的数 k 到数十 k),但通常 EN 引脚的输入阻抗较大,ZL6205 的 REN 的阻值为 3MΩ,所以 EN 脚电压信号还是会与 VIN 基本保持一致。

图 3 直接上拉使能

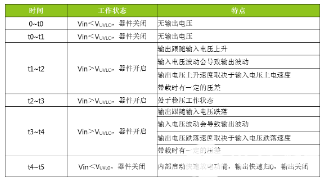

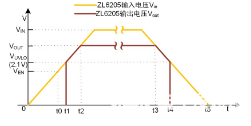

按照上图的电路设计,ZL6205 在轻载时上下电会得到图 4 这样的输入输出电压曲线。这个电路的最大特点就是上下电过程中,输出的开启和关闭完全由芯片固有的欠压阈值 VUVLO(2.1V)控制,而不受 VEN(EN 脚的逻辑阈值电压)控制。各个时间段特点如表 2 所示。上下电过程中输入电压越过 VUVLO 后均有一段输出跟随输入电压的阶段(t1~t2,t3~t4),该电路比较适合输入电压较为稳定,且对输出电压上下电速度要求不高的场合。

表 2 各段时间电压特征说明

图 4 直接上拉使能输入输出电压曲线

3. 方式二:电阻分压使能

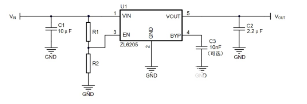

有时候需要 VIN 上升或者跌落到某一电压(不小于 VUVLO)后,才允许 ZL6205 启动输出电压或者关闭输出电压,这样就需要图 5 这样的使能电路。根据图 2 可知,ZL6205 在 VIN=2.2V~6.5V 的输入电压范围内的使能电压阈值 VEN=1.2V±0.3V,这样就可以通过电阻分压来设置 ZL6205 的上电时的启动电压(或掉电时的关闭电压)。

图 5 电阻分压使能

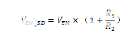

根据图 5 可以得到以下公式。

VEN_SD:上电过程中期望的开启电压点(或者掉电过程中期望的关闭电压点),该值需要大于 VUVLO(2.1V),小于 VIN。

VEN:VEN_SD 电压对应的器件实际使能阈值(可以根据图 2 得到),要求精度不高时,可以统一按照 1.2V 来计算。

例如,对于常用的 3.3V 输出版本的 ZL6205 来说,在电源上下电过程中,希望达到一定的电压值,例如 3.6V,再开启或者关闭 ZL6205。那么这个 3.6V 就是需要设定的电压点 VEN_SD。根据图 2 可知,输入电压为 3.6V 对应的 VEN 为 1.15V。代入上面的公式得 R1:R2=2.13, 电阻 R1 和 R2 需要满足这个比例,结合考虑功耗,稳定性和 EN 输入阻抗,推荐 R1=100k,R2 = 47k。

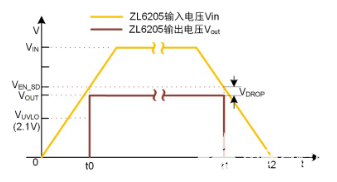

按照上面设计,ZL6205 上下电会得到图 6 这样的输入输出电压曲线。对于常用的 3.3V 输出版本的 ZL6205 来说,3.6V 的 VEN_SD 能满足全负载范围的压差 VDROP 需要。各个时间段特点如表 3 所示。这个电路的最大特点就是上下电过程中,输出的开启和关闭完全由设定的 VEN_SD 来控制,而不受芯片的欠压阈值 VUVLO(2.1V)控制。当设置的 VEN_SD 大于稳态输出电压 VOUT 时,上下电过程很快,看起来几乎是一步到位,而没有输出跟随输入电压的阶段,在输入电压低于 VEN_SD 的阶段无论输入怎么波动都不会影响到输出。所以该电路在输入电压上下电缓慢且不稳定的场合中使用,输出可以获得更加快速且稳定的上下电效果。

表 3 各段时间电压特征说明

图 6 电阻分压使能输入输出电压曲线

4. 其他使能的应用

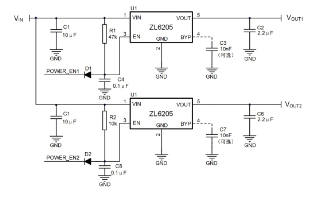

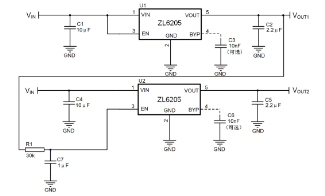

对于电源来说,利用 EN 脚控制输出的方式还有很多。如图 7 所示,该电路可以通过调整 RC 参数(R1 和 C4,R2 和 C8)来调整输出上下电时序,也可以通过外部控制信号 POWER_EN1 和 POWER_EN2 来控制输出电压上下电时序。图 8 则是利用第一路的输出 VOUT1 作为输入信号来控制第二路的输出 VOUT2。从而实现需要的上电时序,这里由于篇幅限制,更多的电源的应用电路和解决方案可访问广州立功科技官网。

图 7 输出电压时序应用电路一

图 8 输出电压时序应用电路二

文章转载来源:https://www.eefocus.com/analog-power/471724

-

LTC2950 EN如何做上拉处理,上拉电源怎么提供?2024-01-03 0

-

学习:电源芯片EN引脚对电机控制板有何影响?2019-10-16 0

-

MPS的低压DCDC芯片的EN脚能不能直接接到5V Vin脚上,不串接电阻2019-12-20 0

-

电源EN脚使用要点相关资料下载2021-11-11 0

-

关于ⅩL4005EN脚失效的2023-03-02 0

-

关于XL4005E1的EN脚失效问题2023-03-03 0

-

请问TJA1043的EN脚悬空会怎样?2023-03-16 0

-

使用TOP256EN设计的40 W笔记本电源的电路图2009-06-21 15518

-

EN5364/EN5394 Enpirion推出效率达93%2009-08-14 1081

-

基于ZL6205的快速放电电路EN脚应用2020-08-30 4102

-

DCDC和LDO电源芯片的使能管脚EN的使用说明2020-10-17 39242

-

一种基于TOP260EN的开关电源设计2021-09-22 722

-

电源芯片使能管脚EN2022-01-05 1320

-

二极管可以设计出好玩的电路2023-03-17 543

全部0条评论

快来发表一下你的评论吧 !