数字集成电路低功耗设计分析器

描述

随着登纳德缩放定律在2005年终结以后,大规模数字集成电路的功耗问题以及由功耗问题衍生而来的散热问题、可靠性问题逐步凸显出来。因此如何有效降低大规模数字集成电路的功耗成为近10年来大规模数字集成电路所面临的最重要挑战之一。

降低功耗的前提是优化设计,而优化设计的前提又是分析到底功耗高在何处。因此,分析功耗是一切的前提。如果学习过数字集成电路与系统设计相关知识的同学应该知道功耗分为静态功耗和动态功耗两部分。其中,静态功耗是由于器件中存在泄漏电流而产生的,只要上电以后就会一直存在。静态功耗可以表征为: 也就是电源电压乘以泄漏电流。初看这个公式,相信大家觉得这不是常识嘛。但问题是泄漏电流又是怎么知道的?泄漏电流一般可以表示为:

也就是电源电压乘以泄漏电流。初看这个公式,相信大家觉得这不是常识嘛。但问题是泄漏电流又是怎么知道的?泄漏电流一般可以表示为: 是不是看着有点晕了?这后面这些乱七八糟的“I ”到底是什么啊……我们就说个最简单的IDS是是亚阈值泄露电流。

是不是看着有点晕了?这后面这些乱七八糟的“I ”到底是什么啊……我们就说个最简单的IDS是是亚阈值泄露电流。

当栅极偏置电压很低时,沟道载流子受源端势垒的影响,泄露电流较小。当源漏端电压升高后,源端势垒降低,导致沟道电流受源漏端电压影响。看到这里,是不是觉得脑袋已经嗡嗡的了?为了避免大家看不下去而导致选手流失,就不能继续分析下去了。我们再来看看动态功耗如何计算吧:

是不是一种看完了以后完全不想说话的感觉……如果我们依靠上面的公式来分析各种低功耗设计方案的正确性,那就太费劲了。有没有一种简单的分析方法能够明确我们设计中采用的多电压域、门控时钟、动态电压频率调节、电源门控等技术是不是有效的降低了功耗,以及是否还有进一步设计优化的空间?这种方法就是不用去直接计算再回头反馈,而是用“规则”和“状态”来判断方法是否有效。

以上提到的低功耗设计方法可以通过UPF(一组TCL命令,所以可以将其简单视为TCL语言的一个特定领域的子集)语言来描述,事实上UPF可以用在IC设计流程的不同阶段并能够完整的描述功耗设计意图。在整个低功耗设计中,电源状态表(Power State Table, PST)可被用来描述各个供电状态(Supply State)之间的相互关系。通过对PST的静态分析可以有效检查Supply State的有效性、冗余性和一致性。进而对整个电源供电网络的状态进行检查优化。

而为方便更多的同学参赛,赛题设置本身降低了相关背景知识的门槛,将赛题抽象为数学算法问题,此外芯华章会提供完整的UPF parser,modeling等相关培训,有利于参赛者能快速上手解题。

赛题要点解析

那么本题要解决的核心要点是什么呢?我们先来看一下赛题描述:

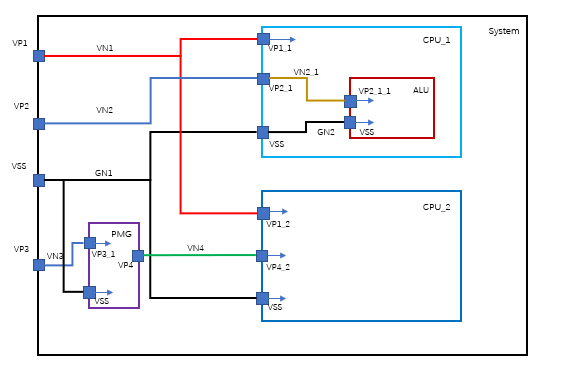

图1一种电源网络供电方案图1展示了一种常见的电源供电网络设计方案(注:仅作为参考而非实际应用电路)。低功耗设计工程师可以根据功耗设计意图来定义电路设计中的每一个供电端口(Supply Port)上的供电状态(Supply State)。

如为上述设计中的VP1, VP2, VSS, VP2, CPU_1/VP1_1, CPU_1/VP2_1, CPU_1/VSS, CPU_1/ALU/VP2_1_1, CPU_1/ALU/VSS, CPU_1/VP1_2, CPU_1/VP4_2, CPU_1/VSS, PMG/VP3_1, PMG/VSS等端口定义供电状态。可以看出,这是大规模数字集成电路中的一种常见的层次化结构。从最顶层的System到最底层的ALU,划分出来3个层次。而在每一个层次中又并列了很多模块。

模块之间的电源网络存在着不同的连接方法,层次间的电源网络又存在包含关系。层次化的方法对于大规模数字集成电路设计具有结构清晰、易于理解的优势。但是最终电源网络是一个整体,这种层次化的状态需要被“展开”为一种平铺的状态。如果说层次化是为了便于设计,那么消除层次化就是为了能够准确分析。因为在真实的电路中并没有所谓的“层次”,尤其是对于电源网络而言,连接到同一电源的所有晶体管其实都是这个电源网络的组成部分而已。因此,进行低功耗分析的第一步自然是将不同的PST进行合并,最终形成一张完整的“大表”。我们可以看到图1可以用五个PST来描述其供电状态。

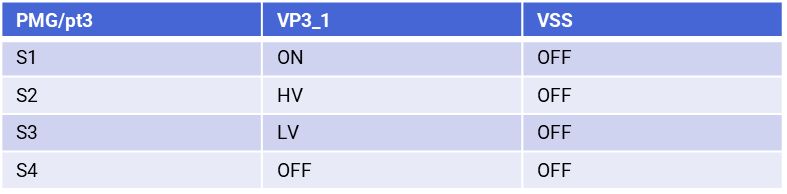

表1. PST of System/PMG

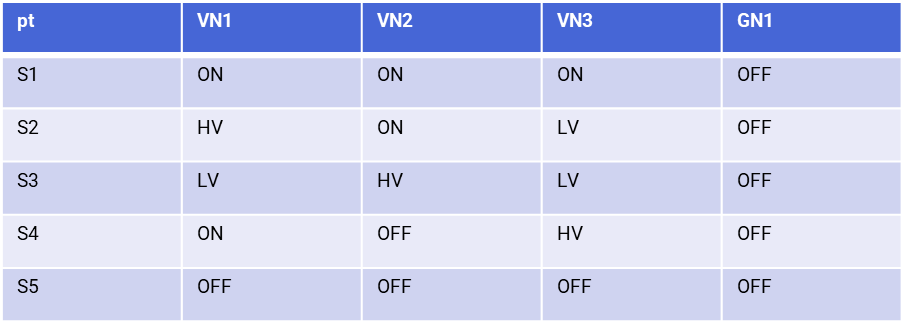

表2. PST of System

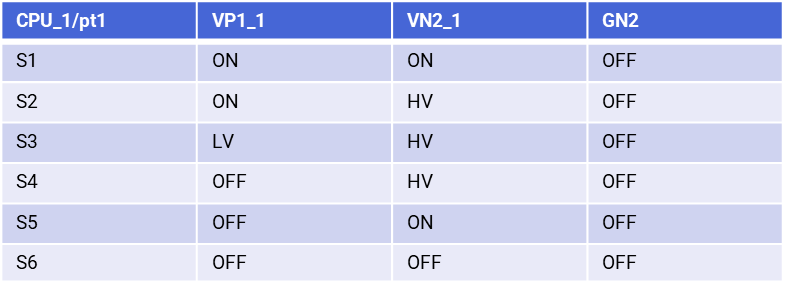

表3. PST of System/CPU_1

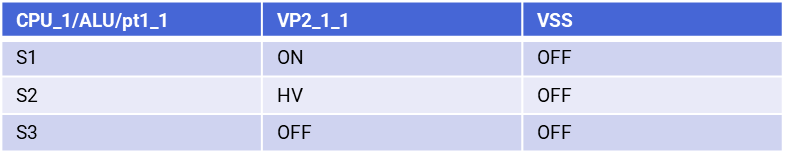

表4. PST of System/CPU_1/ALU

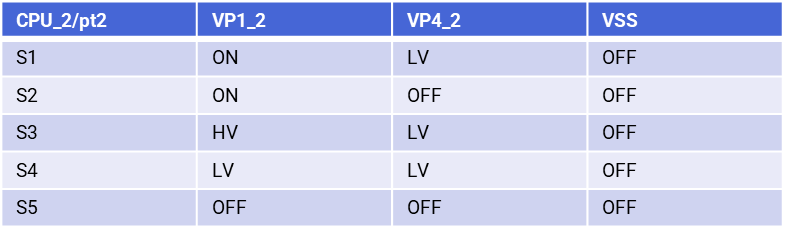

表5. PST of System/CPU_2

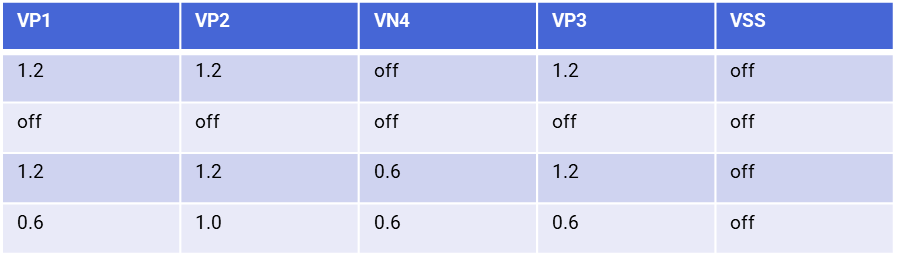

低功耗设计分析器应根据电源供电网络关系,分析并合并不同设计模块下的电源状态表得到供电源(supply source)的PST。最终得到的一张描述整个设计的大表。如在本设计中,应根据表1-5可以得到表6。

表6. 合并后的PST

这样从最终的表6中,我们可以看到不同模块中的几个关键性的电源网络节点的连接情况和供电状态,进而可以根据连接情况和供电状态来做低功耗分析。所以直白一点,本次赛题二的核心点就在于不同PST的解析和合并。由于芯华章已经提供了专门的Parser(解析器),各位参赛选手可以把精力集中于“合并”这一件事情。

建议解题步骤

通过对于赛题要点的分析,我们可以发现赛题二其实只做一件事情:如何将不同的PST按照其对应的连接关系合并为单一的、完整的PST。题目按理说难度并不大。但在赛题发布以后,仍然有不少同学认为题目有相当的难度。

经过分析原因后,我们认为可能主要的难点有两个:首先,除了少部分科研课题和低功耗设计有关的同学外,大部分同学对功耗的成因、计算方法、表针方式等并不是熟悉,对于题目背景的理解有一定的难度;其次,绝大部分同学应该没有接触过UPF和PST,由于对其格式不熟悉而产生了畏难情绪。因此大家在解题之前,首先需要解决的就是对于知识背景的进一步熟悉。

尤其是需要对于UPF的用法和PST的格式有足够的了解。这一点其实并不难做到,因为题目提供了相关的附件以及后续会对这一部分内容重点加强培训,帮助各位同学尽快熟悉UPF和PST。

在熟悉完UPF和PST以后各位同学应该以一个示范性的设计入手,尽快的走通从PST解析到PST合并的全部流程。在这个过程中必然涉及到部分的程序设计、函数调用、数据格式转换等问题,而解决这个问题的过程本身又是对于赛题的进一步熟悉和对UPF以及PST的更进一步的熟悉。再完成以上两步以后,参赛同学可以针对题目要求逐一核对功能是否完成。

在确保功能完备的基础上利用芯华章提供的测试集,不断的加强对所编写程序的检验。除了检验一般性的bug以外,还继续优化程序运行的速度以及占用的空间。最终达耗时更好、占用内存更少的目的。以上解题思路的本质是从简单到复杂,从确保功能到性能优化。符合我们开发软件的一般规律,也符合我们工程研究的一般进程。

其它注意事项

大家在解题时还需要注意以下几点:

不要轻易放弃,题目本身难度不大,但是前期的知识准备要花点时间;

一定要积极参加培训,很多知识其实一点就透,但是在自己没有相关背景的情况下学习还是有一定的挑战性;

要遵循循序渐进、从易到难的解题思路,切不可贪大求全让自己陷入到重重迷雾之中。

最后,预祝各位同学发挥出自己的水平,取得良好的成绩。

责任编辑:haq

-

数字集成电路-电路、系统与设计 免费下载2009-02-12 0

-

数字集成电路速查2011-01-31 0

-

数字集成电路 应用+制作 PDF+22016-09-26 0

-

数字集成电路应用260例2017-02-07 0

-

常用的数字集成电路简介2017-11-06 0

-

什么是数字集成电路IC2021-03-03 0

-

CMOS数字集成电路是什么?CMOS数字集成电路有什么特点?2021-06-22 0

-

数字集成电路设计教学大纲2010-09-20 1039

-

数字集成电路简介2006-04-16 2177

-

数字集成电路的类别2009-09-19 1358

-

数字集成电路_什么是数字集成电路2011-10-28 3852

-

数字集成电路版图提取2011-10-28 1371

-

CMOS数字集成电路:分析与设计(第3版)2016-04-28 1726

-

数字集成电路分析与设计:深亚微米工艺2021-05-12 972

-

芯华章助力集成电路EDA设计精英挑战赛2021-08-10 6233

全部0条评论

快来发表一下你的评论吧 !