Zynq UltraScale + MPSoC的DDR接口

描述

本篇主要针对Zynq UltraScale + MPSoC的DDR接口,从硬件设计的角度进行详细介绍,最后展示一下小编之前自己设计的基于ZU+的外挂8颗DDR4的设计。

目前比较常用的DDR是DDR4和DDR3,其他系列相对使用较少一些,本文主要以DDR4进行介绍。

1、选型

根据ZU+系列芯片的数据手册、TRM、pg150等文档,DDR可以挂载在PS侧,也可以挂载在PL侧,也可同时挂载在PS侧和PL侧。

PL和PS均支持64位的DDR4(不带ECC功能),PL部分如果要支持64位的DDR4,则至少需要提供三个bank的HP接口,只能选择SFVC784或者更高的封装。需要特别说明的是,使用内存颗粒和使用内存条的容量差异较大,需要根据实际需求进行选择。

针对DDR3,其特性如下:

支持DDR3 (1.5V) and DDR3L (1.35V)

容量限制:Support densities up to 8 Gb for components, 32 GB for RDIMMs, 16 GB for SODIMMs, and 16 GB for UDIMMs. Other densities for memory device support is available through custom part selection.

针对DDR4,其特性如下:

容量限制:Support densities up to 32 Gb for components, 64 GB for LRDIMMs, 128 GB for RDIMMs, 16 GB for SODIMMs, and 16 GB for UDIMMs. Other densities for memory device support is available through custom part selection.

DDR接口粗略的介绍可以参见之前的文章《Zynq UltraScale+系列之“外围接口概述”》,PS侧的DDR控制器的详细特性可参看《UG1085》的第17章,PL侧的的相关特性可参考《PG150》、《WP454》等资料,此处不再赘述。

2、Performance

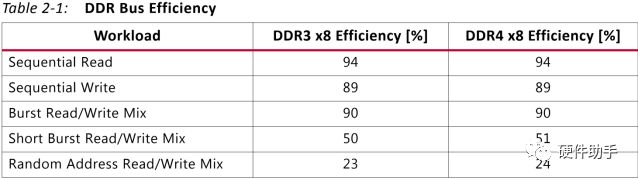

DDR总线的效率在不同的使用模式下差异很大,在实际评估速率时一定要搞清楚使用情况。

针对几种常用的操作模式,《PG150》给出了具体的效率,详见下表:

几种常见的操作模式如下:

Sequential Read

Simple address increment pattern

100% reads

Sequential Write

Simple address increment pattern

100% writes (except for periodic reads generated by the controller for VT tracking)

Burst Read/Write Mix

Repeating pattern of 64 sequential reads and 64 sequential writes

50/50 read/write mix

Short Burst Read/Write Mix

Repeating pattern of four sequential reads and four sequential writes

Full DRAM page accessed in bursts of four before changing the row address for high page hit rate

50/50 read/write mix

Random Address Read/Write Mix

Repeating pattern of two random reads and two random writes

Fully random address for a low page hit rate

50/50 read/write mix

3、原理图设计

PS侧的原理图设计基本没有任何问题,按照对应功能引脚连接即可,PL侧的接口需要特别注意。

对于单个Memory接口,尽量集中使用几个HP bank。如果使用三个bank,两个bank用作数据接口,一个bank用作地址、控制、命令信号线接口,地址、控制、命令信号尽量使用同一个bank,不要跨bank使用;如果使用两个bank,尽量保证数据相关引脚在一个bank,地址和控制信号在另一个bank。

地址、控制、命令信号不能和data共用byte group,只能使用data byte groups以外的byte groups。

CK差分时钟对必须使用差分对,必须连接在控制byte group上,尽量按照Vivado软件对时钟引脚的约束来连接。如果有多个CK对,必须来自于同一个byte lane。

除了DQS和CK之外,其他信号都可以在byte group内随意交换。

前期原理图设计阶段最好在vivado中进行PL侧管脚预分配,别等到PCB出来后才开始在vivado中验证,如果关键信号管脚定义有问题,不能交换,则无法弥补。

4、PCB Guidelines for DDR4 SDRAM (PL and PS)

DDR总线的布局布线需要遵循一些通用的规则,数据线只支持点到点连接,其他信号根据颗粒数量的不同可以有多种拓扑。

ZU+ DDR4 SDRAM支持两种拓扑类型:fly-by和clamshell。Clamshell拓扑在板子空间比较紧张时有一定的优势。在MIG中(PL侧)是一种可选的拓扑,在PS侧不支持clamshell拓扑。

如果使用5片x16的颗粒组成80位宽的接口时,5片DDR的布局采用fly-by topology,如果用9片x8的颗粒,则采用clamshell topology比较节约空间。

由于官方推荐的主线路阻抗较小(单端36/39Ω,差分76Ω),线宽比较宽,但扇出部分阻抗又比较大(单端50Ω,差分86Ω),会导致阻抗突变,因此实际使用中可以通过调整叠层来优化线宽,在满足阻抗要求的同时减小阻抗突变。

4.1.4、Layout Guidelines

以下为DDR4的约束规则,表格中的参数均为最短信号线和最长信号线之间的tolerance参数,数据group一般都是以DQS为TARGET,DQ与DQS进行比较约束。地址、控制、命令group一般都是以CLK为TARGET,ACC(Address、Command、Control)与CLK进行比较约束。

针对上图解释为:例如,最快的ACC信号线传输时间是800ps,最慢的ACC信号线传输时间是840ps,时钟信号线的传输时间应该为862ps±8ps,比ACC总线的中间传输时间(820ps)慢42ps.

CLK和DQS之间的约束比较宽松,最小的差异可以为-879,最大差异可以为+10600,主要是为了保证读写平衡功能从整个菊花链的第一片到最后一片颗粒都正常。

DDR控制器可以调整DQS信号线的内部延迟,由于CK信号线链路连接每一片DDR颗粒,导致CK容性负载更重,所以需要能够调整DQS信号线的内部延迟,以满足和CK之间的约束。

规范规定CK信号线和DQS信号线从FPGA到链路中的第一片DDR颗粒的偏差不小于-149ps,到链路中最远端的DDR颗粒的偏差不大于1796ps。只要链链路中第一片DDR颗粒和最后一片DDR颗粒都满足此条件,整个链路上所有的DDR颗粒的读写平衡功能都将正常。

例如,如果从FPGA到第一片DDR颗粒的DQS延迟为200ps,则从FPGA到第一片DDR颗粒的CK延迟应至少为51ps(200ps-149ps)。如果从FPGA到最后一片DDR颗粒的DQS延迟为700ps,则从FPGA到最后一片DDR颗粒的CK延迟应该小于2496ps(700ps+1796ps)。

下面是一些基本的规则,可以参考遵守:

使用内存条时,CK信号和DQS信号之间的余量会更小一些,因为约束的是FPGA到DIMM插槽处,而颗粒的走线是由DIMM决定的,因此余量预留小一些。

同组的DQ、DQS、DM走线必须在同一层。

DIMM数据线走线最好选择靠近接插件的层,尤其是靠DIMM中间位置的数据组。

采用菊花链结构布线时,ACC信号线可以布在不同的层,但层数越少越好。不要将一个信号切换好几层,主要走线尽量一层走完,这样可以减小串扰,信号换层时,切换过孔附近50mil范围内需要放置一个接地过孔。

FPGA和DDR器件驱动端的阻抗为40Ω,DCI和ODT也是40Ω。因此VTT端接电阻都选为39.2Ω。

当使用内部VREF时,PL侧HP bank上的VREF引脚可以悬空,但不能用于普通IO。

如果系统时钟连接到了DDR的HP bank,则LVDS时钟信号需要外部端接至合适的电压,因为该bank上有不同的逻辑电平 (HSTL, SSTL, or POD)。

对于菊花链布局,人字形扇出(chevron-style routing)可以形成stitching vias;对于比较紧凑的布局,可以通过环抱式扇出形成ground stitch vias。

在器件内部或者周围尽量多放置接地过孔,这样可以更好的为信号提供返回路径,尤其是在边角的位置。

对于ACC信号线的端接电阻布局,应该每四个端接电阻中间穿插布局一个0.1uF的VTT去耦电容,这样可以减小端接VTT的噪声。为了便于布局,最好在原理图中就按每四个电阻放置一个去耦电容。

对于DIMM,去耦电容放置得离DIMM越近越好,这样除了能提供接地过孔外,也能给电源提供低阻抗回路。

以上就是针对ZU+系列MPSoC的DDR接口的详细介绍,PCB设计相关可参考《UG583:UltraScale Architecture PCB Design User Guide》、官方开发板ZCU104、ZCU102、ZCU106等。

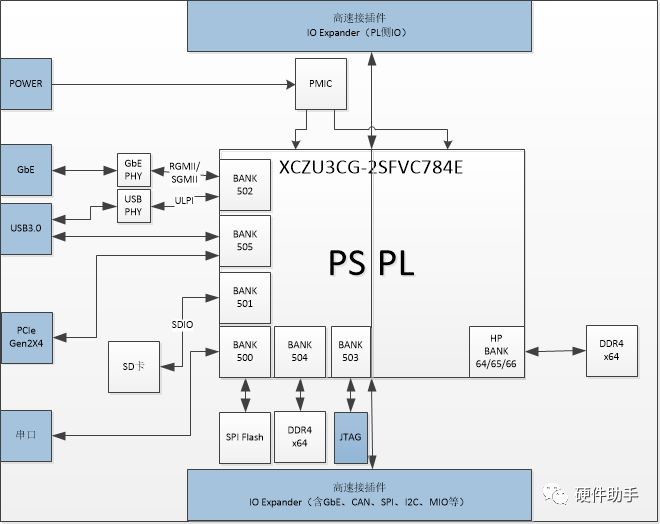

下面介绍一下小编自己设计的基于ZU+(XCZU3CG-SFVC784)的外挂8颗DDR4的设计,采用十层板,板厚1.6mm,最小线宽4mil。板子尺寸120*150mm,单12V电源输入,支持串口、I2C、USB、GbE、TF卡、CAN、PCIe等常用接口,预留PS侧和PL侧IO接口。

硬件框图如下图所示:

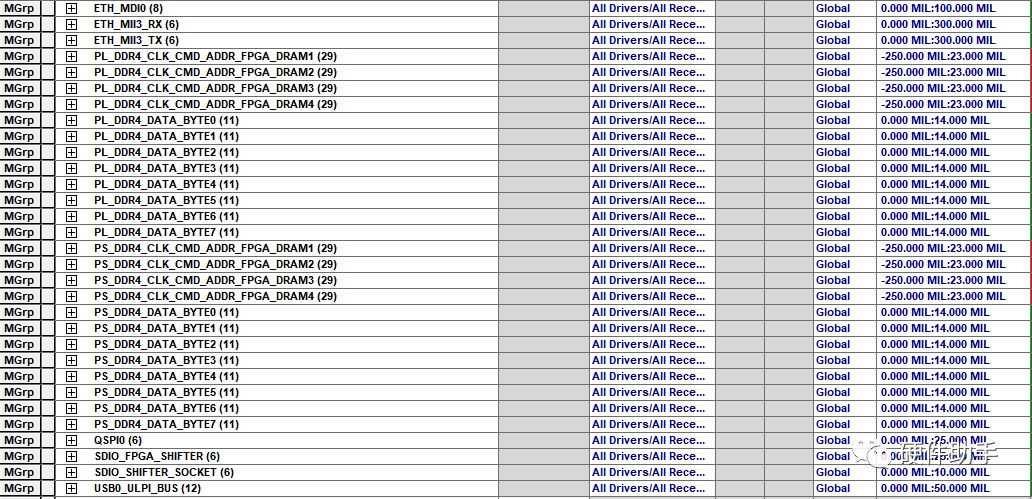

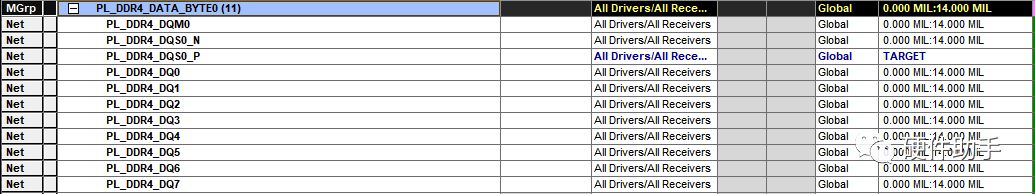

Allegro中的约束规则如下图所示:

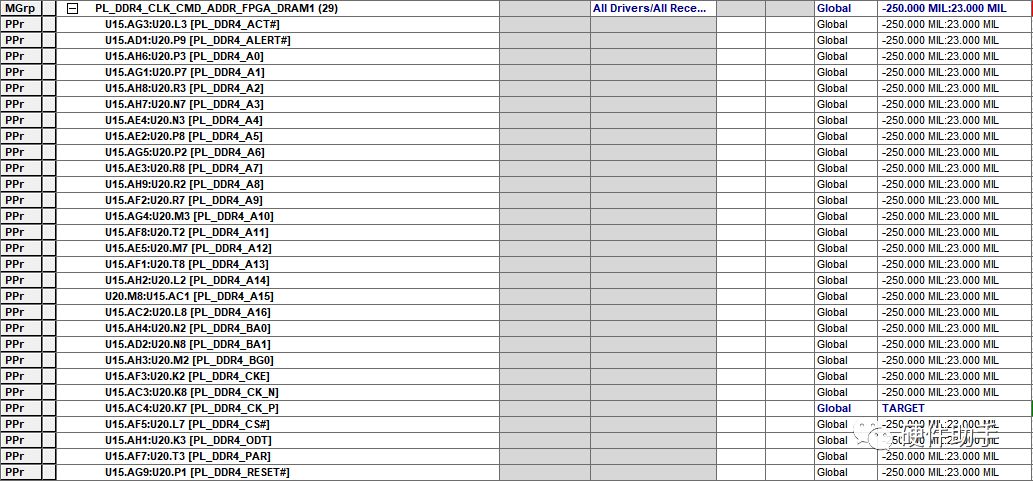

ACC信号线的约束规则如下图所示:

DATA信号线的约束规则如下图所示:

责任编辑:haq

-

fhkj5769

2023-10-07

0 回复 举报你好,请问怎么联系作者 收起回复

fhkj5769

2023-10-07

0 回复 举报你好,请问怎么联系作者 收起回复

-

Zynq UltraScale + MPSoC USB 3.0 CDC器件类设计2019-01-03 0

-

如何利用ZYNQ MPSoC玩DOOM?2019-10-09 0

-

请问Zynq Ultrascale + MPSOC本身是否存在问题?2019-10-14 0

-

如何调试Zynq UltraScale+ MPSoC VCU DDR控制器2021-01-07 0

-

ZYNQ Ultrascale+ MPSOC FPGA教程2021-02-02 0

-

Zynq UltraScale+ MPSoC存储器接口系统的介绍2018-11-29 3088

-

Zynq UltraScale+ MPSoC的发售消息2018-11-27 3313

-

Zynq UltraScale + MPSoC平台的引擎3演示2018-11-22 2782

-

Zynq UltraScale MPSOC数据手册免费下载2019-02-21 1050

-

基于ZU+的外挂8颗DDR4的设计案例分析2020-12-21 7429

-

DDR4的布线设计注意事项和指导2020-12-28 2282

-

如何调试 Zynq UltraScale+ MPSoC VCU DDR 控制器?2021-02-23 1126

-

米尔电子zynq ultrascale+ mpsoc底板外设资源清单分享2022-01-07 519

-

Zynq UltraScale+ MPSoC的隔离设计示例2023-09-13 144

全部0条评论

快来发表一下你的评论吧 !