放大器过压状况的常见原因和影响

描述

当运算放大器的输入电压超过额定输入电压范围,或者在极端情况下,超过放大器的电源电压时,放大器可能发生故障甚至受损。本文讨论过压状况的一些常见原因和影响,为无保护的放大器增加过压保护是如何的麻烦,以及集成过压保护的新型放大器如何能为设计工程师提供紧凑、鲁棒、透明、高性价比的解决方案。

所有电子器件的可耐受电压都有一个上限,超过上限就会产生影响,轻则导致工作暂时中断或系统闩锁,重则造成永久性损害。特定器件能够耐受的过压量取决于多个因素,包括是否安装或意外接触器件、过压事件的幅度和持续时间、器件的鲁棒性等。

精密放大器常常是传感器测量信号链中的第一个器件,因而最容易受到过压故障的影响。选择精密放大器时,系统设计师必须了解放大器的共模输入范围。在数据手册中,共模输入范围可能是用输入电压范围(IVR)、测试条件下的共模抑制比(CMRR)或以上二者来规定。

过压状况的实际原因

放大器需要两种保护:一是过压保护,用以防止电源时序控制、休眠模式切换和电压尖峰引起的故障;二是ESD(静电放电)保护,用以防止静电放电(甚至搬运过程中也可能出现静电放电)引起的故障。安装后,器件可能会受系统电源时序控制,导致重复性过压应力。系统设计师必须想方设法使故障电流避开敏感的器件,或者限制故障电流,使其不致于损坏器件。

在有多个电源电压的复杂分布式电源架构(DPA)系统中,电源时序控制可以使系统电路各部分的电源在不同的时间开启和关闭。时序控制不当可能会导致某个器件的某个引脚发生过压或闩锁状况。随着人们越来越关注能源效率,许多系统要求实现复杂的休眠和待机模式。这意味着,在系统的某些部分已关断的同时,其它部分仍然可能处于上电和活动状态。与电源时序控制一样,这些情况可能会导致无法预测的过压事件,但主要是在输入引脚上。

许多类型的传感器会产生意想不到的、与它们要测量的物理现象无关的输出尖峰,这类过压状况一般仅影响输入引脚。

静电放电是一种广为人知的过压事件,常常发生在安装器件之前。它造成的损害非常广泛,以至于业界主要规范,如JESD22-A114D等,不得不明确如何测试和规定半导体耐受各类ESD事件的能力。几乎所有半导体产品都包含某种形式的集成保护器件。应用笔记AN-397(标准线性集成电路的电诱发损坏:最常见起因和防止再发生的相关处理)是一篇很好的参考文献,详细讨论了这一问题。出现高能脉冲时,ESD单元应进入低阻抗状态。这不会限制输入电流,但能提供到供电轨的低阻抗路径。

一个简单的案例研究:电源时序控制

随着混合信号电路变得无处不在,单一PCB上的多电源需求也变得非常普遍。关于新设计需要考虑的一些微妙问题,特别是需要许多不相关的电源时,请参阅应用笔记AN-932(电源时序控制)。

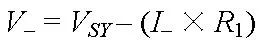

精密放大器可能会成为这种状况的受害者。图1显示了一个配置成差分放大器的运算放大器。放大器通过RSENSE检测电流,并提供与相应压降成比例的输出。必须采取措施,确保由R3和R4构成的分压器将输入偏置在额定IVR范围内的某处。如果放大器的电源电压不是从VSY获得,并且VCC在VSY之后出现,则A1反相输入端的电压为:

其中I–由无电源时A1的输入阻抗决定。如果放大器不包含过压处理设计,则最有可能的电流路径是通过ESD二极管、箝位二极管或寄生二极管流向电源或地。如果此电压超出IVR范围,或者电流超过数据手册规定的额定最大值,器件可能会受损。

ADA4091和ADA4096等过压保护放大器所用的ESD结构不是二极管,而是DIAC器件(双向“交流二极管”),这使得此类放大器即使没有电源也能承受过压状况。

图1. 差分放大器高端电流传感器。如果VSY先于VCC上电,放大器的输入电压或电流可能会超过数据手册规定的最大值。

运算放大器中的故障状况

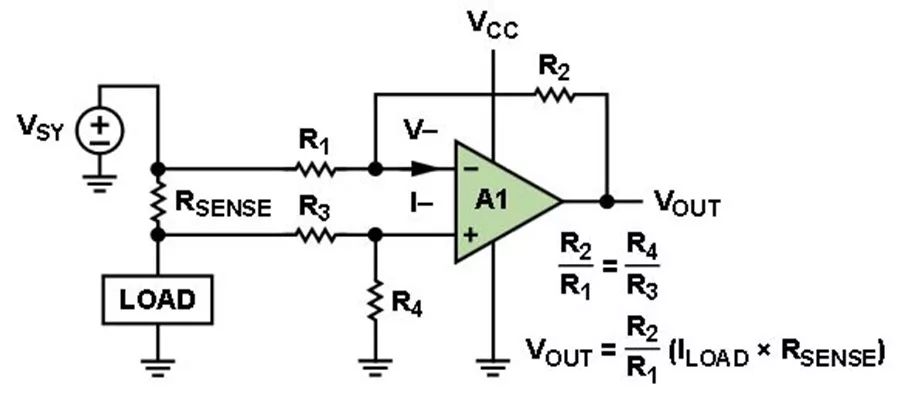

图2显示了一个N沟道JFET输入级(J1、J2、R1和R2),后接一个第二增益级和输出缓冲器(A1)。当开环放大器在其额定IVR范围内时,差分输入信号(VIN+ – VIN–)与VDIFF 180度异相。连接为单位增益缓冲器时(如图所示),如果VIN+的共模电压超过放大器的IVR,J1的栅极-漏极进入未夹断状态并传导整个200 μA级电流。只要J1的栅极-漏极电压仍然反向偏置,VIN+的进一步增加就不会导致VDIFF变化(VOUT仍然处于正供电轨)。然而,一旦J1的栅极-漏极变为正偏,VIN+的进一步增加就会提高A1反相输入端的电压,导致输入信号与VDIFF之间发生不需要的反相。

图2. N沟道JFET输入运算放大器结构示意图

图3显示了A1输出端反相的一个示例。与双极性输入放大器不同,JFET放大器的输入未箝位,因而易发生反相。CMOS放大器的栅极与漏极电隔离,一般不会发生反相。如果确实会发生反相,运算放大器制造商一般会在数据手册中说明。下列条件下可能发生反相:放大器输入端不是CMOS,最大差分输入为VSY,数据手册未声明不会发生反相。虽然反相本身不是破坏性的,但它能导致正反馈,进而使伺服环路不稳定。

系统设计师还必须关注放大器输入超出电源范围时会发生什么。这种故障状况通常发生在电源时序控制导致一个源信号先于放大器电源激活时,或者在开启、关闭或工作中电源出现尖峰时。对于大多数放大器,这种状况是破坏性的,尤其是如果过压大于二极管压降。

图4显示了一个带ESD保护二极管和箝位二极管的典型双极性输入级。在缓冲器配置中,当VIN+超过任一电源轨时,ESD和箝位二极管就会正偏。这些二极管的源极阻抗非常低,源极支持多少电流,二极管就能传导多少电流。精密放大器(如AD8622等)提供少许差分保护,输入端串联500 Ω电阻,施加差分电压时,该电阻可限制输入电流,但它只能在输入电流不超过额定最大值时提供保护。如果最大输入电流为5 mA,则允许的最大差分电压为5 V。注意,这些电阻并不与ESD二极管串联,因而无法限制流向电源轨的电流(例如在过压期间)。

图5显示一个无保护双极性运算放大器在同时施加差分输入和过压情况下的输入电流与电压的关系。一旦施加的电压超过二极管压降,电流就可能损害、降低运算放大器的性能,甚至破坏运算放大器。

外部输入过压保护

从半导体运算放大器问世之初,IC设计师就不得不权衡芯片架构与应对其脆弱性所需的外部电路之间的关系。故障保护一直是最棘手的问题(例如,请参阅MT-036——“运算放大器输出反相和输入过压保护”和MT-069——“仪表放大器输入过压保护”)。

系统设计师之所以需要精密运算放大器,是因为它有两个重要特性:低失调电压(VOS)和高共模抑制比(CMRR),这两个特性能够简化校准并使动态误差最小。为在存在电气过应力(EOS)的情况下保持这些特性,双极性运算放大器经常内置箝位二极管,并将小限流电阻与其输入端串联,但这些措施无法应对输入电压超过供电轨时引起的故障状况。为了增加保护,系统设计师可以采用图6所示的电路。。

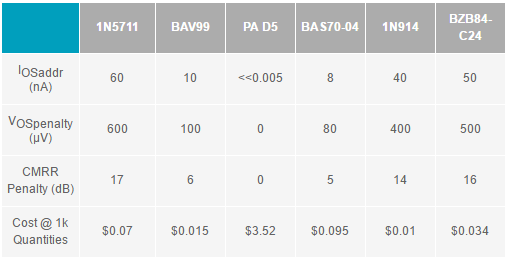

如果VIN处的信号源先行上电,ROVP将限制流入运算放大器的电流。肖特基二极管的正向电压比典型的小信号二极管低200 mV,因此所有过压电流都会通过外部二极管D1和D2分流。然而,这些二极管可能会降低运算放大器的性能。例如,可以利用1N5711的反向漏电流曲线(见图7)来确定特定过压保护电阻造成的CMRR损失。1N5711在0 V时的反向漏电流为0 nA,在30 V时为60 nA。对于0 V共模电压,D1和D2引起的额外IOS取决于其漏电流的匹配程度。当VIN被拉至+15 V时,D1将反向偏置30 V,D2将偏置0 V。因此,额外的60 nA电流流入ROVP。当输入被拉至–15 V时,D1和D2的电气位置交换,60 nA电流流出ROVP。在任意共模电压下,保护二极管引起的额外IOS等于:

图7. 1N5711反向电流与连续反向电压之间的关系

由公式2可计算出极端共模电压下的VOS损失:

使用1N5711在30 V时的漏电流60 nA以及5 kΩ保护电阻,两个极端共模电压下的VOS将增加300 μV,导致整个输入电压范围内的额外ΔVOS为600 μV。根据数据手册,一个具有110 dB CMRR的运算放大器将损失17 dB CMRR。插入反馈电阻来均衡源阻抗只能在共模电压为0 V时有帮助,但无法防止整个共模范围内产生额外的IOS。表1显示了保护精密放大器常用的一些二极管的计算结果。对于CMRR损失计算,假设使用5 kΩ保护电阻。所有成本都是来自www.mouser.com的最新美元报价(2011)。

表1. 常用保护二极管及其对110 dB CMRR精密运算放大器的影响

图6所示的方法可能还有一个缺点,那就是保护二极管会将过压电流分流到电源中。例如,如果正电源无法吸收大量电流,过压电流就可能迫使正电源电压提高。

防止这一现象的一种方法是在正输入与地之间使用背靠背齐纳二极管,如图8所示。超过D1或D2的齐纳电压时,二极管将过压电流分流到地,从而保护电源。这种配置能够防止过压期间的电荷泵效应,但齐纳二极管的漏电流和电容高于小信号二极管。此外,齐纳二极管的漏电流曲线具有软拐点(soft-knee)特征。在放大器的共模范围内,这会带来额外的CMRR损失,如前所述。例如,BZB84-C24是一个背靠背齐纳二极管对,工作电压范围为22.8 V至25.6 V,反向电流额定值为50 nA(最大值,16.8 V时),但制造商并未说明接近齐纳电压时的漏电流是多少。此外,为实现更陡的击穿特性,齐纳二极管一般采用比小信号二极管掺杂更重的扩散工艺制造,这就导致寄生电容相对较高,因而失真(特别是在幅度较高时)和失稳的可能性更高。

早期集成过压保护

上面讨论了放大器的一些常用外部保护方法的缺点。如果放大器本身的设计能够耐受较大的输入过压,那么其中的一些缺点是可以避免的。图9显示了差分输入对采用的常见集成保护方案。

在该电路中,两个放大器输入端均有输入保护电阻。虽然一般情况下只有一个输入端需要过压保护,但使各输入端的寄生电容和漏电流均衡可以降低失真和失调电流。此外,二极管不必处理ESD事件,因而可以相对较小。

增加电阻,无论是外置还是内置,均会增加放大器的和方根(RSS)热噪声(公式4):

如果使用1 kΩ电阻来保护噪声为4 nV/√Hz的运算放大器,总电压噪声将提高√2倍。集成保护电阻并不能改变过压保护会提高等效输入电压噪声的事实,但将R1和R2与运算放大器集成在一起可确保数据手册的噪声规格包括保护电路。为了避免权衡噪声与过压,需要这样一种保护电路:当放大器输入在额定范围内时,它提供低电阻;当放大器输入超过供电轨时,它提供高电阻。这种特性将能按需改善过压保护,降低正常工作时的总噪声贡献。图10显示了一种具有该特性的电路方案。

Jxy全部是P沟道JFET,它们是耗尽型器件,因此沟道的掺杂类型与源极和漏极相同。当放大器输入电平介于两个供电轨之间时,J1A和J2A是简单的电阻,阻值等于RDSON,因为输入偏置电流足够小,沟道与栅极之间的任何电位差都不会使沟道关闭。如果VIN-超出负电源一个二极管压降,电流就会流过J1A,导致漏极关闭。这种转换实际上是J1A离开三极工作区,进入线性工作区。如果VIN+超出正电源一个二极管压降,J1A将充当横向PNP。VIN+至栅极将用作正偏射极-基极结,另一个结用作基极-集电极,其高阻值避免输入管过压。

图11中的电流-电压曲线显示了FET保护运算放大器在受到过压扫描时的输入阻抗变化。保护FET的RDSON为4.5 kΩ;当放大器的正输入被拉至供电轨以上时,保护FET的电阻迅速提高到22 kΩ(30 V时),从而将输入电流限制为1.5 mA。

集成的优势

ADA4091和ADA4096等放大器证明,实现鲁棒的输入过压保护对运算放大器的精度影响非常小(如图10所示)。ADA4096能够提供与电源电平无关的32 V过压保护,从而无需虽然廉价但会大幅降低放大器精度的外部器件,或者虽然精密但成本高于放大器本身的外部器件。

ADA4096-2的集成保护使PCB尺寸大幅缩小,其影响已包括在运算放大器的技术规格中。即使未施加电源,它也能保护放大器(见图13)。此外,ADA4091和ADA4096具有轨到轨输入和输出特性(RRIO),在整个过压保护范围内都不会发生反相(见图14)。这些优势使得系统设计师可以少担心电源时序控制和闩锁问题。

结论

总而言之,集成过压保护具有许多优势:

提高模拟信号链的鲁棒性和精度

缩短产品上市时间(TTM)、设计时间,降低测试要求

降低BOM(物料清单)成本

核准器件清单所需的器件更少

PCB尺寸更小、密度更高

故障率更低

责任编辑:haq

-

功率放大器,超声功率放大器定义分类和应用2017-12-15 0

-

常见设计问答之仪表放大器2018-10-17 0

-

电流检测放大器的差分过压保护电路2018-11-01 0

-

运算放大器输出相位反转和输入过压保护PDF2018-11-05 0

-

放大器振荡的常见原因以及补救方法2019-01-04 0

-

【模拟对话】运算放大器输入过压保护:箝位与集成2019-09-29 0

-

运算放大器在电压保护中的作用2019-10-08 0

-

运算放大器输入过压保护:箝位与集成2019-10-13 0

-

运算放大器如何防止过压?哪种电阻值可用于低噪声应用?2021-03-05 0

-

运算放大器过压状况的原因是什么?有什么影响?2021-04-06 0

-

导致反馈放大器振荡的原因是什么?2021-04-07 0

-

请问如何防止放大器输出出现过压的电路?2021-04-12 0

-

鲁棒的放大器提供集成过压保护2012-11-02 1580

-

放大器会发生振荡两种常见原因浅析2017-03-05 526

-

运算放大器造成过压状况的常见原因和影响分析2019-10-18 6864

全部0条评论

快来发表一下你的评论吧 !