开源工具SkiDL - 用Python来描述电路

描述

我们用Verilog、VHDL这种硬件描述语言来设计FPGA,是否有一种方式来描述电路?如果采用了这种方式,也会像HDL在FPGA、ASIC领域一样成为一种主流的趋势么?我们来看看SkiDL的尝试。

SKiDL 是一个模块,允许您使用 Python 紧凑地描述电子电路和组件的互连。 生成的 Python 程序执行电气规则检查以查找常见错误并输出用作 PCB 布局工具输入的网表。

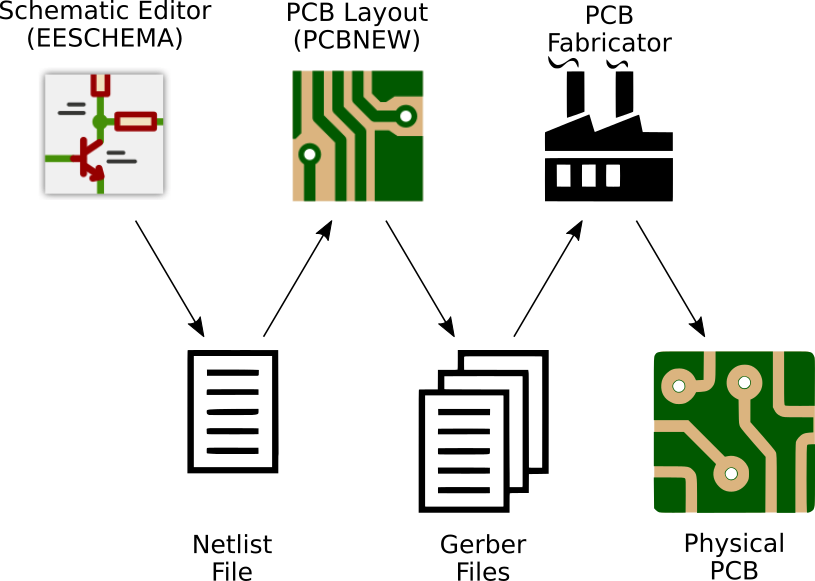

首先,让我们看看 KiCad 中的“正常”设计流程:

在这里,您在原理图编辑器(对于 KiCad,即 EESCHEMA)中开始并绘制原理图。由此,EESCHEMA 生成一个网表文件,其中列出了使用的组件以及它们的引脚如何互连。然后,您将使用 PCB 布局工具(如 KiCad 的 PCBNEW)来排列零件封装并绘制连接网表中指定的引脚的线迹。

完成后,PCBNEW 会输出一组 Gerber 文件,这些文件将发送给 PCB 制造商,该制造商将创建物理 PCB 并将其运送给您。然后你会在 Twitter 上张贴他们的照片,然后因为你对这个项目感到厌烦而立即把它们扔进抽屉里几年。

在基于 SKiDL 的设计流程中,您使用文本编辑器创建 Python 代码文件,该文件使用 SKiDL 库来描述组件的互连。该代码文件由 Python 解释器执行,并输出一个网表文件。从那里开始,设计流程与基于原理图的流程相同(包括将 PCB 倾倒在抽屉中)。

那么,您为什么要使用 SKiDL?以下是 SKiDL 为电子设计带来的一些功能:

只需要一个文本编辑器和 Python。

具有强大、灵活的语法(因为它是 Python)。

允许对电子电路进行简洁的描述(考虑不要通过多页原理图跟踪信号)。

允许电子电路的文本描述(考虑对电路使用 diff 和 git)。

对常见错误(例如,未连接的设备 I/O 引脚)执行电气规则检查 (ERC)。

支持电子设计的线性/分层/混合描述。

促进设计重用(考虑使用 PyPi 和 Github 分发电子设计)。

可以创建其行为/结构以参数方式改变的智能电路模块(考虑根据您所需的截止频率自动调整组件值的滤波器)。

可以使用任何 ECAD 工具(只需要两种方法:一种用于读取零件库,另一种用于输出正确的网表格式)。

利用 Python 生态系统的所有优势(因为它是 Python)。

免费软件:MIT 许可证。

开源:https://github.com/devbisme/skidl

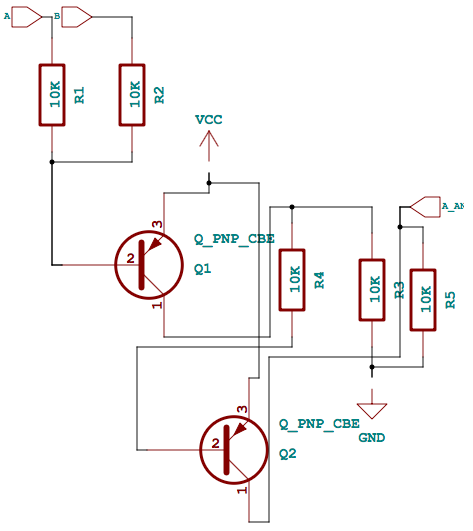

生成原理图:

尽管 SKiDL 可以让您避免繁琐的原理图绘制,但有些人仍然希望看到他们电路的图形描述。为此,SKiDL 可以使用 1) graphviz DOT 语言或 2) 作为使用 SVG 的更传统的示意图将部件的互连显示为有向图。

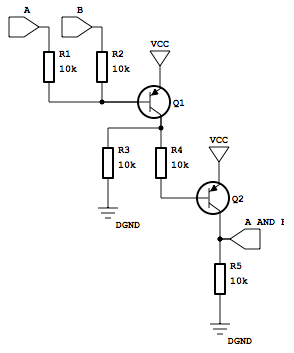

以下电路将用于说明这两种方法:

The SKiDL script for this circuit is:

from skidl import *

# Create part templates.

q = Part(lib="Device.lib", name="Q_PNP_CBE", dest=TEMPLATE, symtx="V")

r = Part("Device", "R", dest=TEMPLATE)

# Create nets.

gnd, vcc = Net("GND"), Net("VCC")

a, b, a_and_b = Net("A"), Net("B"), Net("A_AND_B")

# Instantiate parts.

gndt = Part("power", "GND") # Ground terminal.

vcct = Part("power", "VCC") # Power terminal.

q1, q2 = q(2)

r1, r2, r3, r4, r5 = r(5, value="10K")

# Make connections between parts.

a & r1 & q1["B", "C"] & r4 & q2["B", "C"] & a_and_b & r5 & gnd

b & r2 & q1["B"]

q1["C"] & r3 & gnd

vcc += q1["E"], q2["E"], vcct

gnd += gndt

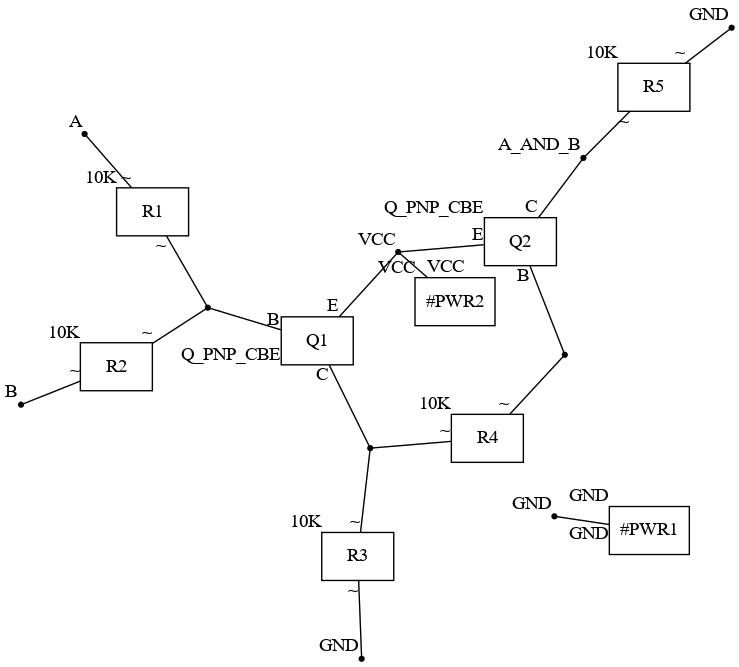

点图

注意:查看 DOT 文件需要您在系统上安装 graphviz。

要为电路生成 DOT 文件,只需将以下内容附加到脚本末尾:

generate_dot(file_='and_gate.dot')

运行脚本生成and_gate.dot文件后,您可以使用以下命令将其转换为位图文件:

dot -Tpng -Kneato -O and_gate.dot

生成的 and_gate.dot.png 文件如下所示:

这张图可以作为一个小电路的健全性检查,但你可以想象如果它包括具有数百个引脚的微控制器或 FPGA 会是什么样子!

另外你可以生成SVG格式的原理图

也可以将现有的KiCad设计转换到SkiDL

也可以使用SkiDL来描述你的电路,并运行SPICE进行仿真。

我对这个了解得很少,只是觉得它值得关注,先分享出来,供有兴趣的朋友参考。

-

python开发工具推荐2018-04-12 0

-

专业python web编程工具2018-06-12 0

-

10大Python工程师必知开发工具盘点2018-06-14 0

-

用Python来守护邮箱2019-06-20 0

-

Python 界面工具--Kivy 初尝试2020-06-18 0

-

自学python单片机编程-单片机可以使用Python语言来控制了! 精选资料分享2021-07-14 0

-

能否用Python语言来控制单片机进行实现对机器人的操控呢2021-08-20 0

-

如何使用开源标准以及工具来创建系统级环境2021-11-05 0

-

怎样使用IDE来调试开源工具呢2022-01-18 0

-

Python硬件验证——摘要2022-11-03 0

-

如何使用Python包装器正确构建OpenVINO工具套件2023-08-15 0

-

Python汉字拼音转换工具2023-02-24 574

-

网络工程师学Python-开源自动化部署工具Fabric2023-04-28 516

-

关于两个Python开源识别工具的效果2023-10-17 291

-

Python的优雅之处:Descriptor(描述符)2023-11-02 700

全部0条评论

快来发表一下你的评论吧 !