eFPGA异军突起,IP模式才是未来?

eFPGA异军突起,IP模式才是未来?

电子说

1.2w人已加入

描述

在硬件加速器应用中,FPGA常被视为最优解,提供极致加速性能的同时,还具备重新编程的能力。尽管其灵活性成了FPGA的一大特色,但大批量生产FPGA的价格可不低。此外,FPGA作为传统的处理器加速方案,工程师必须要解决空间、I/O延迟和带宽之类的问题。

而近些年来,eFPGA(嵌入式FPGA)的概念正在不断兴起。与将芯片与必要的I/O和电源管理电路封装在一起的FPGA不同,eFPGA推行的是卖IP模式。任何厂商都可以将这些eFPGA IP放入自己的定制IC产品内,无论是ASIC、SoC还是SiP。也正因为eFPGA的种种优势,国外不少厂商都想借eFPGA率先抢占市场。

Flex Logic

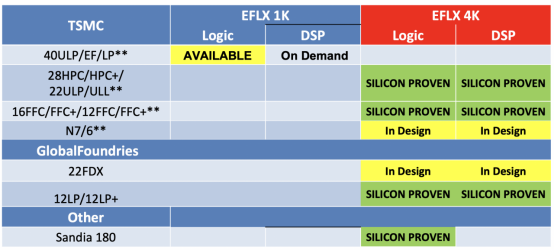

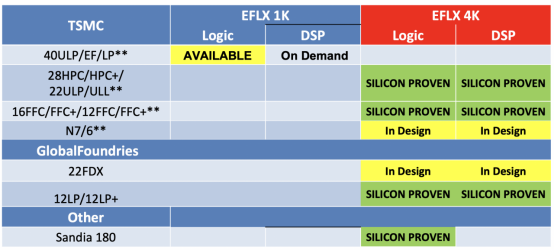

Flex Logic作为最早入局eFPGA的企业之一,已经投入了7年的研发,且eFPGA在2020年正式开始盈利,并与Dialog、大唐电信和波音等企业达成了合作。Flex Logic的EFLX eFPGA IP基本已经覆盖了主流的成熟工艺,比如Sandia美国国家实验室的180nm、格芯的12nm以及台积电的40nm、28/22nm、16/12nm,已完成了十数种芯片的流片。不仅如此,Flex Logic宣称格芯的22FDX和台积电的7/6nm也已经在设计阶段,下一步就是进军5nm。

EFLX eFPGA工艺节点 / Flex Logic

在Flex Logic看来,传统独立FPGA芯片+SoC的方案所需的功率太大,且多数需要高速SERDES或PCIe与其他芯片进行I/O互联。这种方案不仅功率过大,也因为SERDES/PHYS的存在带来了一定的面积成本,而eFPGA却可以做到低功耗、低成本和小面积,并将100K LUT塞入复杂的SoC设计中。而且在继承了FPGA可编程的特性后,即便是已经安装完成的产品,EFLX核心也可以用来升级I/O协议、改变加密算法等等。

InferX X1 / Flex Logic

eFPGA在重构时间上同样具备优势,因而在复杂的神经网络模型中更为适用。比如Flex Logic的AI推理芯片,InferX X1,在测试中,神经网络模型层级的动态重构只需6微秒。这使得InferX X1在具备ASIC性能的同时,也能对新的模型做出动态化处理,非常适合作为主处理器的加速器或协处理器,用于要求低功耗高性能的边缘AI市场。

这样的动态重构也为eFPGA带来了更多的应用方向,比如自动驾驶中的传感器融合方案,针对激光雷达、毫米波雷达和视觉等不同传感器数据进行处理。还有不同的PWM频率要求的多电机方案,在其中提供电机控制器支持。亦或是需要多不同指令集架构的CPU进行动态切换,比如ARM、RISC-V和ARC等。

Achronix

同样踏足eFPGA市场的还有美国公司Achronix。Achronix的Speedcore可以做到750MHz的峰值频率,且已经支持了台积电16nm、12nm和7nm三个成熟制程节点,也可以移植到其他节点上。

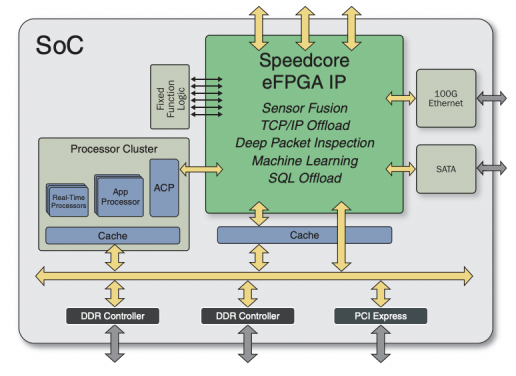

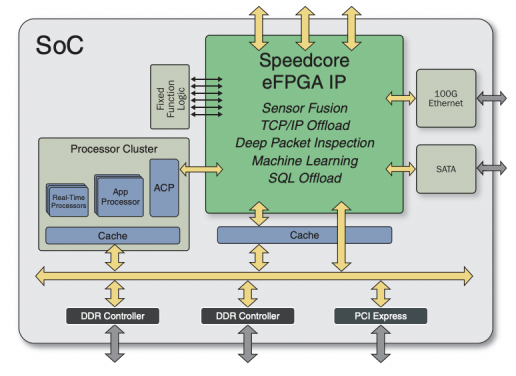

Speedcore / Achronix

Achronix非常看好eFPGA在汽车市场的机遇,尤其是当下汽车开发周期缩短,又要支持10年以上的生命周期。我们以特斯拉这种开始走自研ASIC方向的厂商为例,与其他现成组件相比,虽然需要投入一定的开发成本,但ASIC提供的整体成本和性能都是最优的。与此同时,选择ASIC路线也带来了一定的风险。

首先,ASIC方案必须要对自己的方案有着清楚的认知。特斯拉的FSD ASIC开发历时近三年,如果这之后摄像头ISP需要更新,GPU需要支持浮点而不是FP32,都需要对ASIC架构的大改,很可能会进一步延长后续车型的生产,这也是为何少有汽车厂商选择该技术路线的原因。而将eFPGA IP集成在ASIC中,就为这些厂商提供了FPGA的嵌入式硬件编程能力,又不会像独立FPGA那样加大成本和功率。

小结

eFPGA还有不少优势,比如在加密和保护上,不仅可以支持各种加密算法,也可以保护IP资产被逆向工程。虽然几年前刚面世之际,eFPGA还是一个不成熟的技术,并没有在芯片设计领域产生多大的吸引力。随着几年的发展下来,经过晶圆厂的生产认证,设计流程和软件的完善,加上AI和自动驾驶的兴起,eFPGA已经成了一个可行的方案。但在ARM的IP厂商的前人经验下,eFPGA能否真正崛起,还需要等待更多的市场验证。

打开APP阅读更多精彩内容

而近些年来,eFPGA(嵌入式FPGA)的概念正在不断兴起。与将芯片与必要的I/O和电源管理电路封装在一起的FPGA不同,eFPGA推行的是卖IP模式。任何厂商都可以将这些eFPGA IP放入自己的定制IC产品内,无论是ASIC、SoC还是SiP。也正因为eFPGA的种种优势,国外不少厂商都想借eFPGA率先抢占市场。

Flex Logic

Flex Logic作为最早入局eFPGA的企业之一,已经投入了7年的研发,且eFPGA在2020年正式开始盈利,并与Dialog、大唐电信和波音等企业达成了合作。Flex Logic的EFLX eFPGA IP基本已经覆盖了主流的成熟工艺,比如Sandia美国国家实验室的180nm、格芯的12nm以及台积电的40nm、28/22nm、16/12nm,已完成了十数种芯片的流片。不仅如此,Flex Logic宣称格芯的22FDX和台积电的7/6nm也已经在设计阶段,下一步就是进军5nm。

EFLX eFPGA工艺节点 / Flex Logic

在Flex Logic看来,传统独立FPGA芯片+SoC的方案所需的功率太大,且多数需要高速SERDES或PCIe与其他芯片进行I/O互联。这种方案不仅功率过大,也因为SERDES/PHYS的存在带来了一定的面积成本,而eFPGA却可以做到低功耗、低成本和小面积,并将100K LUT塞入复杂的SoC设计中。而且在继承了FPGA可编程的特性后,即便是已经安装完成的产品,EFLX核心也可以用来升级I/O协议、改变加密算法等等。

InferX X1 / Flex Logic

这样的动态重构也为eFPGA带来了更多的应用方向,比如自动驾驶中的传感器融合方案,针对激光雷达、毫米波雷达和视觉等不同传感器数据进行处理。还有不同的PWM频率要求的多电机方案,在其中提供电机控制器支持。亦或是需要多不同指令集架构的CPU进行动态切换,比如ARM、RISC-V和ARC等。

Achronix

同样踏足eFPGA市场的还有美国公司Achronix。Achronix的Speedcore可以做到750MHz的峰值频率,且已经支持了台积电16nm、12nm和7nm三个成熟制程节点,也可以移植到其他节点上。

Speedcore / Achronix

Achronix非常看好eFPGA在汽车市场的机遇,尤其是当下汽车开发周期缩短,又要支持10年以上的生命周期。我们以特斯拉这种开始走自研ASIC方向的厂商为例,与其他现成组件相比,虽然需要投入一定的开发成本,但ASIC提供的整体成本和性能都是最优的。与此同时,选择ASIC路线也带来了一定的风险。

首先,ASIC方案必须要对自己的方案有着清楚的认知。特斯拉的FSD ASIC开发历时近三年,如果这之后摄像头ISP需要更新,GPU需要支持浮点而不是FP32,都需要对ASIC架构的大改,很可能会进一步延长后续车型的生产,这也是为何少有汽车厂商选择该技术路线的原因。而将eFPGA IP集成在ASIC中,就为这些厂商提供了FPGA的嵌入式硬件编程能力,又不会像独立FPGA那样加大成本和功率。

小结

eFPGA还有不少优势,比如在加密和保护上,不仅可以支持各种加密算法,也可以保护IP资产被逆向工程。虽然几年前刚面世之际,eFPGA还是一个不成熟的技术,并没有在芯片设计领域产生多大的吸引力。随着几年的发展下来,经过晶圆厂的生产认证,设计流程和软件的完善,加上AI和自动驾驶的兴起,eFPGA已经成了一个可行的方案。但在ARM的IP厂商的前人经验下,eFPGA能否真正崛起,还需要等待更多的市场验证。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

- 相关推荐

- efpga

-

掌握这几步充分发挥eFPGA性能,SoC架构师都懂的选型技巧2019-07-04 0

-

嵌入式 FPGA (eFPGA) 时代已到!浅谈FPGA技术的过去、现在和未来2021-11-09 0

-

嵌入式FPGA的发展前景如何2021-12-27 0

-

三星LED异军突起 MOCVD订购量称霸全球2010-03-15 608

-

一文读懂eFPGA 选择是要注意的四个步骤2018-06-29 2123

-

解密:Achronix 7nm eFPGA的设计方法2018-11-30 2960

-

eFPGA的工作方式与FPGA芯片类似 其中有可编程互连2018-12-23 1334

-

32位MCU异军突起 8位MCU何去何从2019-01-07 10646

-

eFPGA是什么?几个关于eFPGA的常见迷思2019-01-27 8571

-

对于eFPGA该如何选择2019-07-29 594

-

Achronix宣布其Speedcore eFPGA IP核出货量超千万个2021-03-26 1926

-

浅谈集成FPGA的两种方式:eFPGA(SoC)& cFPGA(SiP)2021-08-16 6487

-

eFPGA异军崛起 IP模式会是未来嘛2021-11-17 1444

-

为什么嵌入式FPGA(eFPGA)IP是ADAS应用的理想选择?2023-07-10 259

-

基于Speedcore eFPGA IP构建Chiplet2023-09-06 264

全部0条评论

快来发表一下你的评论吧 !