如何估算LC电路的Q值

模拟技术

2285人已加入

描述

图3.4中有一个与信号源相串联的电阻,这个电阻可以作为任何门电路驱动被测信号时的输出阻抗的模型。对于TTL或高性能的CMOS驱动器,这个源端阻抗大允为30欧。对于ECL系统,输出阻抗大约为10欧。

LC电路的Q值,或者说谐振因子,受被测信号的源端电阻影响很大。对于L、C和源端的电阻RS的串联组合,其串联谐振电路的Q值近似为:

在上式中,Q值是存储在回路中的总能量与每弧度振荡损耗能量的比值。一个高Q值的电路在受到外界激励时,会持续较长时间的振铃。该揩振在电路的频率响应上表现为一个大的尖峰。

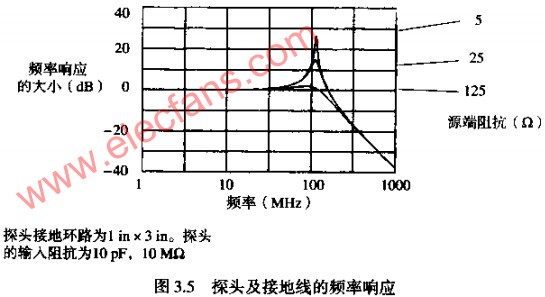

在图3.4所示的电路中,当我们减小源端电阻RS时,LC滤波器会在100MHZ附近产生较大的谐振。图3.5中所示的频率响应曲线,显示了源端电阻分别为5欧,25欧和125欧时的情形。

5欧的源端电阻,会产生29DB的谐振。截止频率超过100MHZ的数字信号,会因这个探头的电路而产生较大畸变。

15欧的源端电阻会产生15DB的谐振,截止频率超过100MHZ的数字信号,会因这个探头的电路产生畸变。

125欧的源端电阻,对电路有相当大的衰减,几乎消除了谐振。

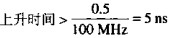

如果用图3.4所示的这个探头测量转折频率小于100MHZ的数字信号,则没有不良的振铃和过冲发生,式( )告诉我们,上升时间应该大于5NS才能保证截止频率低于100MHZ:

)告诉我们,上升时间应该大于5NS才能保证截止频率低于100MHZ:

对于这个特定探头装置,5NS上升时间的限制是其200NH接地回路电感和10PF并联电容一个函数。

本文地址:http://www.elecfans.com/article/analog/2010/20100603218913.html

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

请问反馈型LC振荡器的Q值怎么推导出来的?2016-06-16 0

-

【转帖】浅析LC谐振电路和LC振荡电路2018-12-07 0

-

LC串联谐振和并联谐振Q值的问题?2019-05-06 0

-

【电路精选】LC振荡电路2019-07-18 0

-

LC滤波电路的电感电容如何选择?感值容值应该多大?2021-02-22 0

-

单项全桥整流LC滤波电路的电感电容值该如何确定呢?2023-04-06 0

-

lc选频电路2009-03-12 10119

-

LC振荡灭弧电路2009-07-17 1874

-

实用LC振荡电路2010-04-17 2824

-

lc振荡电路是如何起振的_lc振荡电路起振条件及调试2018-01-22 32437

-

基于ROBDD的电路功耗估算方法2018-03-12 811

-

lc振荡电路和lc谐振电路有什么区别?lc振荡电路的原理及特点详解2018-07-18 91039

-

LC并联谐振电路和LC串联谐振电路2020-10-20 55575

全部0条评论

快来发表一下你的评论吧 !