WCDMA信道编解码任务调度方案

WCDMA技术

描述

0 引言

WCDMA支持高速率传输,并且同时满足不同速率和质量要求的业务复用。这就要求信道编解码模块必须采用一种灵活的业务复用方案,高效、动态的进行多信道处理。而由于终端设备在功耗、实时性及存储要求等方面的特殊性,使整个系统的实现变得更加复杂。

随着DSP处理器和大规模FPGA技术在近些年的高速发展,DSP+FPGA的硬件架构能完全支持上述这些复杂技术的实现。但由于该硬件架构需要相应的软件支持才能发挥它们的性能,所以寻求一种有效的软件方案是实现整个信道编解码模块的关键。本文结合WCDMA一帧多时隙[3]的特点,给出了一种基于时隙来灵活调度各处理模块的中断任务处理方案,该方案充分发挥DSP在任务实时调度方面的优势,使整个系统的硬件资源得到最大的利用,执行效率得到尽可能的提升,并且系统功耗在一定程度上能得到有效降低。

1 WCDMA终端侧信道编解码的描述

终端侧信道编解码模块包含上行编码复用链路和下行解码复用链路。

根据3GPP TS25.212协议,WCDMA系统上行链路复用和信道编码的过程为:传输块经过CRC校验后进行信道编码,编码后的数据进行第一次交织和速率匹配,然后对多个传输信道的数据复用并进行第二次交织,最后映射到相应的物理信道。如果进行多码传输,则在传输信道复用以后还需进行物理信道的数据分割。

每个数据块集从上层到达传输信道的时间间隙(TTI)上都附有相关的处理参数(TFI)。信道编解码模块根据TFI的信息查表计算出关于从CRC开始到速率匹配的各个环节的处理参数。当有多个传输信道复用到物理信道时,物理层对不同传输信道的TFI信息进行排序得到传输格式组合(TFCI),它描述了各个传输信道的复用关系。同时经过速率匹配的多个传输信道的数据按照TFCI进行相应的串行复用处理,组成一个编码合成传输信道(CCTrCH),并进行第二次交织后把CCTrCH映射到物理信道。

下行链路的解码复用链和上行链路的复用链结构大致相同,只是对应上行链路每个编码模块,下行链路都提供一种相应的逆处理模块。与上行链路不一致的是速率匹配模块和无线帧合并模块所处的位置不同于上行链路,并增加了固定或可变比特位置的DTX处理。

2 基于时隙的任务调度研究

本文给出的基于时隙的任务调度方案是基于DSP+FPGA的硬件架构之上。DSP实现任务的控制与调度,FPGA完成各处理子模块的具体实现,并且这些模块为各信道所共享。

2.1 基于时隙的任务调度方案原理描述

根据WCDMA信道编解码的协议说明,信息流分成为多个传输块以TTI周期为单位进行发送和接受,整个信息流的处理由DSP根据接受的中断触发不同的任务来完成。在本方案*采用两个DSP中断:一个是时隙(Slot)中断,中断周期为667us;另一个是帧(Frame)中断,中断周期为10ms。两个中断有不同的优先级,时隙中断的优先级高于帧中断。本文基于时隙的任务调度方案就是以这两个中断为参考,周期性的定位出时隙任务。

时隙中断的主要任务是通过中断触发将10ms分为15等分,每次中断根据上下行编解码流程的不同环节,调度运行FPGA中不同的功能子模块,对于在一个577us时间内不能完成的功能子模块,监控其运行的状态以控制整个流程的运行。帧中断的任务就是通过中断触发,周期性地把一个TTI周期以10ms帧为单位进行划分。

2.2 WCDMA终端侧编解码模块执行机制

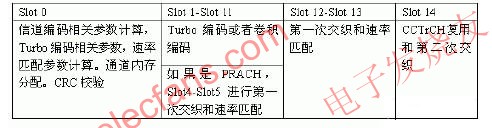

在一个TTI周期为10ms的通路中上行编码各阶段所占用的时隙分配如表1。该TTI周期所需的信道编码参数在该slot 0确定,并且由传输格式半静态参数和动态参数计算出Turbo或卷积的编码参数和速率匹配参数。

表1 WCDMA终端侧上行编码链路流程时隙分配

Slot 1-Slot 11进行多个信道的卷积编码或Turbo编码,多个信道共享Turbo编码器和卷积编码器,DSP在每个slot中断查询编码器的状态,当有编码器处于空闲状态并且有信道需要进行编码时,DSP调度编码器为该信道服务。

Slot 12-slot 13进行第一次交织和速率匹配,第一次交织有三个独立的模块,可以同时进行三个信道的交织,DSP根据各个信道的处理流程控制使用。

Slot 14进行CCTrCH的复用和第二次交织。

当上行传输信道TTI不等于10ms时,上行处理流程有些变化。TTI中的第一帧按照表1进行相关流程动作,在TTI后面的几帧中,由于CRC校验和Turbo编码或卷积编码已经在第一帧中完成,所以只要进行第一次交织与速率匹配、第二次交织与信道复用。

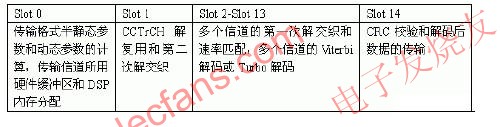

在一个TTI等于10ms的下行链路中,解码各阶段所占用的时隙分配如表2。各时隙的执行调度机制与上行编码链路类似。

表2 WCDMA终端侧下行解码链路流程时隙分配

当TTI不等于10ms时, 首先在TTI中的第一帧中必须进行参数计算与内存分配,然后在TTI的前面几帧中进行第二次解交织与信道解复用、第一次解交织与速率匹配,在该TTI最后的一帧中才进行Viterbi解码或Turbo解码,以及CRC校验和数据输出。

在整个上下行链路并行处理的过程中,由于各子处理单元是通过FPGA模块化实现的,某一时刻未被调用的子模块,DSP都将关闭它们的时钟,使其处于休眠状态,当它们被再一次调用时,DSP重新启动时钟。这样通过节省各模块的执行时间使系统功耗得到降低。

3 方案实现与性能测试

在实现过程中我们采用以TEAK[5]为内核的DSP处理芯片,这一方面有利于最后ASIC的集成,另外作为一款32位的处理器,它具有灵活多样的寻址方式,提供巨大的处理能力。FPGA采用Xilinx公司的VirtexII XC2V6000[6],它具有丰富的资源,强大的输入输出能力。

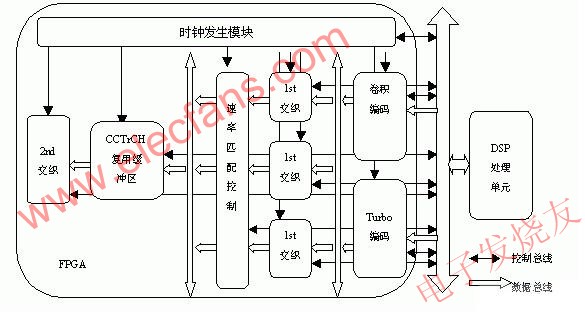

根据本方案针对这个系统所提出的流程结构和执行机制,本文列出了上行链路的数据处理流程图(见图1)。根据上行数据处理的特点,将整个上行链路的信道解码过程分割为三个主要环节:卷积编码或TURBO编码、第一次交织和第二次交织。经过CRC处理的数据块根据TFCI的编码方式分别输入给卷积编码器或者TURBO编码器;经编码后的数据写入第一次交织器输入缓冲区,第一次交织器有3个独立的模块,可以同时进行三路传输信道的交织。在把数据从第一次交织输出缓冲区写入第二次交织输入缓冲区的过程完成了CCTrCH的复用。

图1 WCDMA终端侧信道编解码上行链路信号流图

FPGA完成信道解码中的各个具体模块的实现,并且每个功能模块提供相应的控制接口。DSP通过这些控制接口对各硬件模块进行参数配置、任务调度,从而控制多个下行传输信道的解码过程,并能够最大限度的调度各个功能模块为多个传输信道服务,这样实现了各个功能模块为多个传输信道所共享,提高同时处理多路下行信道的能力。整个流程充分考虑到了DSP和FPGA各自的优缺点,通过软硬件的相互配合,协同处理来提高整个系统的性能。

下行链路和上行类似,DSP完成任务调度和模块配置,FPGA完成下行各解码子模块的具体实现。

最后,我们采用对两种业务进行复用来实现平台的环回测试。整个平台通过把上行链路的第二次交织输出缓冲区与下行链路的第二次解交织输入缓冲区进行连接,实现上行编码链路和下行解码链路的环回。两个业务中一个是速率为12.2kbps,TTI为20ms,采用卷积编码的低速率话音业务;一个是速率为384kbps,TTI为10ms,采用Turbo编码的高速率业务。整个测试过程连续进行了两个小时,结果语音环回声音清晰,高速率数据环回测试误码率小于10e-6,这样的结果完全满足了3GPP所规定的实现要求。

测试表明本方案不仅在高速率业务的处理上符合规范要求,而且对不同类型的业务复用处理有较强的适应能力,达到了WCDMA的基本性能要求。同时,由于在运行过程中对空闲子模块采用了休眠处理,使整个系统模块在运行过程中大大降低功耗,充分考虑了移动终端的特殊要求。

4 结束语

通过灵活调度业务复用中各个环节的处理子模块,本文提出的基于时隙的任务调度方案实现了WCDMA终端侧信道编解码的处理。作为一个ASIC的验证平台,利用本方案,可以降低系统的功耗,增加模块的可扩展性,从而更有利于系统的开发和维护。

-

为什么需要视频编码,它的原理又是什么?第二集#视频编解码 #视频编解码面包车 2022-07-29

-

数字音视频编解码技术与标准2008-06-04 0

-

基于CPLD的CMI编解码电路的设计与实现2010-05-06 0

-

基于Kinetis L实现的G.726语音编解码方案2022-12-09 0

-

WCDMA无线资源信道配置2009-06-01 297

-

WCDMA关键技术2009-06-02 928

-

Turbo 码及交织技术在WCDMA 的信道编码方案中的应用2009-08-24 806

-

Turbo码及交织技术在WCDMA的信道编码方案中的应用2009-08-25 650

-

一种有效的WCDMA信道编解码任务调度方案研究2009-08-26 343

-

基于DSP实现WCDMA信道估计2009-09-15 360

-

什么是音频编解码器?2009-05-03 3901

-

WCDMA承载分组数据的传输信道有哪些2009-06-15 1834

-

基于FPGA的8B/10B编解码设计2011-05-26 3399

-

四路编解码电路原理图2016-05-11 513

-

通信接口——编解码2017-09-04 751

全部0条评论

快来发表一下你的评论吧 !