《Xilinx—UG471中文翻译》(2)ISERDESE2原语介绍

电子说

描述

1.前言

本文仅对UG471 第3章《Advanced SelectIO Logic Resources》部分进行翻译和学习解读。

其他部分,后续补充。

水平所限,有不足之处,欢迎拍砖。

2.ISERDESE2原语介绍

SERDESE2是专用的串并转换器,它在完成串并转换时并不会带来多余的时序上的问题,从而很适合应用到高速源同步应用中。比如摄像头数据。

专用解串器/串并转换器

它可以完成高速数据传输同时不需要FPGA端匹配数据频率,这个转换器支持SDR(single data rate)和DDR(double data rate)。SDR模式支持2-,3-,4-,5-,6-,7-,8bit位宽;DDR模式支持4-,6-,8-bit位宽。10或14-bit需要两个级联。

Bitslip 子模块

该子模块可以使设计者重新排列输入的并行数据。可用于源同步tranining。

- 对strobe-based 类型存储接口的专用支持

- 对networking接口的专用支持

- 对DDR3接口的专用支持

- 对QDR接口的专用支持

- 对异步接口的专用支持

3.原语例化

ISERDESE2 #(

.DATA_RATE("DDR"), // DDR, SDR

.DATA_WIDTH(4), // Parallel data width (2-8,10,14)

.DYN_CLKDIV_INV_EN("FALSE"), // Enable DYNCLKDIVINVSEL inversion (FALSE, TRUE)

.DYN_CLK_INV_EN("FALSE"), // Enable DYNCLKINVSEL inversion (FALSE, TRUE)

// INIT_Q1 - INIT_Q4: Initial value on the Q outputs (0/1)

.INIT_Q1(1'b0),

.INIT_Q2(1'b0),

.INIT_Q3(1'b0),

.INIT_Q4(1'b0),

.INTERFACE_TYPE("MEMORY"), // MEMORY, MEMORY_DDR3, MEMORY_QDR, NETWORKING, OVERSAMPLE

.IOBDELAY("NONE"), // NONE, BOTH, IBUF, IFD

.NUM_CE(2), // Number of clock enables (1,2)

.OFB_USED("FALSE"), // Select OFB path (FALSE, TRUE)

.SERDES_MODE("MASTER"), // MASTER, SLAVE

// SRVAL_Q1 - SRVAL_Q4: Q output values when SR is used (0/1)

.SRVAL_Q1(1'b0),

.SRVAL_Q2(1'b0),

.SRVAL_Q3(1'b0),

.SRVAL_Q4(1'b0)

)

ISERDESE2_inst (

.O(O), // 1-bit output: Combinatorial output

// Q1 - Q8: 1-bit (each) output: Registered data outputs

.Q1(Q1),

.Q2(Q2),

.Q3(Q3),

.Q4(Q4),

.Q5(Q5),

.Q6(Q6),

.Q7(Q7),

.Q8(Q8),

// SHIFTOUT1, SHIFTOUT2: 1-bit (each) output: Data width expansion output ports

.SHIFTOUT1(SHIFTOUT1),

.SHIFTOUT2(SHIFTOUT2),

.BITSLIP(BITSLIP), // 1-bit input: The BITSLIP pin performs a Bitslip

// CE1, CE2: 1-bit (each) input: Data register clock enable inputs

.CE1(CE1),

.CE2(CE2),

.CLKDIVP(CLKDIVP), // 1-bit input: TBD

// Clocks: 1-bit (each) input: ISERDESE2 clock input ports

.CLK(CLK), // 1-bit input: High-speed clock

.CLKB(CLKB), // 1-bit input: High-speed secondary clock

.CLKDIV(CLKDIV), // 1-bit input: Divided clock

.OCLK(OCLK), // 1-bit input: High speed output clock used when

// Dynamic Clock Inversions: 1-bit (each) input: Dynamic clock inversion pins to switch clock polarity

.DYNCLKDIVSEL(DYNCLKDIVSEL), // 1-bit input: Dynamic CLKDIV inversion

.DYNCLKSEL(DYNCLKSEL), // 1-bit input: Dynamic CLK/CLKB inversion

// Input Data: 1-bit (each) input: ISERDESE2 data input ports

.D(D), // 1-bit input: Data input

.DDLY(DDLY), // 1-bit input: Serial data from IDELAYE2

.OFB(OFB), // 1-bit input: Data feedback from OSERDESE2

.OCLKB(OCLKB), // 1-bit input: High speed negative edge output clock

.RST(RST), // 1-bit input: Active high asynchronous reset

// SHIFTIN1, SHIFTIN2: 1-bit (each) input: Data width expansion input ports

.SHIFTIN1(SHIFTIN1),

.SHIFTIN2(SHIFTIN2)

);

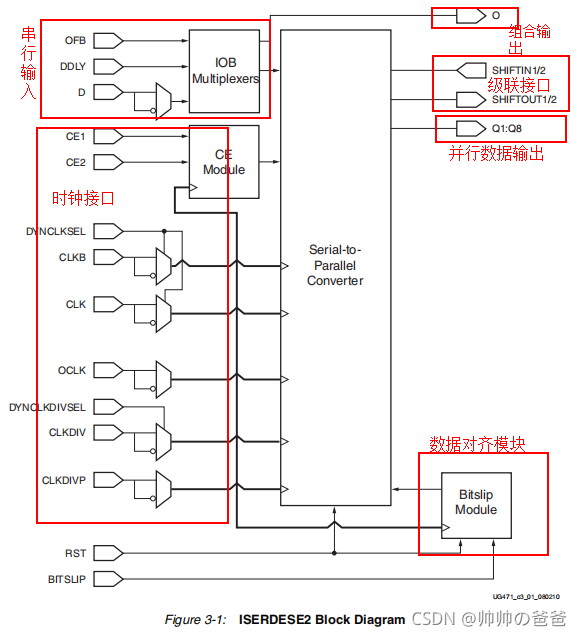

4.ISERDESE2框图

串行输入: 即串行数据输入(D: 与IOB相连, DDLY来源于IDELAYE2原语的输出)

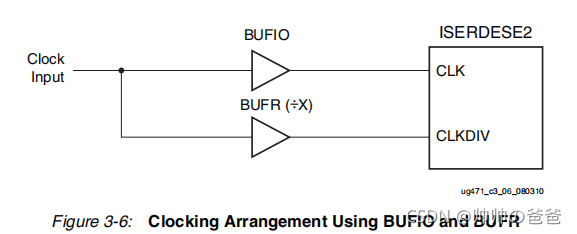

时钟接口:包含高速时钟CLK ,分频时钟CLKDIV等;

数据对齐模块:Bitslip,用于源同步,重新排列输入的并行数据;

组合输出O:O输出不寄存,根据参数配置输出D / DDLY;

级联接口:1个ISERDESE2最大位宽为8位,想要实现10-,14bit的数据,就需要级联两个ISERDESE2;

并行数据输出:Q1-Q8

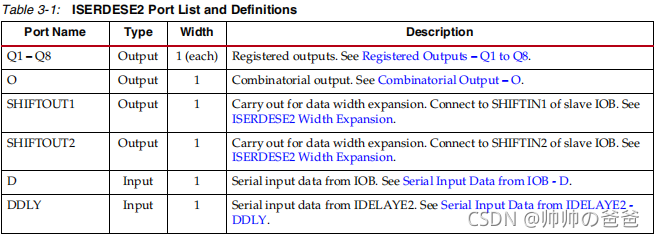

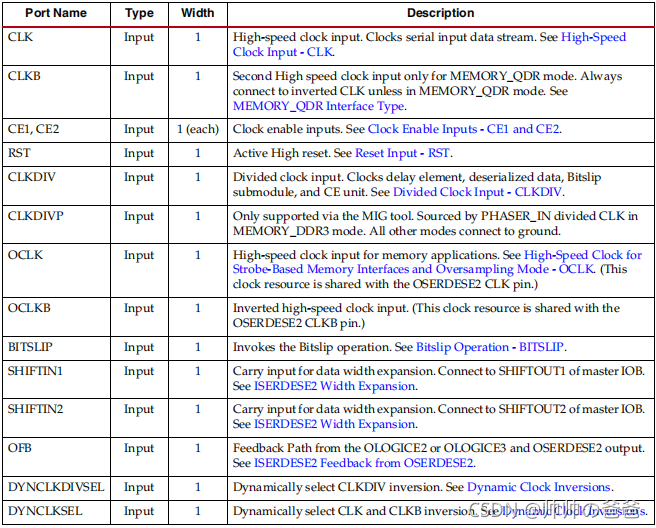

5. ISERDESE2端口信号

有些地方可能翻译的不是很准确,附上手册原文。

5.1时钟接口

提供ISERDESE2工作的高速源同步串行时钟,并行数据获取时钟和控制时钟。

5.2并行数据输出

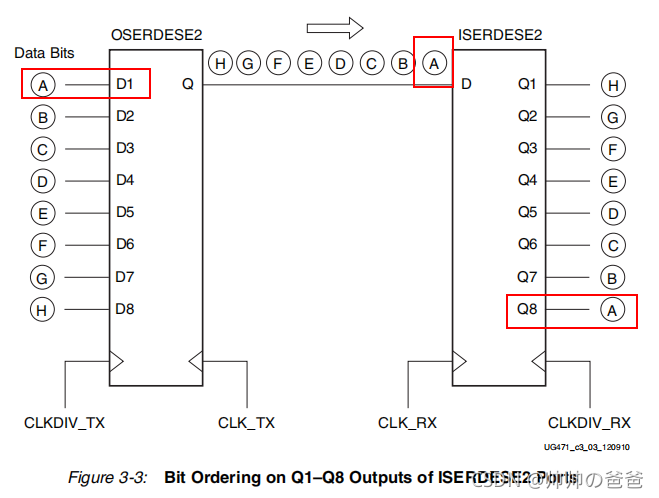

输入输出的顺序相反,具体见下图:

当输入D1为A,输出Q8为A

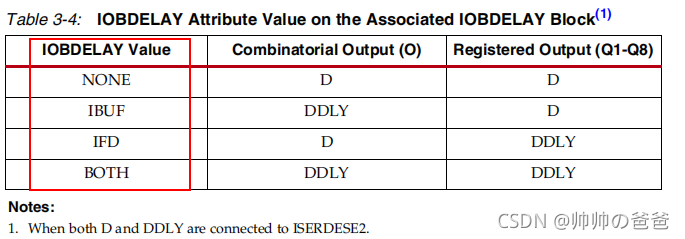

5.3 数据输出选择

根据IOBDELAY参数设置的不同,组合输出O与寄存输出Q1-Q8的输出选择:

D 、 DDLY 的意思前文已讲过,不再重复。

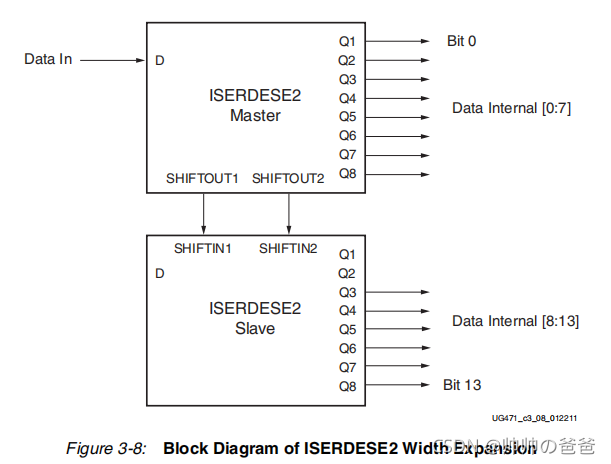

5.4级联接口

该接口用于实现DDR模式下,位宽扩展为10bit,14bit;

通过级联接口与另外一个ISERDESE2相接;

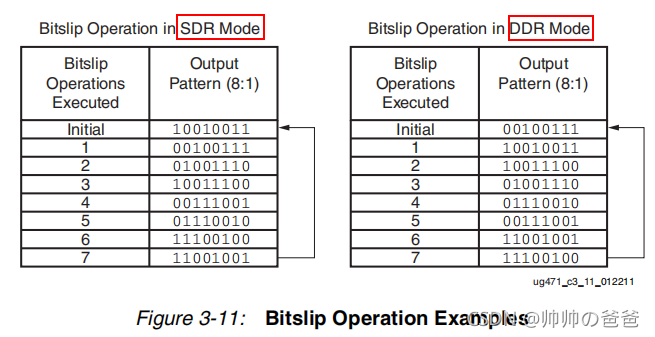

6.数据对齐操作

SDR Mode:

输出每次左移1位;当8次操作后,恢复到最初状态;

DDR Mode:

输出交替进行右移1位和左移3位操作,当8次操作后,恢复到最初状态;

注意:

1. 同步于CLKDIV时钟,本小节所说的时钟周期特指CLKDIV时钟周期

2. 在“NETWORKING”模式下使用

3. 类似于一个桶式移位”Barrel_Shifter”

4. bitslip只能拉高1个clkdiv时钟周期

5. bitslip两次拉高之间必须间隔至少一个时钟周期;

6. 用户逻辑需等待最少2个clkdiv时钟周期(SDR模式)/3个时钟周期(DDR)后,数据移位才能完成。

审核编辑:符乾江

-

PowerPCB 快捷命令中文翻译2008-05-11 Array

-

thyristor 中文翻译是晶闸管2009-05-24 0

-

芯嵌出品----ILI9341中文翻译资料(版本V1.0)2013-09-03 0

-

The LabVIEW Style Book 中文翻译版2016-01-06 0

-

uCOS-III中文翻译2016-07-22 0

-

请问是否必须总是有一个训练模式来使用ISERDESE2?2019-04-04 0

-

无法找到IODRP2_MCB原语的任何文档2019-05-24 0

-

请问ISERDESE2原语支持多少位输入?2020-04-24 0

-

如何正确配置ISERDESE2?2020-07-22 0

-

使用ISERDESE2 INTERFACE_TYPE设置为NETWORKING时收到警告的原因?2020-07-25 0

-

Understanding Delta-Sigma Data Converters, 2nd Edition 中文翻译出版2021-07-30 0

-

《Xilinx—UG471中文翻译》(3)OSERDESE2原语介绍2022-02-16 1462

-

《Xilinx—UG471中文翻译》(1)IDELAYE2原语介绍2022-02-16 2888

-

《Dive Into Python》中文翻译版.pdf2022-02-25 587

全部0条评论

快来发表一下你的评论吧 !