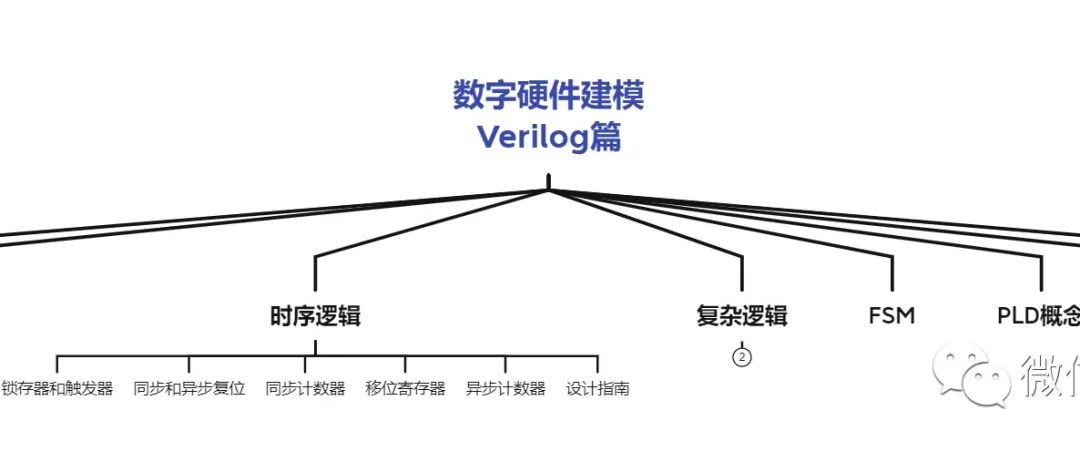

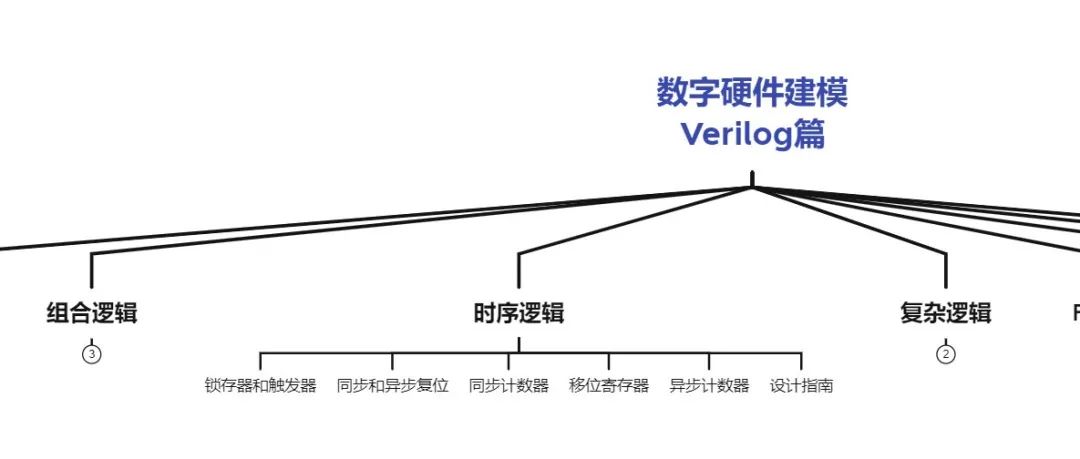

一文详细了解可编程逻辑器件(PLD)

描述

FPGA的发展历史

PLD简介

在过去的十年中,可编程逻辑器件(PLD)市场不断增长,对PLD的需求不断增加。具有可编程特性且可编程的芯片称为PLD。PLD也称为现场可编程器件(FPD)。FPD用于实现数字逻辑,用户可以配置集成电路以实现不同的设计。这种集成电路的编程是通过使用EDA工具进行特殊编程来完成的。

市场上推出的第一个可编程芯片是可编程只读存储器(PROM)。PROM有许多地址线和数据线。地址线用作逻辑电路输入,数据线用作逻辑电路输出,因为PROM的结构效率低下,无法用于实现复杂的数字逻辑。20世纪70年代开发的器件是PLA,它具有两级逻辑,用于实现小密度逻辑。在PLA进化之后,可编程逻辑器件发生了真正的进化。之后,SPLD、CPLD和FPGA在20世纪80年代早期发展起来。早期的可编程逻辑器件如图9.1所示。

表9.2 PLD分类

| 逻辑单元 | PAL或者PLA | SPLD | CLB |

| 密度 | 几百个逻辑门 | 几千个逻辑门 | 少数lac逻辑门 |

| 类型 | 富门逻辑Gate rich logic | 门到达逻辑Gate reach logic | 触发器丰富逻辑Flip-flop rich logic |

| 应用 | 小密度FSM | 中等门计数FSM | 复合FSM |

| PLD | SPLD | CPLD | FPGA |

|---|

PLD分类如表9.2所示。

以下是用于理解现场可编程设备的关键术语。

PAL是一种密度相对较小的现场可编程器件(FPD),它具有可编程和平面,然后是固定或平面,称为可编程阵列逻辑(PAL)。可编程逻辑阵列(PLA)是一种密度相对较小的现场可编程器件(FPD),它具有可编程和平面,然后是可编程或平面。PLA结构有两级逻辑,可在全定制芯片上使用。

任何类似PAL或PLA的结构称为简单可编程逻辑器件(SPLD)。SPLD由于具有良好的时序性能,被用于实现小型门计数状态机。

复杂可编程逻辑器件(CPLD)是指在同一芯片上由多个类似于SPLD的模块组成的具有互连逻辑的结构,称为复杂可编程逻辑器件(CPLD)。CPLD也称为mega-PAL、Super-PLA或增强型PLD(EPLD)。在实际场景中,CPLD用于实现中等密度状态机,因为与SPLD相比,CPLD具有更好的定时性能。CPLD结构如图9.2所示。

图9.2复杂可编程逻辑器件系统框图

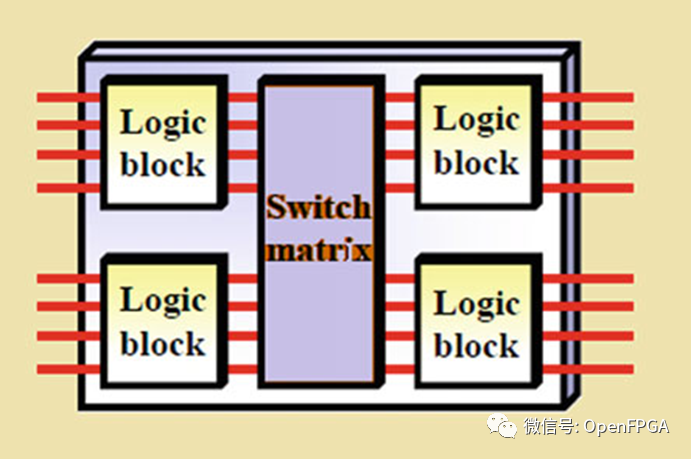

图9.3基本FPGA架构

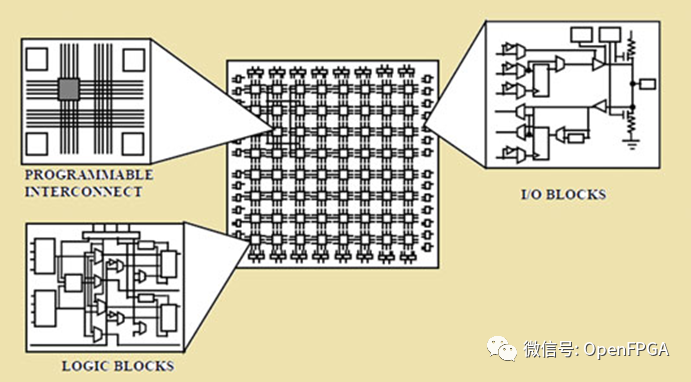

现场可编程门阵列(FPGA)是由触发器和逻辑块等更多资源组成的可编程逻辑,用于实现高密度逻辑,被称为现场可编程门阵列(FPGA)。FPGA也称为可编程ASIC,由可配置逻辑块(CLB)、IO块(IOB)和可编程互连组成。现代FPGA甚至包括乘法器、RAM、DSP和处理器核心。带有关键块、逻辑块、IO块和可编程互连的FPGA如图9.3所示。

互连现场可编程设备中的布线资源称为互连。

可编程开关用于将一条互连线连接到另一条互连线或将逻辑块连接到互连线的开关称为可编程开关。

可配置逻辑块(CLB)可配置用于所需组合和顺序逻辑功能的逻辑块称为CLB。在FPGA上实现逻辑时,逻辑被分解为小密度逻辑块并映射到多个CLB上。

逻辑密度FPGA中每单位面积的逻辑量称为逻辑密度。

逻辑容量映射到单场可编程器件的逻辑量称为逻辑容量。逻辑容量以门阵列中逻辑门的数量的形式给出。逻辑容量可以认为是两个输入与非门或通用门的数量。

现场可编程设备的最大工作频率是时序逻辑性能的度量。对于组合逻辑,设计中的最长路径决定了性能。

结构化ASIC和FPGA设计的比较如表9.3所示。

表9.3结构化ASIC与FPGA的比较

| 原型样本的时间 | 4–8周 | 0周 |

| 批量生产总时间 | 12–15周 | 8周 |

| 供应商NRE/屏蔽成本 | 10万至20万美元 | 75000美元 |

| 转换的设计成本 | 25万至30万美元 | $0 |

| 转换工具的额外成本 | 10万至20万美元 | $0 |

| 单位成本 | 低的 | 低的 |

| 危险性 | 高的 | 低的 |

| 在系统中进行更改的灵活性 | 不灵活 | 灵活的 |

| 从原型到生产的设计转换 | 附加工程 | 免转换 |

| 选择标准 | 结构化ASIC* | FPGA |

|---|

FPGA分类

现代FPGA被称为可编程ASIC,用于各种应用,包括ASIC SOC设计和原型设计。FPGA编程包括以下类型,本节将对此进行讨论。任何FPGA的主要编程类型有

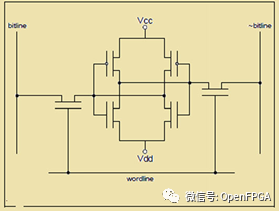

基于SRAM的FPGA

市场上的大多数FPGA都基于SRAM技术。它们将配置位文件存储在使用锁存器设计的SRAM单元中。由于SRAM是易失性的,因此需要在启动时对其进行配置。有两种编程模式:主模式和从模式。SRAM存储单元如图9.4所示。

图9.4 SRAM单元

在主模式下,FPGA从外部源读取可配置数据。

在从模式下,FPGA通过使用外部主设备(如处理器)进行配置。外部配置接口可以是JTAG(边界扫描)。

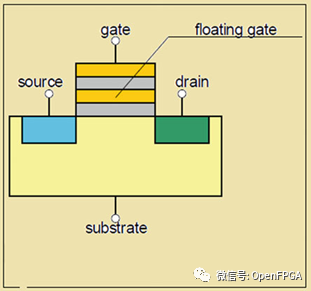

基于FLASH的FPGA

在这种类型的FPGA中,FLASH用于存储配置数据。因此,该FPGA的主要资源是FLASH。因此,这类FPGA的功耗较低,并且对辐射影响的耐受性较差。在基于SRAM的FPGA中,内部FLASH仅在通电期间用于加载配置文件。FLASH中使用的浮栅晶体管如图9.5所示。

图9.5 FLASH中的浮栅晶体管

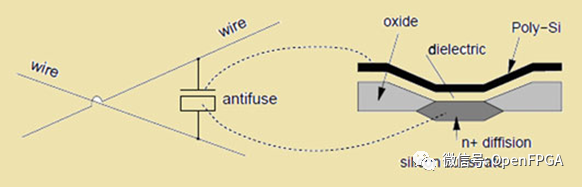

反熔丝FPGA

这些类型的FPGA仅用于编程一次,与前两种类型的FPGA相比,它们有所不同。反熔丝与保险丝相反,最初它们不导电,但可以燃烧以导电。

图9.6反熔丝结构

一旦对其进行编程,就无法重新编程,因为燃烧的熔丝无法强制进入初始状态。如图9.6所示。

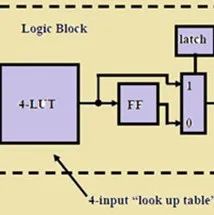

FPGA构建块

以下是FPGA体系结构中的关键结构,本节对此进行了描述。FPGA架构如图9.7所示。

可配置逻辑块(CLB),CLB由查找表(LUT)、多路复用器和寄存器组成。基于RAM的LUT用于实现数字逻辑。CLB可编程实现多种逻辑功能。甚至CLB也用于存储数据。

输入-输出块(IOB)该块用于控制设备内部逻辑和IO引脚之间的数据流。每个IO用于支持三态控制的双向数据流。几乎有24种不同的IO标准,其中包括七种不同的特殊IO高性能标准。双数据速率寄存器还具有数字控制阻抗功能。

块RAM(BRAM)用于存储大量数据,以双端口RAM的形式提供。例如,18 Kbit双端口块RAM。BRAM可以由多个块组成,具体取决于设备。

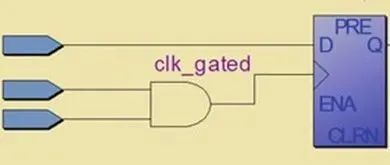

数字时钟管理器(DCM)它们用于时钟管理,并提供完全校准的数字时钟解决方案。它们用于均匀的时钟分布、时钟信号的延迟、对具有均匀时钟偏移的时钟信号进行乘法或除法。

乘法器专用乘法器块用于执行两个“n”位数字的乘法。根据设备的不同,“n”可能会有所不同。如果n=18,则专用块用于执行两个18位数字的乘法。

DSP模块它们是用于实现滤波、数据处理等DSP功能的嵌入式DSP模块。这些模块用于提高FPGA的整体性能,同时为DSP应用程序处理大量数据。

图9.7 FPGA架构(源Xilinx)

FPGA设计流程

FPGA中仿真概念

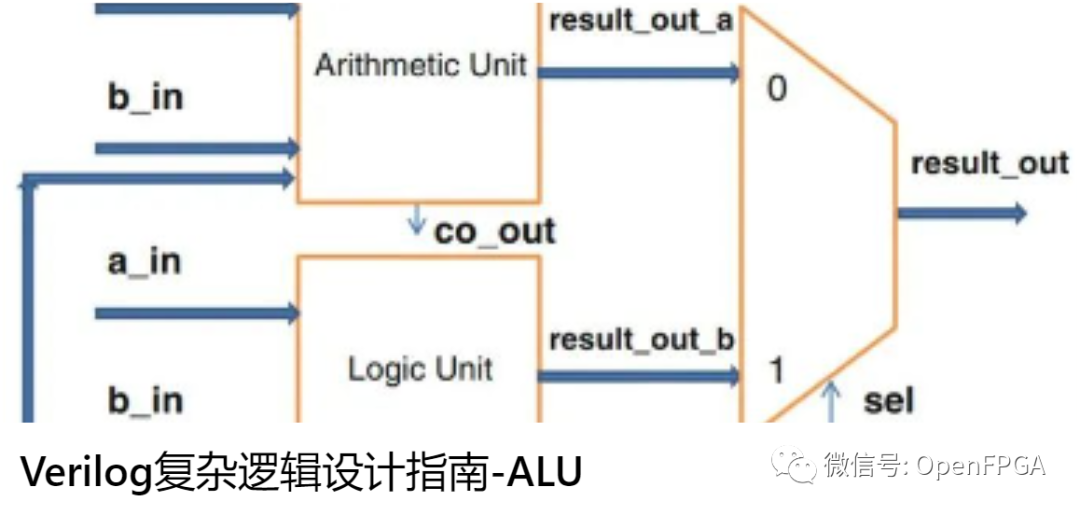

Verilog复杂逻辑设计指南-奇偶校验生成器和校验器及筒式移位器

Verilog时序电路设计指南

Verilog时序逻辑硬件建模设计(五)异步计数器&总结

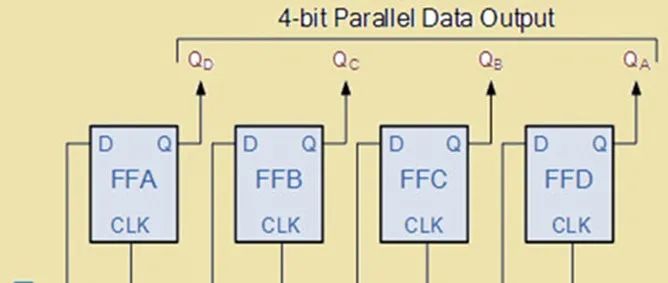

Verilog时序逻辑硬件建模设计(四)移位寄存器

Verilog时序逻辑硬件建模设计(三)同步计数器

Verilog时序逻辑硬件建模设计(二)同步和异步复位

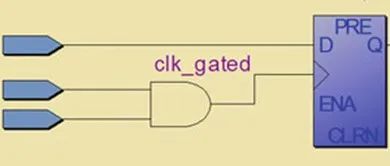

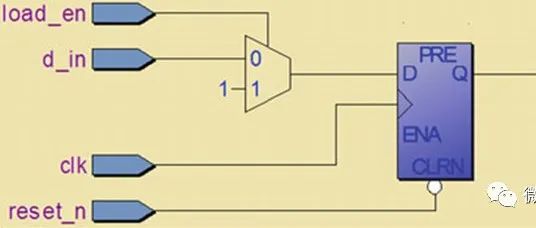

Verilog时序逻辑硬件建模设计(一)锁存器D-latch和触发器Flip-Flop

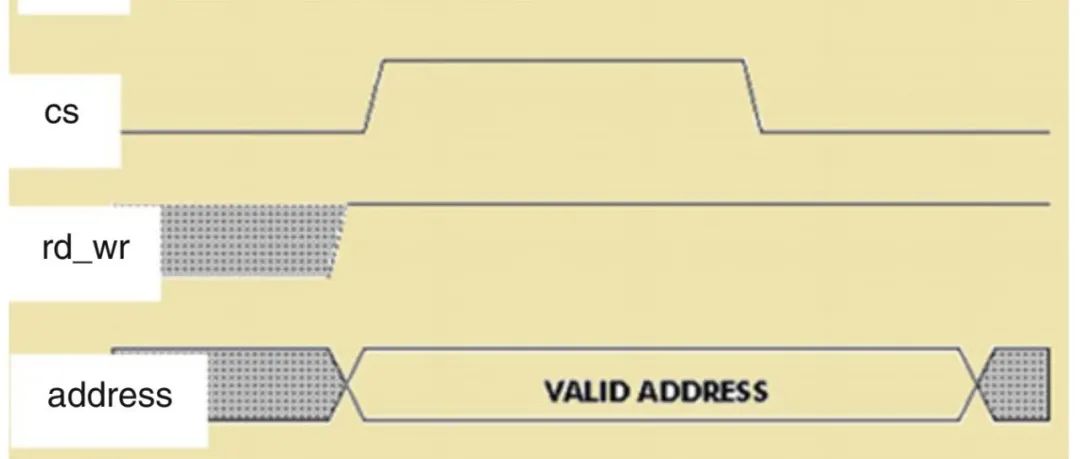

Verilog组合逻辑设计指南

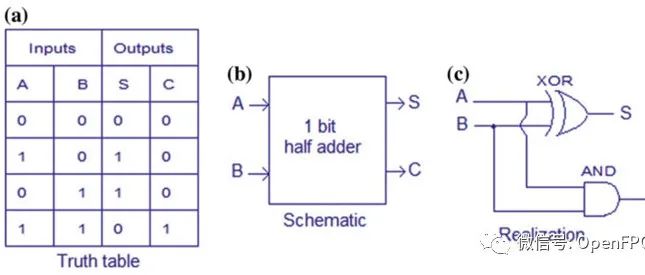

组合逻辑硬件建模设计(二)算术电路

Verilog 里面,always,assign和always@(*)区别

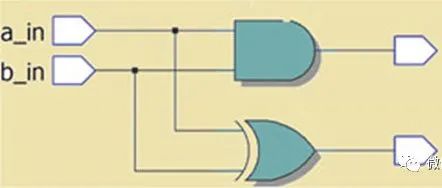

组合逻辑硬件建模设计(一)逻辑门

数字硬件建模-重新从另一方面理解Verilog(二)

数字硬件建模-从另一方面理解Verilog(一)

数字硬件建模综述

原文标题:FPGA的发展历史

文章出处:【微信公众号:OpenFPGA】欢迎添加关注!文章转载请注明出处。

审核编辑:汤梓红

-

什么是可编程逻辑2009-05-29 0

-

PLD/可编程逻辑器件的入门知识2009-06-20 0

-

可编程逻辑器件2014-04-15 0

-

分享一款不错的基于可编程逻辑器件PLD的数字电路设计方案2021-04-30 0

-

PLD可编程逻辑器件2021-07-22 0

-

可编程逻辑器件在积分式A/D转换器中的应用2009-08-29 836

-

第三十二讲 可编程逻辑器件及应用2009-03-30 1350

-

什么是PLD(可编程逻辑器件)2009-06-20 16069

-

基于可编程逻辑器件的数字电路设计2009-11-16 1487

-

可编程逻辑器件技术_pld技术2012-06-16 1166

-

可编程逻辑器件的分类有哪些2020-06-10 27138

-

PLD可编程逻辑器件的原理详细讲解2021-01-21 1243

-

可编程逻辑器件PLD课件下载2021-08-13 912

-

可编程逻辑器件测试方法2023-06-06 757

-

可编程逻辑器件测试2023-06-06 441

全部0条评论

快来发表一下你的评论吧 !