为什么PCIe Gen3/Gen4不使用CXL

描述

本文由甄建勇翻译。甄建勇,高级架构师(某国际大厂),十年以上半导体从业经验。主要研究领域:CPU/GPU/NPU架构与微架构设计。感兴趣领域:经济学、心理学、哲学。

2022 年服务器行业的最大亮点之一将是 Compute Express Link ( CXL)。我们在 2019 年首次宣布 CXL时就有媒体开始报道它。该项目已经从英特尔内部项目发展成了一个广泛的行业联盟,并且是我们进入 2022 PCIe Gen5 时代时行业的发展方向。尽管如此,仍有许多人不太了解 CXL,因此我们将尝试先使用一个简单的视频来解释 CXL:酸橙(Limes)。

视频版由于我们将在未来几年内讨论 CXL,因此我们提供了此作品的视频版本,您可以在此处找到。

什么是CXL?

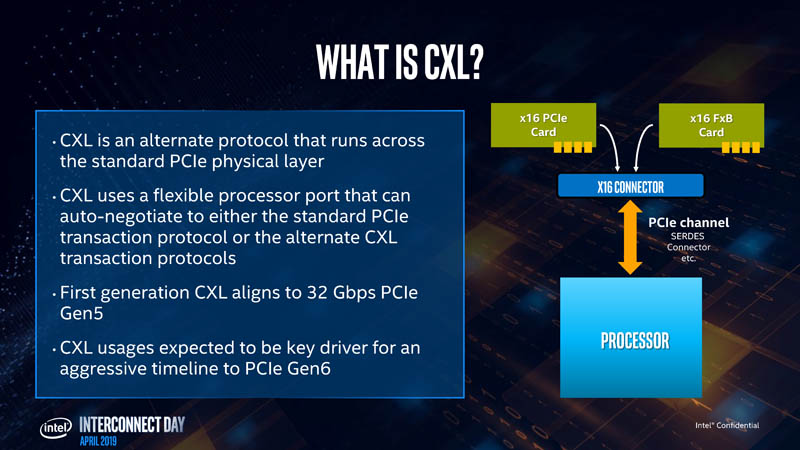

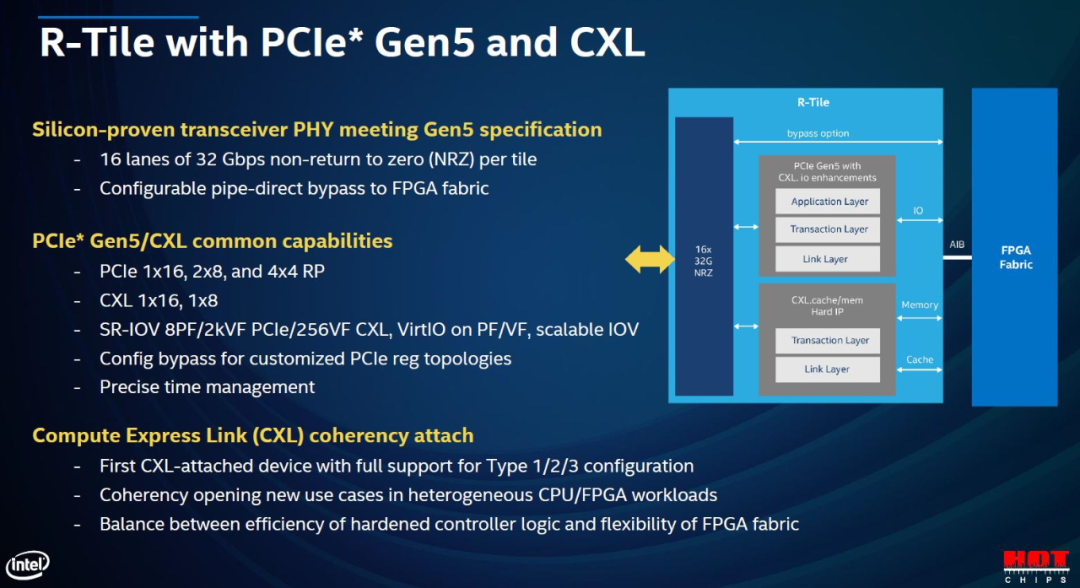

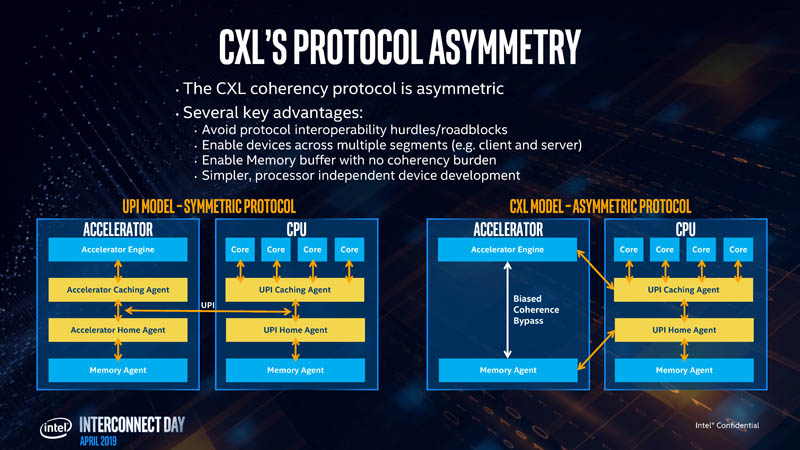

Compute Express Link 是一种缓存一致性互联,旨在帮助系统(尤其是具有加速器的系统)更高效地运行。CXL位于 PCIe Gen5链路基础架构之上。可以有 PCIe Gen5 设备,但许多PCIe Gen5(或 PCIe 5.0)设备也支持在PCIe或 CXL两种模式下运行。类似于 AMD EPYC(霄龙)CPU可以将其 I/O通道作为 PCIe或 Infinity Fabric 运行。这不是特定于某个供应商的实现,而是一个广泛的行业标准。CXL的主要优势是它允许不同终端上的内存直接支持Load/Store,这就是我们接下来要介绍的内容。

我们将在这里重点关注内存。内存是实现这一目标的关键驱动因素,因为超大规模生产商意识到,几乎每个设备都有板载内存,而内存成本很高,但利用率经常很低。在更高的层次上,CXL 是系统在多个设备之间有效共享和利用内存的工具。我们今天讨论的主要是服务器,但CXL也可以应用于服务器之外的领域。

为什么PCIe Gen3/Gen4 不使用CXL?

首先是时间。 CXL 从推出到 2019 年采用, 2021 年末和 2022 年初确实是我们希望看到的支持CXL的第一代芯片。不过,另外一个关键的因素是 PCIe Gen5 的迅速普及。整个行业从PCIe Gen3过渡到 Gen4花了大约七年的时间。PCIe Gen5 普及发生在Gen4 之后大约 3 年。Gen5把 PCIe Gen4带宽翻倍了。由于 CXL位于 PCIe Gen5 之上,所以我们通常会看到 32GT/s x16的控制器,但CXL 也可以支持x8 和 x4。在所谓的“降级”模式下,有一些模式可以进入 x2和 x1。重要的是,PCIe Gen5 x4 链路有足够的带宽来处理 100GbE 链路,因此可见低配下仍然有很大的带宽,类似于英特尔在2021 年第一季度用PCIe Gen3 x16作为高端互联的解决方案。

还有,额外的带宽意味着PCIe将有足够的能力来处理一类新的应用,特别是那些涉及远程内存加载/存储的场景,而前几代PCIe的处理速度不够快。

所以,总结来看,为什么CXL没有早点出来的原因有三。

首先,我们需要 配合PCIe Gen5 的发展时间。

其次,我们需要创建 CXL。

第三,行业采用需要时间。

现在万事俱备,CXL 就是未来。

Compute Express Link 协议三部曲

CXL 使用三个主要协议:

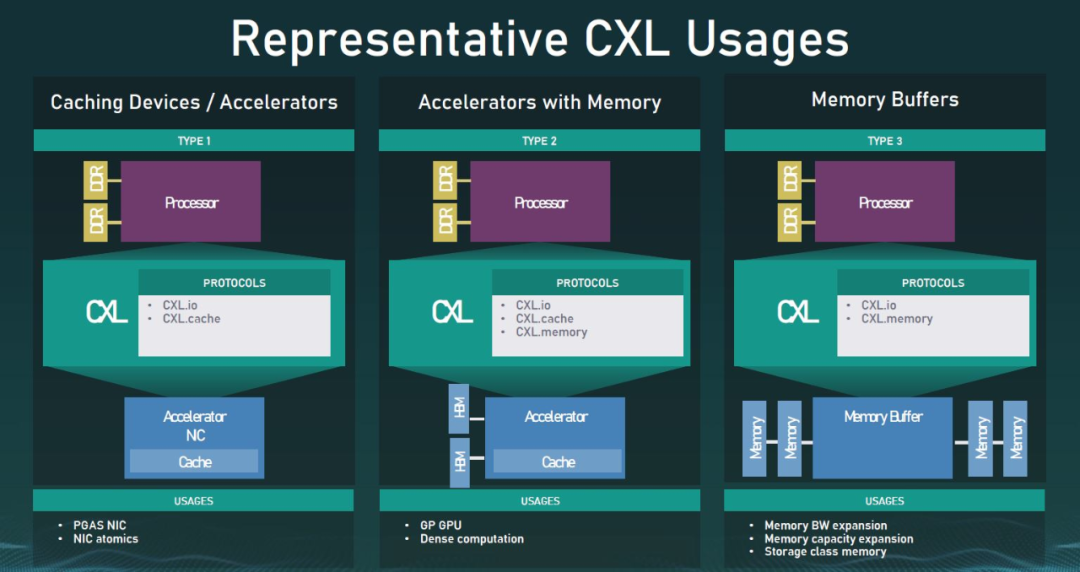

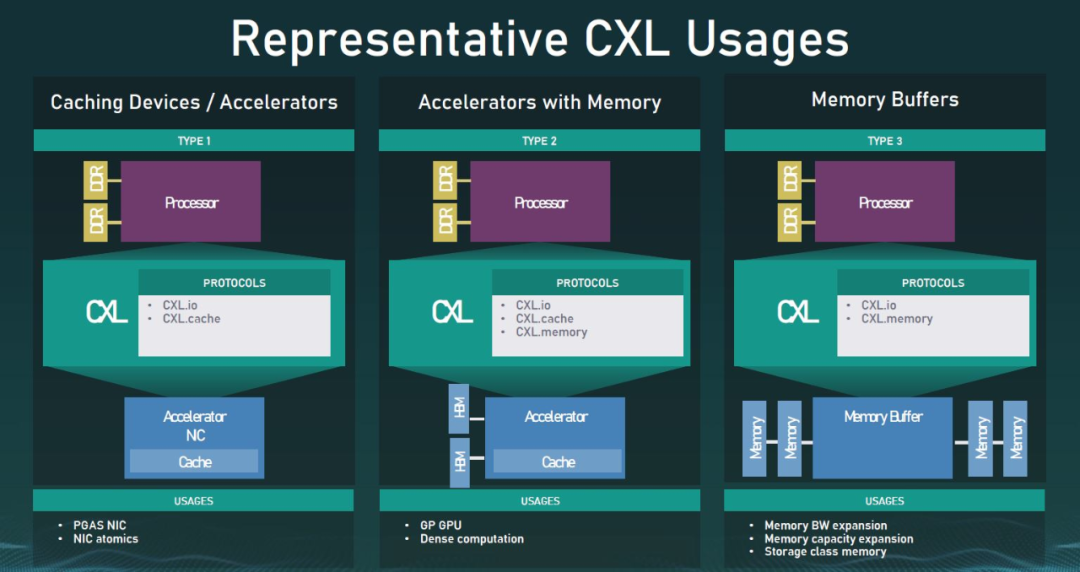

CXL.io 是用于初始化、链接、侦测设备和枚举以及注册访问的协议。它为I/O 设备提供了一个非连贯的加载/存储接口,类似于 PCIe Gen5。CXL 设备也必须支持 CXL.io。

CXL.cache 是定义主机(通常是 CPU)和设备(例如CXL内存模块或加速器)之间交互的协议。这允许 CXL 设备以低延迟访问缓存在主机内存的数据。可以将其理解为为 GPU直接缓存数据在 CPU的内存中。

CXL.memory / CXL.mem 是为主机处理器(通常是 CPU)提供使用加载/存储命令直接访问设备内存的协议。将其理解 CPU可以直接使用 GPU或加速器上的内存。

CXL.io 是 CXL中必需的,可以和 CXL.cache或CXL.mem 任意组合。比如 Type 1 (CXL.io + CXL.cache)、Type 2(所有三个)和 Type 3 (CXL.io + CXL.mem)。

CXL 1.0 和 1.1 用法

Type 1 可以将其视为直接访问主机CPU内存的加速器,比如NIC。Type 2 是我们有一个加速器的情况,比如有内存的 GPU,GPU 可以访问主机内存,而主机 CPU 可以访问 GPU 内存。可以将类型 3 视为一种内存模块,其主要目的是将 CXL 内存设备的内容暴露给主机 CPU。 CXL 1.1 与 2.0

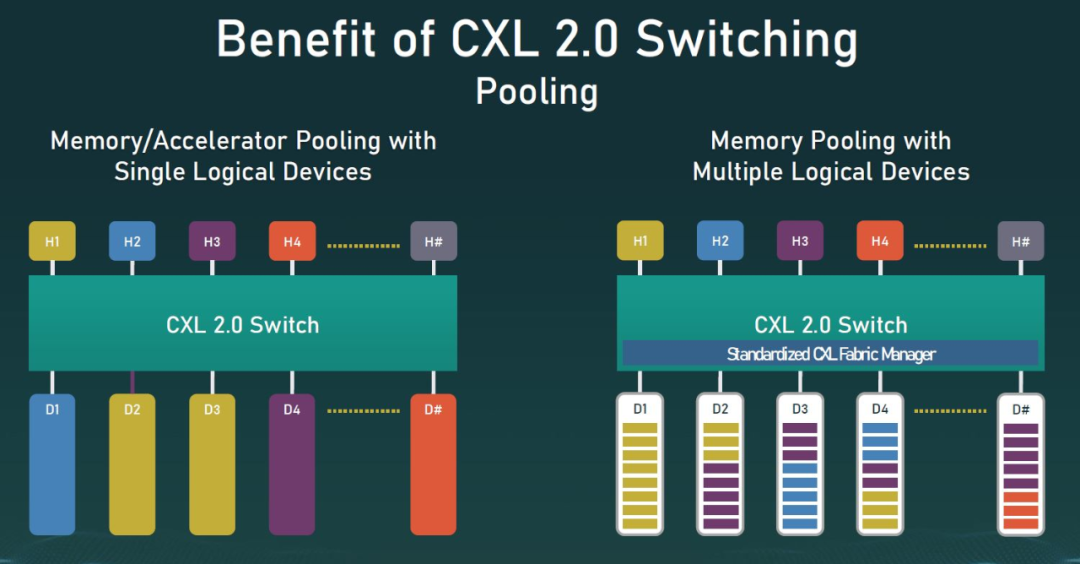

我们将在2022 年初看到大多数的设备将使用CXL 1.1。这些仍然主要是主机 CPU管理的, CXL只用于现有的系统中。CXL 2.0 是真正有意思的东西。使用 CXL2.0,我们可以进行 CXL 切换。CXL的 交换和池等机制,允许将多个主机和多个设备连接到一个交换机,然后设备既可以作为完整设备,又可以作为逻辑设备分配给不同的主机。从CXL 2.0开始我们将看到游戏规则的改变。

CXL 2.0交换池

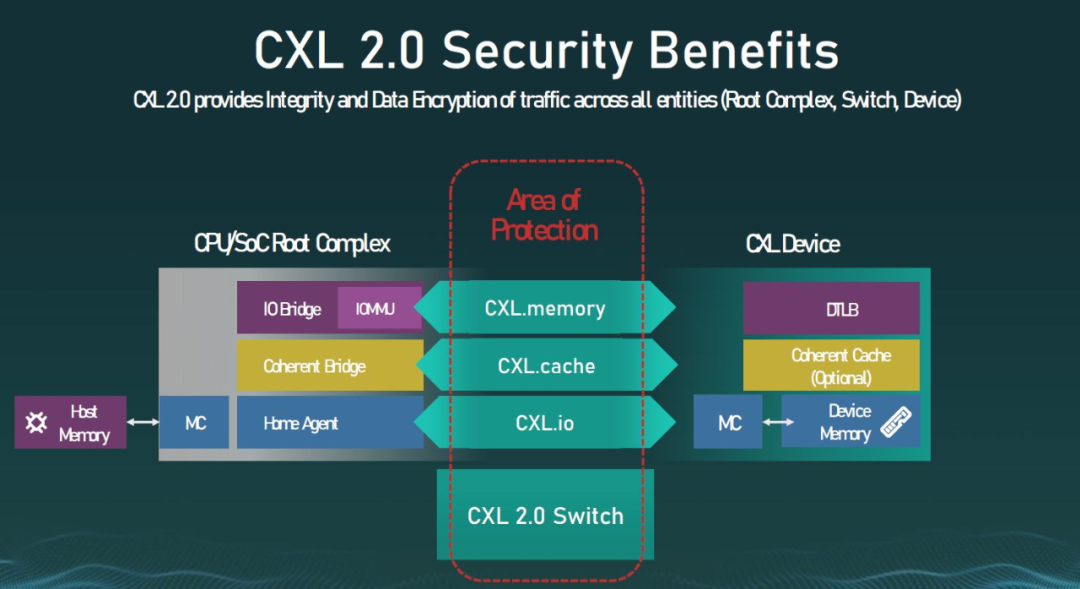

除了 CXL 2.0 交换和池化机制之外,我们还为协议添加了额外的安全层。

CXL 2.0安全性虽然 CXL 1.0/ 1.1 将是启动该计划的重要版本,但 CXL 2.0 是我们真正想要的。这主要是因为我们开始改变服务器架构和部署的方式。CXL 1.1 是必要的,并且有一些应用场景,尤其是加速器和 GPU。不过,CXL 2.0 ,我们希望拥有足够成熟的软件以永远改变服务器的设计方式。 接下来,我们将讨论一些示例,并使用我们的Tacos和Limes来帮助那些在幻灯片上难以想象出 CXL 用处的人。 三个 Compute Express Link (CXL) 示例……使用Tacos和Limes那么让我们来看看Tacos和Limes用例,以及为什么这些用例很重要。这层次太高,也并不完美,但希望这有助于人们对一些高级概念有形象化的理解。

CXL 1.0 和 1.1 用法在我们的示例中,Limes将代表Memory。主机部分将由Rubio的Blackened Mahi Mahi Tacos代表,加速器将由beverage(饮料)代表。

CXL Taco 和 Lime 示例:两个 Tacos盘的石灰苏打水

在我们的第一个示例中,也许我们在两个 Rubio 熏黑的Mahi Mahi Tacos上收到了一个Limes。

CXL Taco 和 Lime 示例:两个 Tacos 一个 Lime 一个 Soda

这并不少见。大多数体验过卢比奥炸玉米饼的人都经历过一次“不足”的事件。事实上,即使是贴在商店橱窗上的广告也表明,一个酸橙配三个炸玉米饼可能会发生这种情况。

Rubios 商店橱窗广告 3 Tacos 1 Lime

这显示了配置内存(石灰)的资源效率低下。我们的第一个示例虽然讨论了一个可能的操作。也许今天不是酸橙炸玉米饼日,而是酸橙饮料日。在这里,我们可以从主机处理器(玉米饼)访问酸橙汁(内存)并将其用于我们的饮料。这就是 CXL.cache 和 Type 1 设备示例背后的想法。

通过 CXL.cache Beverage 访问 CXL Lime

在我们的第二个示例中,我们的处理器(炸玉米饼)来自 Rubios,两个炸玉米饼只有一个酸橙。这是主机处理器内存不足的示例。我们可以利用中心的酸橙盘中的酸橙汁(CXL内存扩展模块)。这是 CXL.mem和 Type 3 设备的一个示例。

CXL Taco 和石灰示例板的石灰

理论上,尤其是当我们有交换和池化的 CXL 2.0 后,我们访问的内存不必是 DDR5。我们可以(理论上)使用英特尔傲腾、GDDR6X 或其他技术等SCM的 CXL设备。不同配置成本不同,应用也不同,但这就是CXL如此重要的原因。

CXL 玉米卷和酸橙玉米卷与柑橘品种 2

在这个用例中,我们可以拥有多种类型的内存,将它们附加到单个系统,然后访问整个内存设备,或者将设备的一部分用于不同的目的。CXL 2.0 具有热插拔功能。我们已经知道用于此用例的设备已经出现,所以我们认为热拔插将非常重要。它还允许比传统DIMM 外形尺寸更大容量更大的系统内存。 在我们的第三个示例中,让我们更疯狂一点,假设我们想在炸玉米饼(处理器)上使用我们饮料中的酸橙(加速器,如 GPU),并在我们的饮料中使用炸玉米饼中的一些酸橙汁。这是 Type-2 设备的示例。

CXL Taco 和Lime 示例 许多炸玉米饼 许多苏打水 柑橘品种

同样,事情开始变得真正有趣的地方是,比如说,我们想要 3D XPoint/英特尔傲腾持久内存或存储类内存 (SCM),而不是我们的标准 DDR5 内存。我们可以将 SCM媒体(柠檬)打包到看起来像我们用于酸橙的东西,现在可以使用柠檬而不是酸橙或柠檬和酸橙的混合物的 Type-3 设备。在 CXL 2.0世界中,GPU和 CPU不再需要各自的 SCM,而是都可以访问 SCM 甚至是其它连接的大型内存池。 虽然这不是一个完美的例子,但希望上面的照片有助于说明CXL的发展方向。就像在虚拟化中一样,GPU 访问主机系统或 Type-3连接设备内存的能力,意味着我们可以更有效地利用资源和系统设计。我们不需要具有与主机 CPU 分开的 Optane 内存的 GPU/AI 加速器。那将是成本高昂且不灵活的。CXL 为系统增加了这种灵活性。CXL 有助于控制成本,同时还增加了架构的灵活性,这类似于几年前虚拟化带来的好处。 加强版示例 供应很重要,有效的资源利用也很重要,但让我们更进一步,想象一下这将如何改变架构。尽管它们在当今的大规模部署中不太常见,但许多企业仍在使用硬件 RAID 控制器。

Broadcom 9500 RAID 控制器

这些通常使用一些关键组件和功能进行操作: · 有一个 SoC 控制数据移动、奇偶校验计算、缓存和存储/检索。· 板载 DRAM 用作写入缓存,通常用作小型读取缓存。· 电池/电容器 FRU 允许写入缓存发生在板载 DRAM中,即使断电也能安全刷新。· 用于板载 DRAM 的闪存存储,以在断电时刷新。· 用于管理磁盘的存储控制器。· SSD 用于主存储或作为连接到 RAID控制器的缓存设备进行管理。· 通常,这些 SSD 在每个设备上都有自己的断电保护写入缓存。现在,想象一下未来会怎样。DRAM-less NAND SSD 和硬盘驱动器在更高级别进行管理。这可以为每个 SSD移除几 GB的 NAND。我们可以使用基于 CXL的 SCM(例如 Optane Persistent Memory)并直接写入该设备,而不是 NAND SSD和 RAID控制器上的断电保护以及闪存写入断电刷新事件数据作为系统的写缓存。然后,诸如 DPU 之类的协处理器可以管理将缓存从 SCM 写入本地或网络存储的刷新。RAID 卡上的缓存不是几 GB 可能是 1TB 的主机内存(尽管这基本上不需要,因为我们有 CXL)或CXL DDR5,可以由主机处理器直接访问,而不是通过 RAID控制器。 这种应用场景给我们的启发是,如何用服务器中更高性能的本地资源替换传统存储阵列并使用横向扩展存储?这对行业来说绝对是变革性的,这只是我们听到的几家公司正在努力的一个例子。通常,这些应用场景包含更大、更多样化的内存池和 GPU/AI 等加速器,所以我给了一些不同的示例来说明为什么CXL 可以轻松应付这些个不同的场景。

最后的话

CXL 的关键在于,随着 CXL的普遍采用,服务器架构的严格限制将开始消失。这非常重要,因为随着服务器不断扩大,这意味着资源得到了更有效的利用。几年后,我们回顾今天的服务器,就会认为它们是一种传统的运营模式,就像我们为虚拟化之后的许多应用程序(以及后来的容器)所做的专用服务器一样。多年以来,这些东西已经被讨论过很多次,但我们实际上是在Astera Labs Aries CXL Retimers之外的产品中实施不到一年。

CXL Taco 和Lime示例 许多炸玉米饼 许多苏打水 柑橘品种

希望本指南可以帮助您了解 CXL 是什么以及它通常要完成的工作。CXL在技术深度方面还有很多,但我们想确保我们的读者先有一个基本的理解。Tacos和 Lime并不完美,但多年来我们一直在研究相同的图表,但仍有人不知道 CXL 的影响。我们谈论的是PCIe Gen5时代早期的CXL,但我们也有有一个到PCIe Gen6 及以后的路线图。我们已经讨论了一些关于此模型如何扩展到诸如 Gen-Z 之类的结构,以使用某种类似的解决方案实现更大规模部署。 当然,我们将来会有更多关于 CXL 的内容,但我们想先给大家说一下CXL 是啥以及其他一些关于CXL的初级内容。

原文标题:CXL:为缓存一致性而生的新一代总线

文章出处:【微信公众号:Linux阅码场】欢迎添加关注!文章转载请注明出处。

审核编辑:汤梓红

-

为什么在我的PCIe Gen3插槽上使用VC709不起作用?2019-09-09 0

-

用于 PCIe Gen-3 卡的高速前端参考设计2015-05-08 0

-

基于FPGA的高速以太网适配器卡必备的PCIe Gen3技术2017-02-10 0

-

可提高信号完整性和系统稳健性PCIe Gen-3高速前端卡设计包括BOM,PCB文件及光绘文件2018-08-14 0

-

用于BBB的4D系统Gen4 LCD触摸屏如何校准2018-10-22 0

-

PCIe GEN3 ECRC仅在离线模式下出错2018-11-05 0

-

请问XC7K325T-2FFG900支持PCIE PHY GEN3吗?2020-07-25 0

-

符合PCIe Gen1,Gen2和Gen3标准的9端口PCIe时钟发生器2020-08-27 0

-

PCIe Gen-3高速前端卡参考设计2022-09-21 0

-

Layerscape MPU中是否有支持PCIe GEN3 16通道的EVB?2023-05-30 0

-

UltraScale FPGA器件中PCIe Gen3模块的性能演示2018-11-28 3513

-

一文解析BMW的Gen3 到 Gen4 的主要更改2021-05-11 8631

-

克服向PCIe Gen3迁移的SoC设计挑战2022-06-14 1667

-

天玑9400性能将超越骁龙8 Gen4?2023-12-18 893

-

骁龙8s Gen3、骁龙7+ Gen3或发布,小米Civi 4或首发2024-03-13 212

全部0条评论

快来发表一下你的评论吧 !