Zynq SoC 设备上的多种用途

描述

ZYNQ从放弃到入门(一)MIO

这篇博文特别关注 Zynq SoC 的多用途 IO (MIO, Multipurpose IO) 模块。正是这个接口块为 Zynq SoC 的双核 ARM Cortex-A9 MPCore 处理器提供了许多标准接口。MIO 还包含确定 Zynq SoC 如何启动的配置设置。MIO 连接到 Zynq SoC 的 PS(处理器系统)端。它连接到 Zynq 设备上的 54 个引脚(注意 CLG225 封装中的 Zynq-7010 SoC 有 32 个 MIO 引脚),用于以下用途:

定义配置方法

四路 SPI 存储器接口

SRAM/NOR闪存接口

NAND闪存接口

两个 10/100/1000 以太网 MAC

两个 USB 2.0 OTG 接口

两个 SD 卡接口

两个 UART

两个主从 I2C 接口

两个全双工 SPI 接口

两个 CAN 2.0B 接口

PJTAG 和 TRACE 调试接口

三重定时器/计数器 (TTC)

系统看门狗定时器

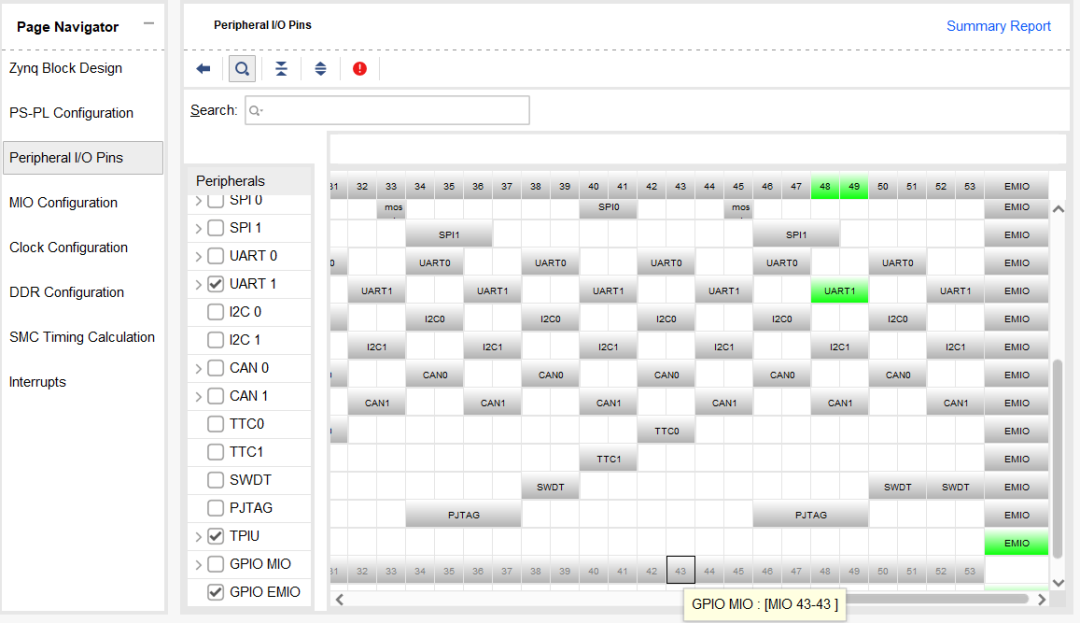

当然,有时会遇到需要用可用引脚数来权衡许多接口的情况。毕竟,工程学总是一门妥协的艺术。使用 Vivado 设计流程,可以通过双击框图中的处理器来分配 MIO 中的功能,这会打开重新定制 IP 窗口。定义 MIO 有两个选项。第一个选项——Peripheral I/O Pins——非常图形化,让您可以看到分配一个接口标准如何影响其他标准,如下图所示:还可以使用此窗口为每个接口定义组电压设置两个 I/O bank(绿色 = 激活)。

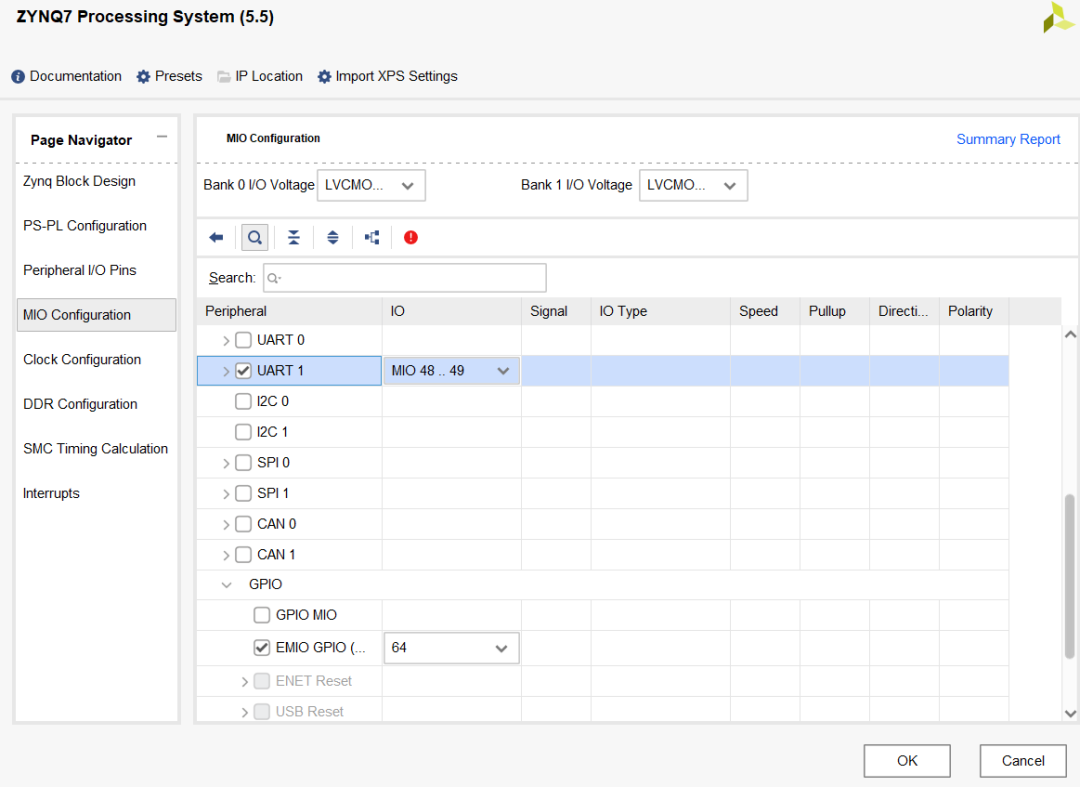

第二个选项是 Zynq 处理系统屏幕中的“MIO 配置”选项卡,如下所示,它会显示分配给 MIO 的接口列表。我们还可以在此视图中分配 EMIO 引脚,稍后我们将解决这个问题。MIO 分为两个电压组:

MIO0 引脚 0 到 15

MIO1 引脚 16 至 53

Bank 0 包括配置输入引脚,在上电后对其进行采样。这些模式引脚共享器件 PS 侧的多用途 I/O 引脚。总共有七个模式引脚映射到 MIO[8:2]。前四个模式引脚定义启动模式;第五个判断是否使用PLL;第六和第七个模式引脚定义了上电期间 MIO bank 0 和 bank 1 上的 bank 电压。在引导加载程序完成后,可以将 MIO bank 0 和 1 上定义的电压标准从 LVCMOS 更改为 HTSL。

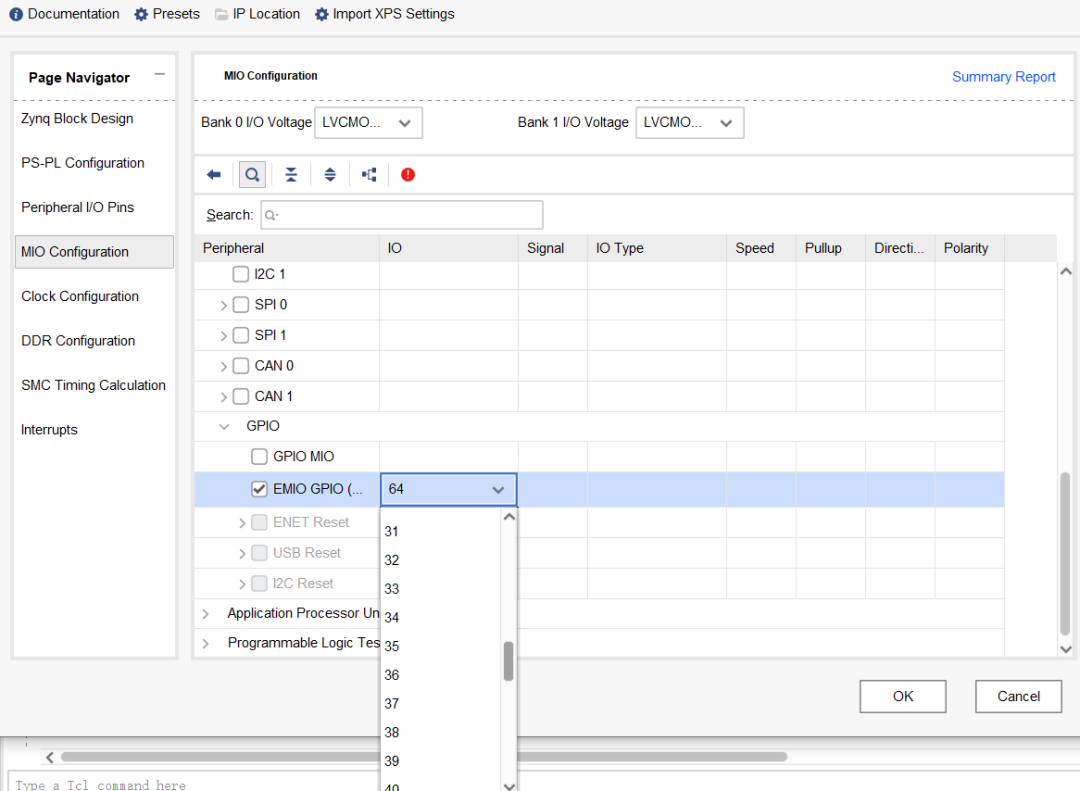

如上所述,有时没有足够的 MIO 引脚来显示希望拥有的所有接口。在这种情况下,可以将 MIO 扩展到 Zynq SoC 的可编程逻辑 (PL) 端。这称为扩展多用途 IO 或 EMIO(Extended Multipurpose IO )。EMIO 可以提供多达 64 个额外的 GPIO 引脚。或者,可以将大多数 MIO 接口分配给 EMIO,但 USB、SRAM/NOR 存储器接口和 NAND 闪存接口除外。Zynq SoC 技术参考手册提供了有关 MIO 和 EMIO 功能差异的非常详细的信息。为 EMIO 分配功能非常简单,只需单击 Peripheral I/O Pins 选项卡末尾的 EMIO 按钮即可完成,如下所示:

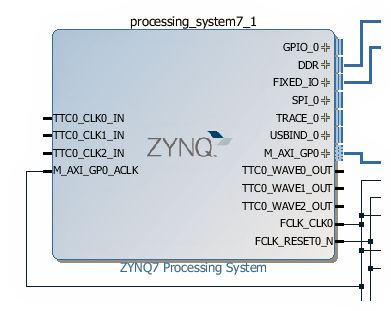

可以启用 GPIO 设置并从 MIO 配置选项选项卡中选择其大小。如果选择了最大 64 位大小,则 GPIO 将分为两组,每组 32 位。当关闭 re-customize IP 选项时,将看到您选择的附加端口已添加到框图中的 PS:上面的示例显示了当 GPIO_0、SPI_0 TRACE_0 和 TTC_0 分配给 EMIO 时的 PS。然后可以将这些功能分配为外部 IO,并将出现在重新生成的 HDL 网表中。注意:因为 EMIO 位于 Zynq SoC 的 PL 侧,所以不要忘记启用 PS 和 PL 之间的电平转换器以确保正确操作。

原文标题:ZYNQ从放弃到入门(一)MIO

文章出处:【微信公众号:OpenFPGA】欢迎添加关注!文章转载请注明出处。

-

Zynq Book来袭!!!!!!2014-09-04 0

-

Zynq-7000 SoC提供 FPGA 资源2018-08-31 0

-

RTOS怎么添加到ZYNQ SoC设计中?2019-10-23 0

-

为什么人们使用Zynq SoC而不是其他类型的FPGA?2020-04-01 0

-

典型的ZYNQ SoC结构图/系统框架2021-01-15 0

-

Xilinx Zynq-7000SOC的相关资料推荐2022-01-03 0

-

Xilinx客户分享Zynq SoC设计成功经验2017-02-09 233

-

将Zynq SoC上的两个ARM Cortex2017-02-11 2290

-

一个典型的Zynq SoC开发流程2018-05-01 15092

-

Zynq-7000 AP SoC 在多种应用领域中的演示2018-06-04 4533

-

Zynq SoC 给赛灵思带来的收益2019-07-24 2024

-

ARM TrustZone技术对Zynq SoC的作用2019-08-01 3186

-

zynq-7000 SoC产品选型指南2020-12-09 1017

-

Zynq-7000 SoC数据手册下载2021-05-21 1306

-

如何在Zynq SoC上开始使用FreeRTOS2023-10-18 582

全部0条评论

快来发表一下你的评论吧 !