什么是PA的“记忆效应”?

描述

在5G PA设计和应用中,有一个名词经常被大家提及:记忆效应(Memory Effect)。

PA怎么还会有“记忆”?记忆效应有什么影响,又要怎么规避?

带着以上问题,本文对PA的“记忆效应”做一个讨论

PA的“记忆效应”

什么是PA的“记忆效应”?

记忆效应是指器件的特性随时间变化而发生变化的现象。器件特性随时间变化,当前时间的特性受上一时间状态的影响,就好像器件带有“记忆”一样,所以这种特性被称作“记忆效应”。

对于PA电路来说,记忆效应反应出来的现象是:在同样的输入功率下,PA的增益、延时等特性在不同时刻表现不同。

PA一旦表现出强的记忆效应,线性度将会受到明显影响,出现宽带线性度恶化、左右ACLR不平现象,还会影响预失真(DPD或APD,数字预失真或模拟预失真)电路的工作 [1]。在PA设计和使用中,记忆效应需要尽量规避。

PA记忆效应的识别

方法一:观测AM/AM、AM/PM

在PA输入端加入输入信号,观察PA的输出信号,将此时放大器的增益、相位与输入信号逐点一一对应起来,就得到不同功率下的AM/AM、AM/PM特性曲线。观测AM/AM、AM/PM是识别记忆效应的最主要方法。

未发生记忆效应时,AM/AM、AM/PM曲线为一条平滑曲线,代表同样输入功率时不同时刻PA的特性保持相同。发生记忆效应时,曲线表现出一组发散分布的点,点的分散的离散与否代表了记忆效应的强弱。如果AM/AM、AM/PM曲线表现分散,表示对于一个同样的输入功率,PA有不同的增益、相位变化。PA的状态不止以此时刻的输入有关,还与其他时刻的状态有关,即PA表现出了“记忆效应”。

图:带有记忆效应的PA特性

方法二:宽带ACLR的恶化或不对称

另外一个识别记忆效应的方法是观察ACLR随信号带宽的变化。如果观察到信号带宽变宽时ACLR出现快速恶化,或者开始出现明显的左右不对称时,很有可能是发生了记忆效应[2]。

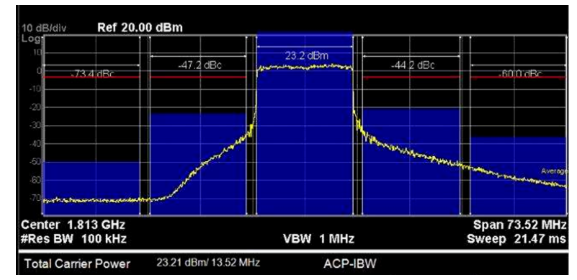

图:典型的PA左右ACLR不对称现象

ACLR不对称的产生也对测试造成较大困扰,当左右ACLR差别较大时,数据的准确记录都成问题。当发生严重左右不对称现象时,需要停下来检查PA是否发生了记忆效应。

方法三:宽带双音信号IMD3恶化或不对称

与观测宽带ACLR是否恶化方法类似,还可以采用观察宽带双音信号(Two tone)的IMD3是否出现记忆效应。

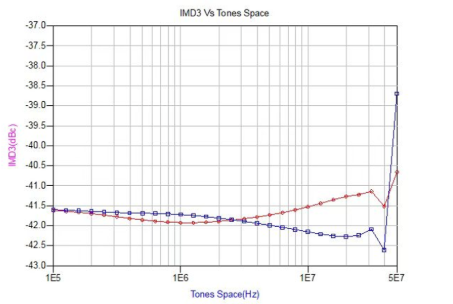

采用双音对PA进行激励,并将双音信号的间距逐渐由小变大,测试双音信号的IMD3。如果随着双音信号的间隔变大,IMD3出现恶化或左右不对称,则代表PA开始出现记忆效应。如下图所示测试,当信号间隔大于10MHz时,PA记忆效应开始显现。

图:采用双音测试法识别PA记忆效应

PA记忆效应的产生与规避

在对PA记忆效应的分析中,一般认为是输入信号中随时间变化的包络引起了PA特性的变化,造成PA不同时间的响应不同。为何输入信号会有包络呢?包络又是如何进一步引起PA特性变化?

4G/5G信号的包络

4G/5G系统中所使用的调制方式是OFDM(Orthogonal Frequency Division Modulation,正交频分复用)调制,OFDM是一种特殊的FDM(Frequency Division Multiplex,频分复用)调制方式。

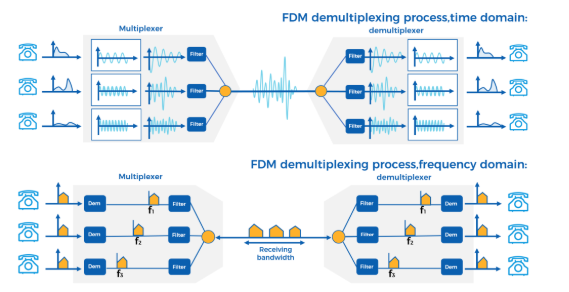

FDM是无线通信中的重要复用技术,是指将传输信号调制到不同频率的多载波上,再进行空间传输。与单一频率的单载波信号相比,FDM可以有效增加带宽,提升传输速率,并且可以增强信号抗干扰能力,在无线通信系统中得到广泛应用。下图为FDM系统的典型实现框图。

图:频分系统的时域及频域图示

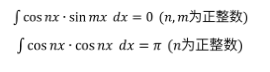

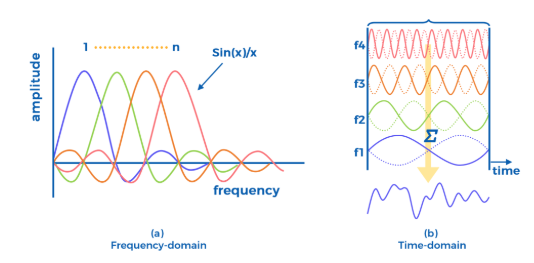

OFDM本质也是一种FDM技术,也是利用频分的方式进行信号的空间复用传输。只不过在信号的正交上,并不只是采用如传统FDM相同的频分技术,还利用到了一些信号在正交上的特性,OFDM利用到的信号正交特性可由如下积分公示表示,当积分区间为0~2π时:

如果将cos nx看成一路信号,sin mx或cos nx看成另外一路信号,可以看到相同的信号相乘后积分为π,不同信号相乘后积分为0。所以对于混在一起的不同信号,我们只需要用指定信号和其相乘积分,就可以将有用信号提取出来,实现信号的正交。这就是正交频分复用的原理。

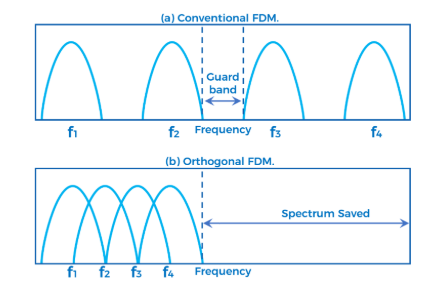

利用这一特性,OFDM中并不需要像传统FDM一样保留较宽的保护带,而是可以将频率成倍数关系的子载波叠加在一起,就可以完成频分复用,大大提高了频谱利用效率。FDM和OFDM的频域关系如下图所示:

图:FDM与OFDM的频谱特性 [6]

在信号传输时,频域上多个子载波频分复用进行信号传输,时域上这些信号幅度相叠加。如果某一时间点几个子载波的振幅均为高位,则叠加出现峰值功率,OFMD信号的峰均比:PAPR(Peakto Average Power Ratio)就此出现。

图:OFDM信号的时域叠加:

形成高峰均比(非恒定幅值)信号

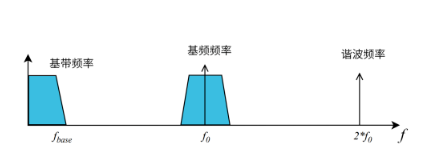

以上OFDM信号的产生均在基频处发生,为了将信号在空间传输,需要将信号调制到射频频率。一般在无线通信系统中,将携带信息的OFDM信号称为基带信号,所对应的频率也称作基带频率。由于射频信号的调制和放大经常伴有谐波发生,为了把射频的信号做区分,一般将所用来做射频调制的频率称为基频频率,将信号的谐波称为二次、三次谐波频率。

图:基带频率、基频频率与谐波

(二次谐波为代表)频率之间的关系

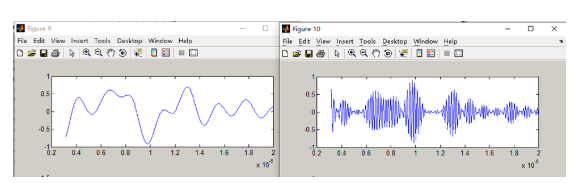

经过射频调制的OFDM信号波形如下图所示。

图:OFDM基带包络信号的形成(左)

及射频基频信号正交调制后的波形(右)

由上图(右)可以看到,OFDM基带信号被射频频率调制成包络与原始OFDM信号相同、载波频率与射频基频信号相同的射频信号。

以上信号将进入功率放大器放大输出,即进入功率放大器的信号并不是恒包络信号,而是包络跟随OFDM信号变化、带有峰均比的信号。这就是4G/5G中射频信号包络产生的过程。

PA记忆效应的来源

在4G/5G 通信系统中所使用的是非恒定包络的OFDM信号,如果PA特性随信号包络在变化,则会发生记忆效应。

在PA记忆效应的分析中,一般将包络信号对PA的影响分为三类 [3],分别是:

电记忆效应;

电热记忆效应;

半导体器件陷波效应(Semiconductor Trapping Effects)。

电热记忆效应和半导体器件的陷波效应

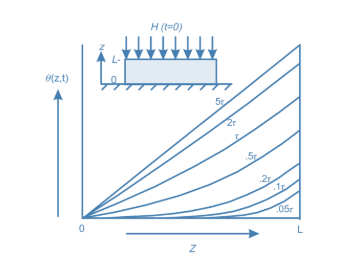

PA是高耗电器件,同时PA特性对温度敏感。对于PA器件而言,热扩散与时间相关。下图为对PA芯片进行一维等效,在芯片表面加热源后,芯片各部分位置温度随时间变化图。可以看到,随着时间的不同,芯片各位置的温度发生变化[3]。

图:PA晶体管芯片温度分析的一维等效

如果PA的输入信号带有包络,不同包络信号的幅度将会引起PA温度的变化,进而引起PA特性的不同,使PA产生记忆效应。通常情况下,电热记忆效应只与低于1MHz的包络频率有关,因此,通常把电热记忆效应认为是长时记忆效应。

针对于电热记忆效应,需要对PA进行良好的散热设计,确保PA产生的热量可以良好扩散。

半导体的陷波效应(Semiconductor Trapping Effects)是指在半导体器件中表现出来的记忆效应,此种记忆效应与半导体制造工艺相关。对于半导体陷波记忆效应,设计上可尝试的方法并不多,需要代工厂在器件上做优化和保障。设计中可以采用较为成熟的半导体工艺,确保器件侧无记忆效应问题。

电热记忆效应

电记忆效应是PA电路记忆效应的主要来源。

在PA设计中,PA能量的来源是直流供电。直流供电需要通过偏置电路加在器件的输出(集电极或漏极)及输入(基极或栅极),这些偏置电路需要完成供电功能,并且不能影响到射频信号传输。

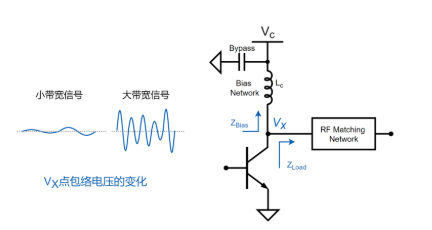

理想情况下,偏置电路需要对射频信号表现出高阻(射频信号才不会进入到偏置电路中),同时对其他频率保持低阻(防止其他频率出现交流电压摆幅)。对于射频信号的包络频率来说,由于其与射频载波信号的二阶交调(IMD2)刚好会落在信号的旁带,所以射频信号包络频率的阻抗控制尤其重要。如果处理不好,偏置电路将会发生包络调制,引起ACLR恶化。

图:简单PA偏置网络示意图

以上图所示简单偏置电路来理解包络信号对PA偏置的调制作用。图示为简单共射极放大电路,放大器集电极通过串联电感连接至直流供电电源,Bypass电容提供射频接地,电感LC提供高的射频阻抗。

如果假设PA工作射频频率为2.6GHz,电感LC的感值为3nH,供电电压为3.4V,电流为500mA。则电感LC可提供的射频阻抗为ZBias@2.6GHz=163Ω,由于此点的射频负载阻抗ZLoad@2.6GHz≈3.5Ω,在2.6GHz射频工作频率,ZBias远大于ZLoad,偏置网络可以提供较高的射频阻抗,使射频信号不进入偏置网络内。

如果此2.6GHz信号带有10MHz信号带宽,位于基带频率的10MHz的包络信号在经过LC产生的压降为0.1V左右,晶体管接收到的将不是一个稳定的3.4V供电电压,而是一个受包络调制,摆幅0.1V的变化电压。如果晶体管特性在0.1V供电电压波动时不产生变化,输出信号将看不到记忆效应。

如果这时将输入信号带宽提高到100MHz,则LC产生的包络频率压降将提升至1V左右,这将对一个3.4V供电的电源带来明显影响,如果晶体管特性在1V的变化下发生明显变化,记忆效应将显现。所以,随着信号带宽的增加,偏置网络引起的记忆效应现象将更加明显。这也是为什么5G相比4G记忆效应问题更加突显的原因。

以上是以输出偏置网络为例对电记忆效应其中一个成因的简单描述。在PA设计中,PA输入偏置网络、阻抗匹配网络的记忆效应均需要在设计中加以考虑。

对包络信号引起IMD3变化的定量分析如下。

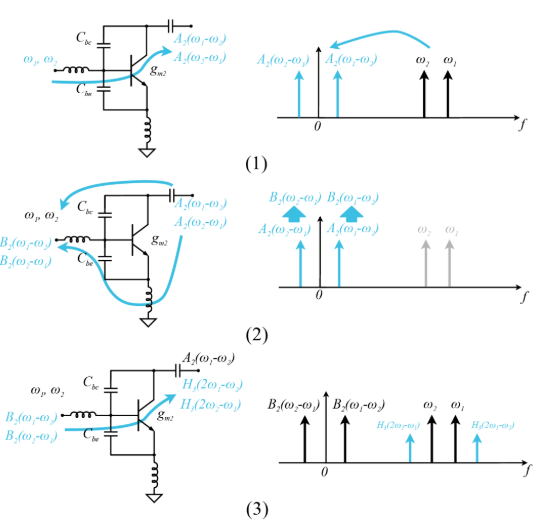

输入放大器带有一定带宽的OFMD信号调制信号可以简化为一组双音信号,频率分别为ω1,ω2,在只考虑HBT器件非线性跨导时gm2,IMD3信号产生过程如下:

输入端双音信号通过HBT器件 的二阶非线性跨导gm2在输出端产生包络信号A2(ω1-ω2)、A2(ω2-ω1);

输出端包络信号通过寄生电容和源极电感等反馈通路反馈到输入端,经过反馈通路后到输入端包络信号为B2(ω1-ω2)、B2(ω2-ω1);

输入端的包络信号和输入端的基频信号ω1再次通过HBT的二阶非线性跨导gm2产生二阶交调,在输出端产生IMD3信号H3(ω1-ω2)、H3(ω2-ω1)、,造成线性度的恶化;

图:宽带信号激励下,由于器件非线性引起IMD3的过程

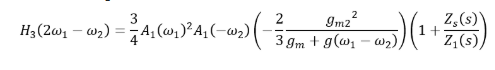

以上为宽带信号IMD3产生及影响线性度恶化的过程,通过Volterra级数推导,由二次跨导非线性gm2和包络信号产生的IMD3为:

通过以上公式也可以计算得到左侧IMD3 H3(ω1-ω2)、H3(ω2-ω1)的表达式。需要说明的是,由于A2(ω1-ω2)及A2(ω2-ω1)位于零频两侧,二者阻抗不同,会导致第三步左右IMD3混频结果不对称,这也是左右ACLR不对称的来源。

当信号带宽变大时,即ω1与ω2频率相差变大。如果不加以控制,A2(ω1-ω2)与A2(ω2-ω1)之间的阻抗差别也会变大,造成宽带信号ACLR变差,这是宽带信号记忆效应表现更明显的原因。

可以看到,IMD3信号的大小与器件的线性与非线性跨导相关,同时与源端、负载端等阻抗相关。以上公式可以用来设计和控制包络信号产生IMD3分量的大小。

电热记忆效应的规避

电记忆效应的来源是由于在PA设计中,谐波及包络频率阻抗过大引起,在设计中,要注意对这些阻抗加以处理,将包络频率与谐波频率的阻抗尽量归零。

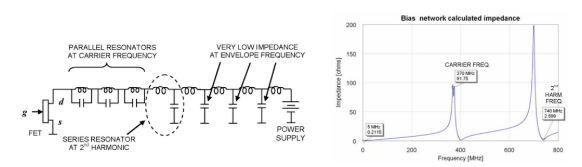

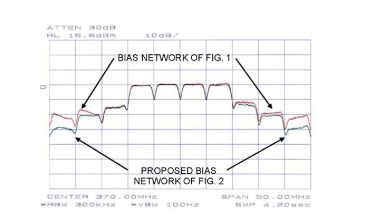

文章 [4]中提出了一种供电电路设计,此电路可以对基频信号提供较高的阻抗(91.75Ω),同时使包络信号及谐波信号保持较低的阻抗(0.2Ω及2.6Ω)。采用此偏置网络,PA线性度和ACLR恶化现象明显改善。

图:文章 [4]所提出偏置网络及其阻抗特性

图:文章 [4]所提出偏置网络对线性度有明显改善

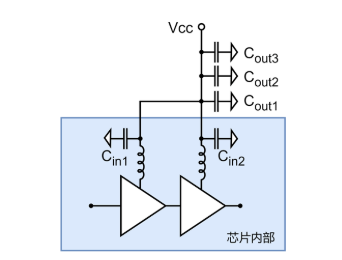

在PA芯片的手机应用中,由于偏置网络在芯片内部已经设计好,重新设计偏置网络不是一个可行的选项。但在应用中观测到记忆效应时,还是需要对板级Bypass电容进行良好设计。

一般在PA芯片内部,Bypass电容为100pF量级(在2.6GHz阻抗为0.6Ω的低阻),起到对射频信号旁路功能。但100pF电容在100MHz处的阻抗为16Ω左右,无法为基带频率及包络频率提供低阻,所以,一定要在板级放置100nF量级Bypass电容,为包络信号提供近似理想接地,降低电源引起的记忆效应。

图:典型PA芯片的Bypass电容放置

器件的非线性引起的记忆效应需要借助对器件的非线性分析进行消除,常用分析方法是Volterra级数法等。通过对放大器偏置点、阻抗及非线性的控制,可以使器件非线性引起的记忆效应加以改善 [7]。

总 结

PA记忆效应是较为抽象的概念,反应PA特性随时间的变化而变化,造成输出信号的失真。

PA记忆效应是由包络信号的幅度变化引起,OFDM调制带来的信号峰均比经过射频调制后,形成包络变化的射频信号。如果PA特性随包络变化而变化,则将发生记忆效应。

电记忆效应是PA记忆效应最主要的来源,通过优化偏置电路、节点阻抗可以有效地改善电记忆效应。在应用中,需要注意偏置电路中的Bypass电容设计,一定要在包络频率提供较低阻抗,确保包络信号在偏置电路中不被调制起来。

在5G PA设计中,慧智微利用可重构技术架构,可以对功率放大器各频点阻抗进行调谐控制,有效解决5G PA的记忆效应问题,使5G PA大带宽线性度明显改善。

-

功率放大器居然有记忆效应?2021-12-30 1155

-

功放记忆效应是什么?如何降低功放记忆效应?2021-04-07 0

-

电池的认识记忆效应2008-09-07 581

-

什么是电池记忆效应?怎样消除?2009-10-24 4802

-

什么是电池记忆效应?2009-11-03 4261

-

镍镉电池记忆效应2009-11-05 4774

-

什么是记忆效应(笔记本每日一贴)2010-01-21 1362

-

电池的记忆效应2010-09-06 1011

-

电池的记忆效应是什么_铅酸电池有记忆效应吗2017-12-22 30846

-

消除镍镉电池记忆效应的电路2019-02-08 5206

-

镍镉电池记忆效应原因及消除2019-12-03 8275

-

电池记忆效应原理_电池记忆效应怎么解决2020-08-03 9364

-

PA怎么还会有“记忆”?记忆效应有什么影响2022-04-13 1861

-

5G PA设计和应用中的“记忆效应”2022-04-15 4716

-

5G PA怎么还会有“记忆效应”?2023-07-04 637

全部0条评论

快来发表一下你的评论吧 !