DDR仿真需要提取到多少频率?

描述

DDR仿真作为一个非常普遍的仿真模块,基本上入门SI行业的人都会首先接触到。记得本人刚接触这个行业的时候,也是先接触DDR模块的仿真。从DDR2到DDR4,可能很多同行都一直使用同一套的仿真方法,就是先提取无源链路(RLC链路或者S参数),再加入有源的模型(例如IBIS模型),然后码型跑起来,芯片驱动接收配置调起来就能看到扫描的结果。

有源的模型这个没什么好说的,就摆在这里,我们也只能管管模型对不对。那我们说说提取链路的无源参数吧。我们以DDR4的数据信号(2400Mbps)为例来说明。我们看到2400Mbps,大家都知道该速率对于的最高码型的频率为1200MHz,也就是我们所说的基频。那我们在提取链路的S参数时,是不是只需要提取到1200MHz就好了呢?

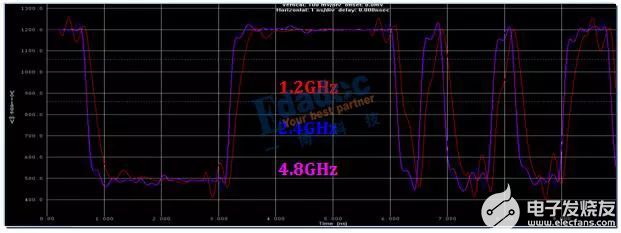

我们首先来看看提取到下面三个频率后加入有源模型的波形差异。

信号波形如下所示:

可以看到提取到不同的频率对波形的差别很大,尤其在1.2GHz和2.4GHz的差别,几乎上升/下降沿都对不上,而2.4GHz和4.8GHz时在稳定电平上的波形也有不小的差异。

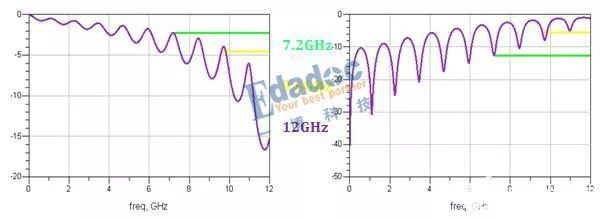

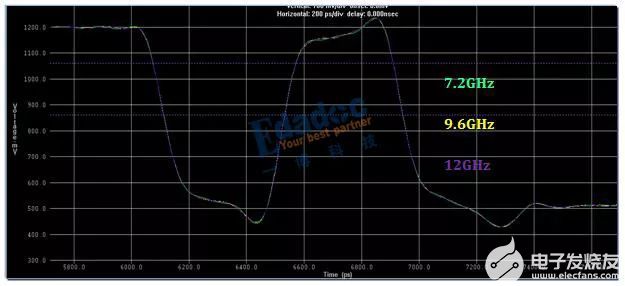

那我们再提取更高的频率看看,如下:

然后我们再来看看波形结果,可以看到在这几个频率下,无论是沿还是稳定电平的振荡情况都比较接近,区别不大了。

看来我们提取无源参数的时候还真不能只按照基频来提取。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

Altera DDR2仿真2016-06-29 0

-

DDR仿真的频率提取2019-07-24 0

-

什么情况下才需要DDR信号仿真分析?2021-03-17 0

-

用Cadence Sigrity仿真DDR模组,怎么提取出.ckt的MCP头文件2021-05-27 0

-

Cadence软件提取和建立拓朴进行仿真2010-04-05 532

-

基于Cadence的DDRⅡ仿真设计2012-02-13 497

-

分析提取S参数需要注意的细节 保证仿真可以准确的获取到通道的性能2018-01-16 16588

-

DDR串扰仿真的使用指导书详细概述2020-04-14 729

-

以DDR内存条为例教你进行SI仿真2023-02-07 1056

-

DDR仿真需要提取多少频率 不同的频率对波形有何差别2021-03-31 2537

-

如何利用ADS仿真软件辅助进行DDR的电路仿真?2021-05-17 10454

-

DDR设计和仿真技术详解2022-10-24 349

-

一文了解内存DDR的频率2023-01-05 11469

-

calibre后仿真参数提取2024-01-04 458

全部0条评论

快来发表一下你的评论吧 !