如何使用SPI总线设计正交编码器计数器

描述

本应用笔记描述了一个SLG46140V设计,该设计实现了一个带有正交编码器输入的16位加/减计数器。GreenPAK设备减轻了主机的实时输入要求,并允许轻松连接多个编码器。

旋转编码器广泛用于感测轴和机器零件的方向,以及作为用户界面输入设备。大多数旋转编码器输出一对正交信号,将轴运动编码为一系列脉冲。

为了跟踪编码器位置,必须对每个脉冲进行计数。通常,中断引脚用于此目的,计数在软件中实现。许多微控制器包括专门的外设来读取正交信号。然而,基于中断的计数限制了最大脉冲速率并占用了CPU时间,而专用外设限制了可连接到单个微控制器的编码器数量。此外,在非实时平台(例如PC)上,这两个选项都不可用。

本应用笔记演示了SLG46140VGreenPAK器件如何实现具有16位向上/向下计数器和SPI总线接口的正交编码器接口。主机应用程序可以按所需的时间间隔读取编码器的当前位置,而辅助设备会跟踪每个输入脉冲。此外,SPI总线允许链接多个设备以将灵活数量的编码器连接到单个处理器。

高级设计

本应用笔记设计具有来自编码器的三个输入信号:A、B和Z。信号A和B是正交信号,它们以00、10、11、01格雷码序列交替切换状态。信号Z是一个可选的编码器零索引输入,它将计数器复位到零位置。

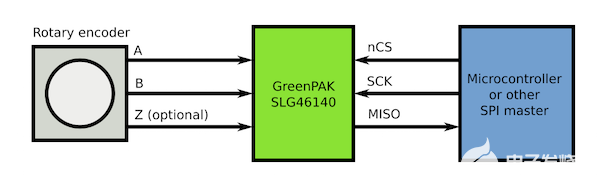

图1.一个编码器设备的系统连接。

所描述的SPI由nCS片选信号、SCK串行时钟和MISO(主机输入,从机输出)串行输出组成。片选低电平有效,当nCS为高电平时,总线可以被其他SPI设备使用。本应用笔记中使用的SPI传输格式为CPOL=0,CPHA=1,这意味着SCK在空闲时处于低电平状态,并且在下降沿采样数据。

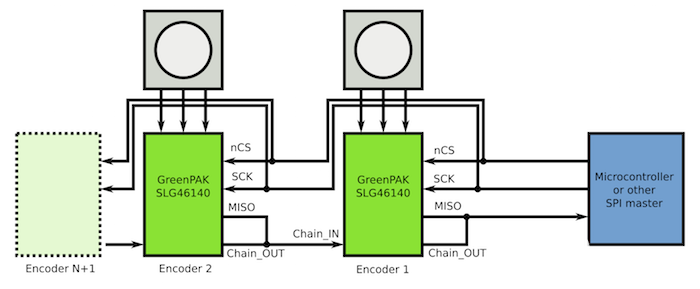

图2.具有多个编码器的系统连接。

使用Chain_IN和Chain_OUT信号可以将多个设备链接在同一总线上,这些信号在内部延迟16个SCK时钟周期的数据。因此,主机接收的前16位将来自第一个编码器,接下来的16位来自第二个编码器,依此类推。所有编码器将在第一个SCK时钟沿同时进行采样。

GreenPAK设备内部的实现由三部分组成:

正交编码器输入模块:将正交信号转换为计数器的KEEP/UP信号对,并将信号与内部时钟同步。

16位向上/向下计数器:两个链接的8位计数器对编码器脉冲进行计数并向SPI模块提供并行数据。

SPI总线:SPI锁存并行数据,并在nCS有效时串行输出。

正交输入模块和计数器由内部环形振荡器时钟运行,而SPI由SPI主控从外部提供时钟。以下部分包含每个组件的详细说明。

正交编码器输入模块

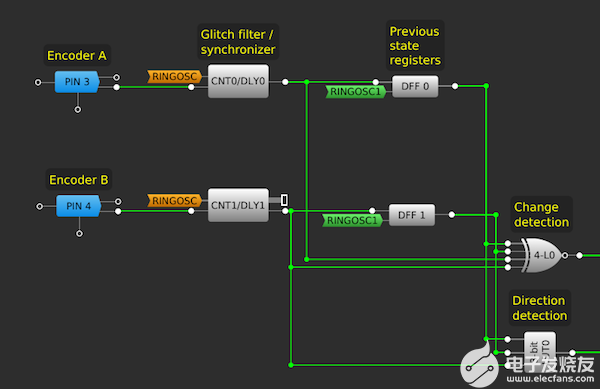

来自编码器的信号最初进入一对延迟块。它们既可用作毛刺滤波器又可用作同步器,确保其输出信号仅在时钟上升沿发生变化。延迟值设置为最小值,给出2个时钟周期的延迟。可选地,对于噪声信号,可以增加延迟以滤除来自输入的任何毛刺脉冲,但这种过滤也会限制最大脉冲速率。

延迟块的输出被传递到一对D触发器,它们保留前一个时钟周期的信号状态。然后将当前状态和先前状态与4输入XNOR门进行比较。如果任一信号发生变化,XNOR门将为KEEP信号输出0值,使计数器模块开始计数。

图3.正交信号输入模块

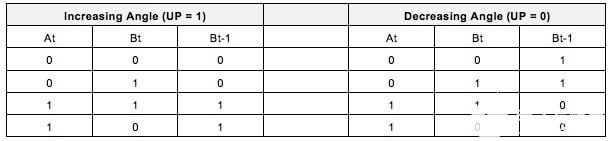

通过比较当前状态At和Bt与先前状态Bt-1来检测编码器方向,如表1所示。检测逻辑已编程到3位LUT0组件,该组件向计数器输出UP信号。

表1.信号状态的方向检测

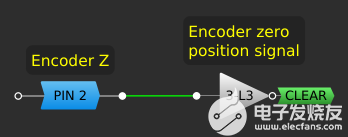

一些编码器有一个额外的零位传感器,可用于在重新启动后找到系统的绝对位置。此Z信号上的高电平会将计数器重置为零。如果不需要此功能,可以不连接信号,因为输入引脚已配置下拉电阻。

16位加/减计数器

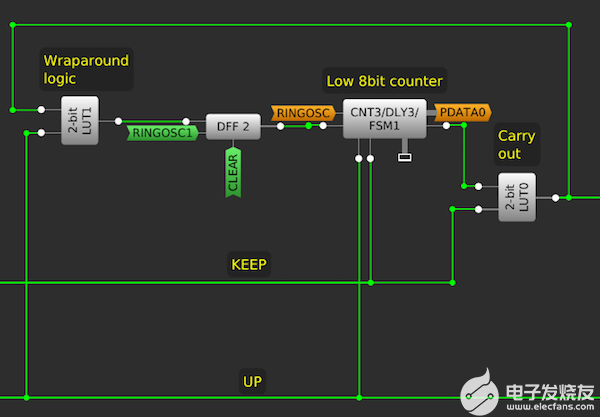

SLG46140V器件包含两个计数器/有限状态机模块,具有与SPI模块的并行数据连接。它们中的每一个都可以输出一个8位的计数,并且通过链接两个计数器可以制成一个16位的计数器。计数器在任一方向从0x0000环绕到0xFFFF。

图4.Z输入信号的逻辑

默认情况下,CNT3块从可配置的起始值向下计数到0或向上到255,然后以配置的值重新启动。通过将起始值设置为255可以实现向下计数的回绕,但要同时获得向上计数的回绕,则需要额外的逻辑。

图5.低8位计数器的执行和环绕逻辑

当计数器处于其极值时,计数器的OUT信号激活。当KEEP=0和OUT=1时,LUT0输出一个进位脉冲到下一个计数器以增加它的计数。同时,如果UP=1,LUT1将激活复位信号。DFF2对复位信号进行采样,以便计数器在时钟上升沿同步复位。

来自编码器Z输入的CLEAR信号连接到DFF2的异步置位输入,这会导致计数器立即复位。计数器在下一个时钟上升沿继续计数。

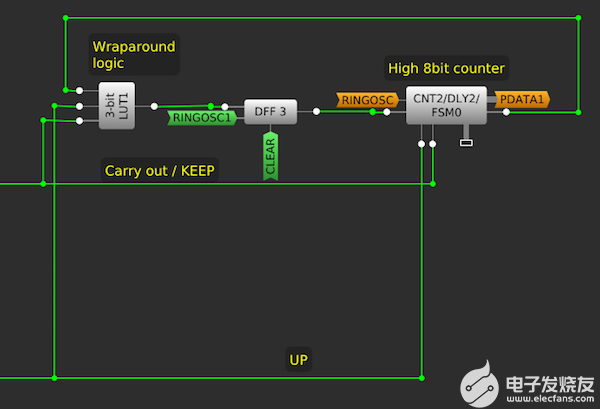

图6.高8位计数器的环绕逻辑

第二个计数器级的连接方式类似,因为该级不需要单独的进位信号。这三个信号都连接到一个LUT组件。当UP=1、KEEP=0和OUT=1时,它将计数器重置为零。

SPI总线

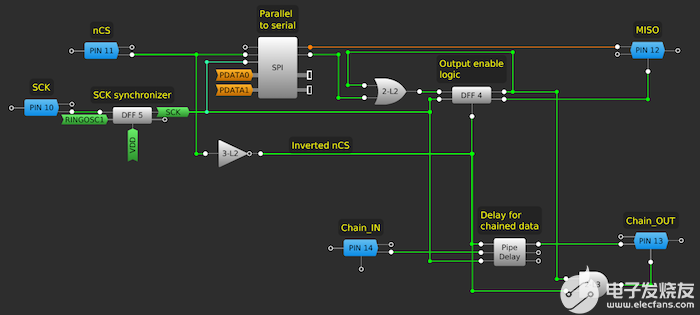

SLG46140和SLG46620中的并串转换器接口作为现成的功能块提供。在nCS变低后,该块在第一个SCK边沿锁存来自两个计数器的并行数据,然后逐位移出数据。

外部产生的SCK信号与计数器使用的内部时钟不同步,因此两个模块需要以某种方式同步,以便在它们之间可靠地传输数据。SPI模块提供了一个内置选择,用于在发生数据传输时将FSM时钟门控两个时钟周期。在此应用中,不希望对FSM时钟进行门控,因为它可能会在时钟被禁用时导致脉冲丢失。相反,DFF5用于将外部SCK信号与内部环形振荡器时钟同步。这确保了当FSM数据稳定时,SPI模块看到的SCK时钟沿发生在环形振荡器时钟沿。

在本应用笔记中,基本SPI通过数据链接逻辑进行了扩展。这允许在同一SPI总线上轻松连接多个编码器,并同时对它们的计数器值进行采样。

链接功能基于管道延迟功能块。这个块有一个由16个触发器组成的链,它们将在时钟信号的每个上升沿移入和移出一位。来自链中前一个设备的MISO信号连接到输入,输出到下一个设备。

由于MISO信号直接连接到硬件的12号引脚,Chain_OUT必须在外部与其并联。输出使能逻辑确保一次只有一个引脚处于活动状态。

图7.SPI和数据链逻辑

对于前16个时钟周期,在nCS变为低电平后,每个设备保持MISO启用并输出其计数器值。同时,管道延迟模块存储从链中第N-1个设备接收到的信号。

16个时钟周期后,SPIINTR输出变为高电平以指示传输结束。LUT2或门然后使DFF4触发器变高,禁用PIN12并启用PIN13。PipeDelay模块移出第N-1个值,同时移入第N-2个值。这一直持续到所有值都被读取并且主机产生一个nCS信号,这将DFF4重置回其初始状态。

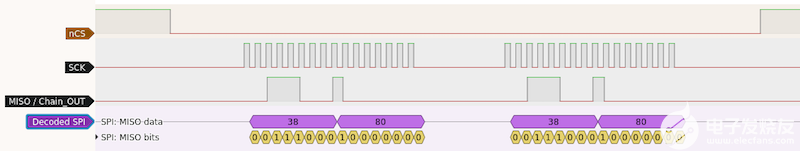

图8.使用两个设备捕获SPI信号

图8显示了一个SPI通信示例,其中设备首先发送自己的16位数据值,然后从链中的下一个设备转发16位值。

时钟速率限制

延迟和计数器模块由内部环形振荡器提供时钟,该振荡器以大约27MHz的频率运行,具有1、4、8或16的可选分频器。最大时钟速率取决于逻辑元件的延迟,并随电源电压。

设计中最长的逻辑链从输入DLY0/1块通过4位LUT0变化检测器、2位LUT0执行逻辑和3位LUT1环绕逻辑到FSM块。这些模块的延迟值在SLG46140数据表中定义,并在表2中进行了总结。由于布线延迟和部件差异,理论上可能的6.8MHz频率不适用于GreenPAK输入电压范围的最低端(VDD=1.8V),而使用3.4MHz时钟。

表2.模块延迟和最大工作频率

工作频率将限制正交输入的最小脉冲宽度。输入毛刺滤波器通过至少三个时钟周期长的脉冲并过滤掉任何低于两个时钟周期的脉冲。

测试结果

以两种方式测试功能。使用AMT203旋转编码器的正交输出进行手动测试,以验证两个方向的计数是否按预期工作并跟随编码器运动。

使用模拟正交信号的微控制器生成的信号源验证了最大脉冲率和计数可靠性。微控制器被配置为以给定的步进频率输出8000步。正交信号中的脉冲宽度是步距的两倍,因为一次只有一个信号改变状态。当通过SPI总线读取数据时,该步骤系列重复了几次。仅当每次都正确计算所有步骤时,才将测试用例标记为成功。

表3总结了测试结果。正如预期的那样,短于两个时钟周期的脉冲会被毛刺滤波器拒绝并导致计数为零。当在每个电压下接近最小脉冲宽度工作时,会有一些丢失的步骤。这可能是由不对称的上升/下降延迟引起的,这可能会在某些脉冲通过逻辑时稍微缩短一些脉冲。

结论

介绍了一种将正交编码器连接到SPI总线的设计。该设计可以按原样使用,也可以将各个组件重新用于不同的应用。正交输入部分可以修改为直接输出适合不同设备的信号,例如步进驱动器。16位加/减计数器模块为测量多种脉冲源提供了有用的工具。可链接的SPI可用于同时从多个GreenPAK设备进行采样和读取,数据源可以来自计数器或ADC。

-

请问有没有计数器输出的计数值是串行数据(最好是SCI总线2012-02-07 0

-

正交编码器接口2013-06-04 0

-

基于dsPIC单片机的正交计数器设计 求大神给思路2014-03-26 0

-

stm32正交编码器2014-03-26 0

-

【数据采集分享】怎样将正交编码器和数据采集卡配合使用2014-12-05 0

-

MM32 TIM编码器模式2018-02-08 0

-

转动编码器时计数器的增量太快2019-03-13 0

-

LS7366R 32 位正交编码脉冲计数器模块2019-04-17 0

-

【案例分享】STM32正交编码器驱动电机2019-07-20 0

-

正交编码器原理码盘2021-08-12 0

-

STM32正交编码器怎么进行测速?2021-11-16 0

-

正交编码器原理什么是正交?2022-01-10 0

-

正交编码器测速的方法2022-01-10 0

-

基于VHDL的正交编码脉冲电路解码计数器设计2010-03-01 1116

-

1路编码器脉冲计数器或2路DI高速计数器,Modbus RTU模块 YL1502022-11-03 505

全部0条评论

快来发表一下你的评论吧 !