拉电流和灌电流电路原理以及构成

拉电流和灌电流电路原理以及构成

描述

相信拉电流和灌电流这两个名词我们听了很多,源电流和灌电流一般在集成电路中使用,例如MCU、数字信号控制器、数字信号处理器等,今天我们就详细说说拉电流和灌电流电路原理以及构成。

1.拉电流

所谓拉电流就是提供给外部电路的电流能力,目前最新的MCU和DSP的输出引脚一般具有 4mA 至 16mA 的输出电流能力,在某些集成IC中,输出电流能力是可配置的,可以根据需要设置 4mA、9mA 等拉电流。

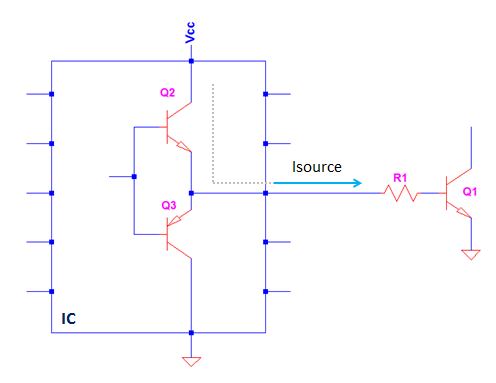

下图显示了拉电流的方向,拉电流具有向外输出的方向。该电流通过内部电路流向电阻器R1和晶体管Q1等外部电路,两个晶体管Q2和Q3的公共基极加高电平时,PNP晶体管Q3将截止,只有NPN晶体管Q2饱和导通,电流将流出端口向外输出。

比较重要的是不要超过IC可以输出的最大电流,以免损坏IC端口。有些刚接触拉电流的新手可能会误认为拉电流是恒定电流源输出,认为拉电流是器件的唯一输出电流值,并且不能变化,假设指定的拉电流为 4mA,设备只会将电流钳制在这个水平,这是错误的理解,根据上图,Q2晶体管将饱和,然后电流将仅受电阻R1的值限制。因此,必须仔细选择 R1 的大小,以免超过规格书规定的拉电流,实际工作时拉电流计算如下:

由于Q2晶体管饱和,VCEsat 的值被忽略,公式将推导为:

为了提高设计的可靠性,Isource 的值必须小于规格书指定的拉电流,最好使最大输出电流应力不超过规定值的80%。

2.灌电流

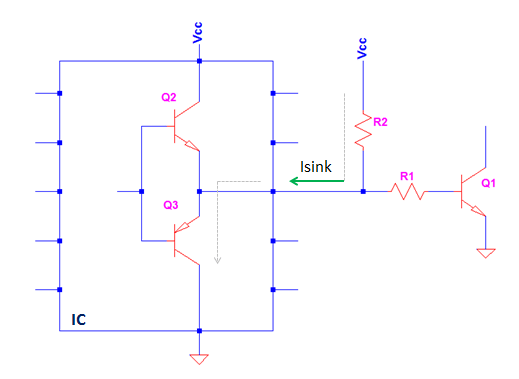

灌电流其实就是输入电流,下图展示了灌电流的方向。当 Q2 和 Q3 上施加的基极电压较低时,上部晶体管将截止,下部晶体管将饱和导通。PNP 晶体管Q3将饱和导通,电流 Isink 将从 Vcc 流向 R2,然后流向 IC 引脚。Isink 的计算值必须小于规格书中的规定值,以防止端口过流损坏。

忽略 VCEsat,公式变为:

同样为了提高设计的可靠性,最好使最大灌入电流应力不超过规定值的80%。

在上图中,IC 引脚的配置是漏极开路,这就是需要电阻 R2 的原因,如果引脚配置为推挽式,则不需要 R2。对于上图,当使用推挽时,灌电流不是问题,因为没有来自外部的电流路径,流过 PNP 晶体管的电流只是来自上 NPN 晶体管的漏电流。

审核编辑:汤梓红

-

什么是灌电流和拉电流,灌电流和拉电流的意思2009-10-21 0

-

什么是拉电流,什么是灌电流?什么是吸收电流 ?2011-11-07 0

-

什么是拉电流和灌电流?2014-03-05 0

-

拉电流与灌电流的含义和区别2018-09-06 0

-

拉电流与灌电流(双向通讯思考)2018-10-09 0

-

拉电流和灌电流是衡量电路输出驱动能力2019-03-30 0

-

拉电流和灌电流2019-06-03 0

-

拉电流和灌电流是什么意思?扇出系数是指什么?2021-04-07 0

-

电源电路小知识:带你了解拉电流与灌电流的区别2021-08-22 0

-

灌电流是什么?拉电流又是什么2021-09-28 0

-

浅析门电路与拉电流和灌电流2021-10-08 0

-

拉电流和灌电流是什么意思2021-10-08 0

-

拉电流和灌电流与驱动电路有何关系2021-10-09 0

-

拉电流和灌电流的相关资料分享2021-11-24 0

-

拉电流和灌电流是如何去定义的2021-12-01 0

全部0条评论

快来发表一下你的评论吧 !